0% found this document useful (0 votes)

183 views2 pagesDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)

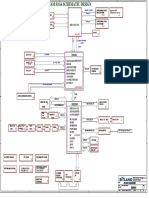

This document summarizes the design of a two-stage CMOS operational amplifier that operates at ±1.8V power supply. It introduces the design procedure, which involves meeting specifications for gain, slew rate, common-mode rejection ratio, gain bandwidth product, and phase margin. It describes the challenges of designing op-amps at reduced supply voltages and transistor sizes. Simulation results are planned to validate the design meets specifications and analyze differential and common mode gain versus frequency and phase.

Uploaded by

Shahin ShahCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

183 views2 pagesDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)

This document summarizes the design of a two-stage CMOS operational amplifier that operates at ±1.8V power supply. It introduces the design procedure, which involves meeting specifications for gain, slew rate, common-mode rejection ratio, gain bandwidth product, and phase margin. It describes the challenges of designing op-amps at reduced supply voltages and transistor sizes. Simulation results are planned to validate the design meets specifications and analyze differential and common mode gain versus frequency and phase.

Uploaded by

Shahin ShahCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 2