Bit logic operations (S7-1200, S7-1500)

Bit logic operations

This chapter contains the following information:

---| |---: Normally open contact (S7-1200, S7-1500)

---| / |---: Normally closed contact (S7-1200, S7-1500)

--|NOT|--: Invert RLO (S7-1200, S7-1500)

---( )---: Assignment (S7-1200, S7-1500)

--( / )--: Negate assignment (S7-1200, S7-1500)

---( R )---: Reset output (S7-1200, S7-1500)

---( S )---: Set output (S7-1200, S7-1500)

SET_BF: Set bit field (S7-1200, S7-1500)

RESET_BF: Reset bit field (S7-1200, S7-1500)

SR: Set/reset flip-flop (S7-1200, S7-1500)

RS: Reset/set flip-flop (S7-1200, S7-1500)

--|P|--: Scan operand for positive signal edge (S7-1200, S7-1500)

--|N|--: Scan operand for negative signal edge (S7-1200, S7-1500)

--(P)--: Set operand on positive signal edge (S7-1200, S7-1500)

--(N)--: Set operand on negative signal edge (S7-1200, S7-1500)

P_TRIG: Scan RLO for positive signal edge (S7-1200, S7-1500)

N_TRIG: Scan RLO for negative signal edge (S7-1200, S7-1500)

R_TRIG: Set tag on positive signal edge (S7-1200, S7-1500)

F_TRIG: Set tag on negative signal edge (S7-1200, S7-1500)

---| |---: Normally open contact

Description

The activation of the normally open contact depends on the signal state of the associated operand. When

the operand has signal state "1", the normally open contact closes and the signal state at the output is set

to the signal state of the input.

When the operand has signal state "0", the normally open contact is not activated and the signal state at

the output of the instruction is reset to "0".

Two or more normally open contacts are linked bit-by-bit by AND when connected in series. With a series

connection, power flows when all contacts are closed.

The normally open contacts are linked by OR when connected in parallel. With a parallel connection, power

flows when one of the contacts is closed.

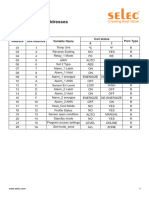

Parameter

The following table shows the parameters of the instruction:

Paramete

r

<Operand

>

Declaratio Data

type

n

S7-1200

Input

I, Q, M, D, L

BOOL

Memory area

S71500

I, Q, M, D, L, T, C

Description

Operand

whose

�Bit logic operations (S7-1200, S7-1500)

signal state is

queried.

Example

The following example shows how the instruction works:

The "TagOut" operand is set when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The operand "TagIn_3" has the signal state "1".

---| / |---: Normally closed contact

Description

The activation of the normally closed contact depends on the signal state of the associated operand. When

the operand has signal state "1", the normally closed contact opens and the signal state at the output of the

instruction is reset to "0".

When the operand has signal state "0", the normally closed contact is not enabled and the signal

state of the input is transferred to the output.

Two or more normally closed contacts are linked bit-by-bit by AND when connected in series. With a

series connection, power flows when all contacts are closed.

The normally closed contacts are linked by OR when connected in parallel. With a parallel connection,

power flows when one of the contacts is closed.

Parameter

The following table shows the parameters of the instruction:

Parameter

Description

Declaration

Data type

S7-1200

<Operand>

Input

BOOL

I, Q, M, D, L

Example

The following example shows how the instruction works:

Memory area

S7-1500

I, Q, M, D, L, T, C

Operand

whose signal

state is

queried.

�Bit logic operations (S7-1200, S7-1500)

The "TagOut" operand is set when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The operand "TagIn_3" has the signal state "0".

--|NOT|--: Invert RLO

Description

You use the "Invert RLO" instruction to invert the signal state of the result of logic operation (RLO). If the

signal state is "1" at the input of the instruction, the output of the instruction has signal state "0". If the

signal state is "0" at the input of the instruction, the output has the signal state "1".

Example

The following example shows how the instruction works:

Operand "TagOut" is reset when one of the following conditions is fulfilled:

The operand "TagIn_1" has the signal state "1".

The signal state of the operands "TagIn_2" and "TagIn_3" is "1".

---( )---: Assignment

Description

You can use the "Assignment" instruction to set the bit of a specified operand. If the result of logic operation

(RLO) at the input of the coil has signal state "1", the specified operand is set to signal state "1". If the signal

state is "0" at the input of the coil, the bit of the specified operand is reset to "0".

The instruction does not influence the RLO. The RLO at the input of the coil is sent directly to the output.

Parameter

The following table shows the parameters of the "Assignment" instruction:

Parameter

Declaration

Data type

Memory area

Description

<Operand>

Output

BOOL

I, Q, M, D, L

Operand to which

the RLO is

assigned.

�Bit logic operations (S7-1200, S7-1500)

Example

The following example shows how the instruction works:

The "TagOut_1" operand is set when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The signal state of the operand "TagIn_3" is "0".

The "TagOut_2" operand is set when one of the following conditions is fulfilled:

Operands "TagIn_1", "TagIn_2", and "TagIn_4" have signal state "1".

The signal state of the "TagIn_3" operand is "0" and the signal state of the "TagIn_4" operand is "1".

--( / )--: Negate assignment

Description

The "Negate assignment" instruction inverts the result of logic operation (RLO) and assigns it to the specified

operand.

When the RLO at the input of the coil is "1", the operand is reset. When the RLO at the input of the coil is "0",

the operand is

set to signal state "1".

Parameter

The following table shows the parameters of the "Negate assignment" instruction:

Parameter

Declaration

Data type

Memory area

Description

<Operand>

Output

BOOL

I, Q, M, D, L

Operand to which

the RLO is

assigned.

Example

The following example shows how the instruction works:

Operand "TagOut_1" is reset when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The signal state of the operand "TagIn_3" is "0".

�Bit logic operations (S7-1200, S7-1500)

---( R )---: Reset output

Description

You can use the "Reset output" instruction to reset the signal state of a specified operand to "0".

The instruction is only executed if the result of logic operation (RLO) at the input of the coil is "1". If power

flows to the coil (RLO = "1"), the specified operand is reset to "0". If the RLO at the input of the coil is "0"

(no signal flow to the coil), the signal state of the specified operand remains unchanged.

Parameter

The following table shows the parameters of the "Reset output" instruction:

Parameter

Declaration

Data type

Memory area

S7-1200

<Operand>

M, D, L, T,

Output

BOOL

S7-1500

Description

I, Q, M, D, L

I, Q,

Operand that is

reset when RLO

= "1".

Example

The following example shows how the instruction works:

Operand "TagOut" is reset when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The signal state of the operand "TagIn_3" is "0".

---( S )---: Set output

Description

You can use the "Set output" instruction to set the signal state of a specified operand to "1".

The instruction is only executed if the result of logic operation (RLO) at the input of the coil is "1". If power

flows to the coil (RLO = "1"), the specified operand is set to "1". If the RLO at the input of the coil is "0" (no

signal flow to the coil), the signal state of the specified operand remains unchanged.

Parameter

The following table shows the parameters of the "Set output" instruction:

Parameter

Declaration

Data type

Memory area

Description

<Operand>

Output

BOOL

I, Q, M, D, L

Operand which is

set

�with RLO = "1".

Example

The following example shows how the instruction works:

The "TagOut" operand is set when one of the following conditions is fulfilled:

The operands "TagIn_1" and "TagIn_2" have signal state "1".

The signal state of the operand "TagIn_3" is "0".

SET_BF: Set bit field

Description

You use the instruction "Set bit field" to set multiple bits starting from a certain address.

You determine the number of bits to be set using the value of <Operand1>. The address of the first bit to be

set is defined by

<Operand2>. If the value of <Operand1> is greater than the number of bits in a selected byte, then the bits

of the next byte

will be set. The bits remain set until they are explicitly reset, for example, by another instruction.

The instruction is only executed if the result of logic operation (RLO) at the input of the coil is "1". If the

RLO at the input of the coil is "0", the instruction does not execute.

Parameter

The following table shows the parameters of the "Set bit field" instruction:

Parameter

Description

<Operand2>

Declaration

Output

Data type

BOOL

Memory area

I, Q, M

In the case of a

DB or an IDB, an

element of an

ARRAY[..] of

BOOL

<Operand1>

of bits to be

Input

UINT

Pointer to the first

bit to be set.

Constant

Number

set.

Example

The following example shows how the instruction works:

If the operands "TagIn_1" and "TagIn_2" have the signal state "1", 5 bits are set starting at the address of the

operand

�"MyDB".MyBoolArray[4]

RESET_BF: Reset bit feld

Descripti

on

You use the "Reset bit field" instruction to reset several bits starting from a

certain address.

You specify the number of bits to be reset using the value of <Operand1>. The address of the first bit to be

reset is specified by <Operand2>. If the value of <Operand1> is greater than the number of bits in a

selected byte, the bits of the next byte will be reset. The bits remain reset until they are explicitly set, for

example, by another instruction.

The instruction is only executed if the result of logic operation (RLO) at the input of the coil is "1". If the

RLO at the input of the coil is "0", the instruction does not execute.

Paramet

er

The following table shows the parameters of the "Reset bit field"

instruction:

Parameter

Description

<Operand2>

Declaration

Output

Data type

BOOL

Memory area

I, Q, M

In the case of a

DB or an IDB, an

element of an

ARRAY[..] of

BOOL

<Operand1>

Input

UINT

Constant

Pointer to the first

bit to be reset.

Number of bits to

be reset.

Example

The following example shows how the instruction works:

If the operands "TagIn_1" and "TagIn_2" have the signal state "1", 5 bits are reset starting at the address of

the operand

"MyDB".MyBoolArray[4]

SR: Set/reset flip-fop

Description

Use the instruction "Set/reset flip-flop" to set or reset the bit of the specified operand, depending on the

signal state of the inputs S and R1. If the signal state is "1" at input S and "0" at input R1, the specified

operand is set to "1". If the signal state is "0" at input S and "1" at input R1, the specified operand will be

reset to "0".

Input R1 takes priority over input S. When the signal state is "1" on both inputs S and R1, the signal state

of the specified operand is reset to "0".

The instruction is not executed if the signal state at the two inputs S and R1 is "0". The signal state of

the operand then remains unchanged.

�The current signal state of the operand is transferred to output Q and can be queried there.

Parameter

The following table shows the parameters of the "Set/reset flip-flop" instruction:

Parameter

Declaration

Data type

Memory area

Description

S7-1200

S7-1500

I, Q, M, D,

L

I, Q, M, D,

L

I, Q, M, D, L

Enable setting

I, Q, M, D, L,

T, C

Enable

resetting

Input

BOOL

R1

Input

BOOL

<Operand>

InOut

BOOL

I, Q, M, D,

L

I, Q, M, D, L

Operand that

is set or

reset.

Output

BOOL

I, Q, M, D,

L

I, Q, M, D, L

Signal state

of the

operand

Example

The following example shows how the instruction works:

The operands "TagSR" and "TagOut" are set when the following conditions are fulfilled:

The operand "TagIn_1" has the signal state "1".

The operand "TagIn_2" has the signal state "0".

The operands "TagSR" and "TagOut" are reset when one of the following conditions is fulfilled:

The operand "TagIn_1" has signal state "0" and the operand "TagIn_2" has signal state "1".

The operands "TagIn_1" and "TagIn_2" have signal state "1".

RS: Reset/set fip-fop

Descripti

on

You can use the "Reset/set flip-flop" instruction to reset or set the bit of a specified operand based on the

signal state of the inputs R and S1. If the signal state is "1" at input R and "0" at input S1, the specified

operand will be reset to "0". If the signal state is "0" at input R and "1" at input S1, the specified operand is

set to "1".

Input S1 takes priority over input R. When the signal state is "1" at both inputs R and S1, the signal state

of the specified operand is set to "1".

The instruction is not executed if the signal state at the two inputs R and S1 is "0". The signal state of

the operand then remains unchanged.

The current signal state of the operand is transferred to output Q and can be

queried there.

�Parameter

The following table shows the parameters of the "Reset/set flip-flop" instruction:

Parameter

Declaration

Data type

Memory area

S7-1200

S7-1500

I, Q, M, D,

L

I, Q, M, D,

L

I, Q, M, D, L

Description

Input

BOOL

S1

Input

BOOL

<Operand>

InOut

BOOL

I, Q, M, D,

L

I, Q, M, D, L

Operand that

is reset or

set.

Output

BOOL

I, Q, M, D,

L

I, Q, M, D, L

Signal state

of the

operand

I, Q, M, D, L,

T, C

Enable

resetting

Enable setting

Example

The following example shows how the instruction works:

The operands "TagRS" and "TagOut" are reset when the following conditions are fulfilled:

The operand "TagIn_1" has the signal state "1".

The operand "TagIn_2" has the signal state "0".

The operands "TagRS" and "TagOut" are set when one of the following conditions is fulfilled:

The operand "TagIn_1" has signal state "0" and the operand "TagIn_2" has signal state "1".

The operands "TagIn_1" and "TagIn_2" have signal state "1".

--|P|--: Scan operand for positive signal edge

Description

You can use the "Scan operand for positive signal edge" instruction to determine if there is a "0" to "1"

change in the signal state of a specified operand (<Operand1>). The instruction compares the current signal

state of <Operand1> with the signal state of the previous scan that is saved in an edge memory bit

(<Operand2>). If the instruction detects a change in the result of logic operation (RLO) from "0" to "1", there

is a positive, rising edge.

If a positive edge is detected, the output of the instruction has the signal state "1". In all other cases, the

signal state at the output of the instruction is "0".

Specify the operand to be queried (<Operand1>) in the operand placeholder above the instruction. Specify

the edge memory bit (<Operand2>) in the operand placeholder below the instruction.

�Note

The address of the edge memory bit must not be used more than once in the program, otherwise the bit

memory is

overwritten. This step influences the edge evaluation and the result is therefore no longer unique. The

memory area of

the edge memory bit must be located in a DB (static area for FB) or in the bit memory area.

Parameter

The following table shows the parameters of the "Scan operand for positive signal edge" instruction:

Parameter

Declaration

Data type

S7-1200

<Operand1>

<Operand2>

Input

InOut

BOOL

BOOL

I, Q, M, D, L

I, Q, M, D, L

Memory area

Description

S7-1500

I, Q, M, D, L, T, C

Signal to

be

scanned

I, Q, M, D, L

Edge

memory bit

in which the signal

state of the

previous query is

saved.

Example

The following example shows how the instruction works:

Operand "TagOut" is set when the following conditions are fulfilled:

The operands "TagIn_1", "TagIn_2", and "TagIn_3" have signal state "1".

There is a rising edge at operand "TagIn_4". The signal state of the previous scan is stored in the edge

memory bit

"Tag_M".

The signal state of the operand "TagIn_5" is "1".

--|N|--: Scan operand for negative signal edge

Descripti

on

You can use the "Scan operand for negative signal edge" instruction to determine if there is a "1" to "0"

change in the signal state of a specified operand (<Operand1>). The instruction compares the current

signal state of <Operand1> with the signal state of the previous scan that is saved in an edge memory bit

<Operand2>. If the instruction detects a change in the result of logic operation (RLO) from "1" to "0", there

is a negative, falling edge.

If a negative signal edge is detected, the output of the instruction has the signal state "1". In all other

cases, the signal state at the output of the instruction is "0".

Specify the operand to be queried (<Operand1>) in the operand placeholder above the instruction. Specify

the edge memory bit (<Operand2>) in the operand placeholder below the instruction.

�Note

The address of the edge memory bit must not be used more than once in the program, otherwise the bit

memory is

overwritten. This step influences the edge evaluation and the result is therefore no longer unique. The

memory area of

the edge memory bit must be located in a DB (static area for FB) or in the bit memory area.

Parameter

The following table shows the parameters of the "Scan operand for negative signal edge" instruction:

Parameter

Description

Declaration

Data type

Memory area

S7-1200

S7-1500

<Operand1>

Input

BOOL

I, Q, M, D, L

I, Q, M, D, L, T, C

Signal to

be

scanned

<Operand2>

InOut

BOOL

I, Q, M, D, L

I, Q, M, D, L

Edge

memory bit in

which the signal

state of the

previous query is

saved.

Example

The following example shows how the instruction works:

Operand "TagOut" is set when the following conditions are fulfilled:

The operands "TagIn_1", "TagIn_2", and "TagIn_3" have signal state "1".

There is a negative signal edge at operand "TagIn_4". The signal state of the previous scan is stored in

the edge memory bit "Tag_M".

The signal state of the operand "TagIn_5" is "1".

--(P)--: Set operand on positive signal edge

Description

You can use the "Set operand on positive signal edge" instruction to set a specified operand (<Operand1>)

when there is a "0" to "1" change in the result of logic operation (RLO). The instruction compares the current

RLO with the RLO from the previous query, which is saved in the edge memory bit (<Operand2>). If the

instruction detects a change in the RLO from "0" to "1", there is a positive signal edge.

When a positive signal edge is detected, <Operand1> is set to signal state "1" for one program cycle. In all

other cases, the operand has the signal state "0".

Specify the operand to be set (<Operand1>) in the operand placeholder above the instruction. Specify the

edge memory bit

(<Operand2>) in the operand placeholder below the instruction.

Note

�The address of the edge memory bit must not be used more than once in the program, otherwise the

bit memory is overwritten. This step influences the edge evaluation and the result is therefore no

longer unique. The memory area of the edge memory bit must be located in a DB (static area for FB) or

in the bit memory area.

Parameter

The following table shows the parameters of the "Set operand on positive signal edge" instruction:

Parameter

Declaration

Data type

Memory area

Description

<Operand1>

Output

BOOL

I, Q, M, D, L

Operand which is

set by a positive

edge.

<Operand2>

InOut

BOOL

I, Q, M, D, L

Edge memory bit

Example

The following example shows how the instruction works:

Operand "TagOut" is set for one program cycle, when the signal state at the input of the coil switches from

"0" to "1" (positive signal edge). In all other cases, the operand "TagOut" has the signal state "0".

--(N)--: Set operand on negative signal edge

Description

You can use the "Set operand on negative signal edge" instruction to set a specified operand (<Operand1>)

when there is a "1" to "0" change in the result of logic operation (RLO). The instruction compares the current

RLO with the RLO from the previous query, which is saved in the edge memory bit (<Operand2>). If the

instruction detects a change in the RLO from "1" to "0", there is a negative edge.

When a negative signal edge is detected, <Operand1> is set to signal state "1" for one program cycle. In all

other cases, the operand has the signal state "0".

Specify the operand to be set (<Operand1>) in the operand placeholder above the instruction. Specify the

edge memory bit

(<Operand2>) in the operand placeholder below the instruction.

Note

The address of the edge memory bit must not be used more than once in the program, otherwise the bit

memory is

overwritten. This step influences the edge evaluation and the result is therefore no longer unique. The

memory area of

the edge memory bit must be located in a DB (static area for FB) or in the bit memory area.

Parameter

The following table shows the parameters of the "Set operand on negative signal edge" instruction:

Parameter

Description

Declaration

Data type

Memory area

�<Operand1>

Output

BOOL

I, Q, M, D, L

<Operand2>

InOut

BOOL

I, Q, M, D, L

Operand which is

by a negative

set

edge.

Edge memory bit

Example

The following example shows how the instruction works:

Operand "TagOut" is set for one program cycle, when the signal state at the input of the coil switches from

"1" to

"0" (negative signal edge). In all other cases, the operand "TagOut" has the signal state "0".

P_TRIG: Scan RLO for positive signal edge

Description

Use the "Scan RLO for positive signal edge" instruction to query a "0" to "1" change in the signal state of

the result of logic operation (RLO). The instruction compares the current signal state of the RLO with the

signal state of the previous query, which is saved in an edge memory bit (<operand>). If the instruction

detects a change in the RLO from "0" to "1", there is a positive signal edge.

If a positive edge is detected, the output of the instruction has the signal state "1". In all other cases, the

signal state at the output of the instruction is "0".

Note

The address of the edge memory bit must not be used more than once in the program, otherwise the bit

memory is

overwritten. This step influences the edge evaluation and the result is therefore no longer unique. The

memory area of

the edge memory bit must be located in a DB (static area for FB) or in the bit memory area.

Parameter

The following table shows the parameters of the "Scan RLO for positive signal edge" instruction:

Parameter

Declaration

CLK

Input

<Operand>

InOut

Output

Example

Data type

Memory area

BOOL

I, Q, M, D,

BOOL

L M, D

BOOL

I, Q, M, D, L

Description

Current RLO

Edge memory bit

in

which the RLO of

the

previous query is

saved.

Result of

edge

evaluation

�The following example shows how the instruction works:

The RLO of the previous query is saved in the edge memory bit "Tag_M". If a "0" to "1" change is detected in

the signal state of the RLO, the program jumps to jump label CAS1.

N_TRIG: Scan RLO for negative signal edge

Description

Use the "Scan RLO for negative signal edge" instruction to query a "1" to "0" change in the signal state of

the result of logic operation (RLO). The instruction compares the current signal state of the RLO with the

signal state of the previous query, which is saved in an edge memory bit (<operand>). If the instruction

detects a change in the RLO from "1" to "0", there is a negative edge.

If a negative signal edge is detected, the output of the instruction has the signal state "1". In all other

cases, the signal state at the output of the instruction is "0".

Note

The address of the edge memory bit must not be used more than once in the program, otherwise the bit

memory is

overwritten. This step influences the edge evaluation and the result is therefore no longer unique. The

memory area of

the edge memory bit must be located in a DB (static area for FB) or in the bit memory area.

Parameter

The following table shows the parameters of the "Scan RLO for negative signal edge" instruction:

Parameter

Declaration

CLK

Input

<Operand>

InOut

Output

Data type

Memory area

BOOL

I, Q, M, D,

BOOL

L M, D

BOOL

I, Q, M, D, L

Example

The following example shows how the instruction works:

Description

Current RLO

Edge memory bit

in

which the RLO of

the

previous query is

saved.

Result of

edge

evaluation

�The RLO of the previous query is saved in the edge memory bit "Tag_M". If a "1" to "0" change is detected in

the signal state

of the RLO, the program jumps to jump label CAS1.

R_TRIG: Set tag on positive signal edge

Description

You can use the "Set tag on positive signal edge" instruction to set a specified tag in the instance DB when

there is a "0" to "1" change in the result of logic operation (RLO). The instruction compares the current RLO

at the input CLK with the RLO from the previous query, which is saved in the specified instance DB. If the

instruction detects a change in the RLO from "0" to "1", there is a positive signal edge.

If a positive edge is detected, the tag in the instance DB is set to signal state "1" and the output Q returns

the signal state "1" In all other cases, the signal state at the output of the instruction is "0".

When you insert the instruction in the program, the "Call options" dialog opens automatically. In this dialog

you can specify whether the edge memory bit is stored in its own data block (single instance) or as a local

tag (multiple instance) in the block interface. If you create a separate data block, you will find it in the

project tree in the "Program resources" folder under "Program blocks > System blocks". For additional

information on this topic, refer to "See also".

Parameter

The following table shows the parameters of the instruction "Set tag on positive signal edge":

Parameter

Declaration

Data type

Memory area

Description

EN

Input

BOOL

I, Q, M, D, L

Enable input

ENO

Output

BOOL

I, Q, M, D, L

Enable output

CLK

Input

BOOL

I, Q, M, D, L

or constant

Incoming signal

whose edge will

be queried.

Output

BOOL

I, Q, M, D, L

Result of

edge

evaluation

Example

The following example shows how the instruction works:

�The RLO of the preceding query is saved in the instance DB "R_TRIG_DB". If a change is the signal state of

the RLO from "0" to "1" is detected in the operands "TagIn_1" and "TagIn_2" or in the operand "TagIn_3",

the output "TagOut_Q" has signal state "1".

F_TRIG: Set tag on negative signal edge

Description

You can use the "Set tag on negative signal edge" instruction to set a specified tag in the instance DB when

there is a "1" to "0" change in the result of logic operation (RLO). The instruction compares the current RLO

at the input CLK with the RLO from the previous query, which is saved in the specified instance DB. If the

instruction detects a change in the RLO from "1" to "0", there is a negative edge.

If a negative edge is detected, the tag in the instance DB is set to signal state "1" and the output Q returns

the signal state

"1" In all other cases, the signal state at the output of the instruction is "0".

When you insert the instruction in the program, the "Call options" dialog opens automatically. In this dialog

you can specify whether the edge memory bit is stored in its own data block (single instance) or as a local

tag (multiple instance) in the block interface. If you create a separate data block, you will find it in the

project tree in the "Program resources" folder under "Program blocks > System blocks". For additional

information on this topic, refer to "See also".

Parameter

The following table shows the parameters of the instruction "Set tag on negative signal edge":

Parameter

Declaration

Data type

Memory area

Description

EN

Input

BOOL

I, Q, M, D, L

Enable input

ENO

Output

BOOL

I, Q, M, D, L

Enable output

CLK

Input

BOOL

I, Q, M, D, L

or constant

Incoming signal

whose edge will

be queried.

Output

BOOL

I, Q, M, D, L

Result of

edge

evaluation

Example

The following example shows how the instruction works:

�Bit logic operations (S7-1200, S7-1500)

Page 17 of 17

The RLO of the preceding query is saved in the instance DB "F_TRIG_DB". If a change is the signal state of

the RLO from "1" to "0" is detected in the operands "TagIn_1" and "TagIn_2" or in the operand "TagIn_3",

the output "TagOut_Q" has signal state "1".