0% found this document useful (0 votes)

72 views21 pagesRethinking Code Generation

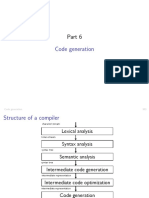

The document discusses rethinking the approach to code generation in compilers. Currently, code generation is broken into separate stages like instruction selection, register allocation, and instruction scheduling. However, these stages are interdependent and their order is not optimal. The document proposes using constraint programming to model code generation as a single combinatorial optimization problem rather than separate heuristic stages. This unified approach could potentially generate optimal code while being more flexible and reducing errors when platforms change.

Uploaded by

DavidCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

72 views21 pagesRethinking Code Generation

The document discusses rethinking the approach to code generation in compilers. Currently, code generation is broken into separate stages like instruction selection, register allocation, and instruction scheduling. However, these stages are interdependent and their order is not optimal. The document proposes using constraint programming to model code generation as a single combinatorial optimization problem rather than separate heuristic stages. This unified approach could potentially generate optimal code while being more flexible and reducing errors when platforms change.

Uploaded by

DavidCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 21