0% found this document useful (0 votes)

66 views7 pagesLec 7c ProgrammingIO

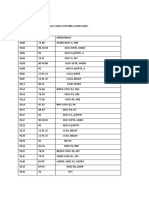

1. The keyboard and display are non-memory mapped I/O devices with dedicated registers for access.

2. Writing to VRAM addresses C000-FDFF sets pixels on the display; reading the KBDR register returns the last pressed key code.

3. The program polls the KBSR status register to check if KBDR has new keyboard data before reading KBDR.

Uploaded by

Anonymous zN7CjfgnECopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

66 views7 pagesLec 7c ProgrammingIO

1. The keyboard and display are non-memory mapped I/O devices with dedicated registers for access.

2. Writing to VRAM addresses C000-FDFF sets pixels on the display; reading the KBDR register returns the last pressed key code.

3. The program polls the KBSR status register to check if KBDR has new keyboard data before reading KBDR.

Uploaded by

Anonymous zN7CjfgnECopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 7