0% found this document useful (0 votes)

86 views25 pagesData-Flow Modeling (A Practical Introduction To HW/SW Codesign, P. Schaumont)

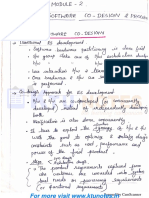

Data-flow modeling uses concurrent models to describe potentially parallel systems. It introduces data-flow models as a classic mechanism for concurrent application modeling. Data-flow models represent applications as connected actors that process and pass tokens along queues. Synchronous data-flow graphs have fixed token consumption and production rates, making them deterministic and suitable for safety-critical embedded systems.

Uploaded by

aishwarya waghCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

86 views25 pagesData-Flow Modeling (A Practical Introduction To HW/SW Codesign, P. Schaumont)

Data-flow modeling uses concurrent models to describe potentially parallel systems. It introduces data-flow models as a classic mechanism for concurrent application modeling. Data-flow models represent applications as connected actors that process and pass tokens along queues. Synchronous data-flow graphs have fixed token consumption and production rates, making them deterministic and suitable for safety-critical embedded systems.

Uploaded by

aishwarya waghCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 25