0% found this document useful (0 votes)

52 views27 pagesHigh Level Synthesis - 02 - Basic Concepts

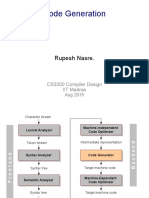

The document provides an overview of high level synthesis and intermediate representations used in digital system design methodologies. It discusses the use of intermediate representations to break compilers into manageable pieces and isolate parts of the design process. The key types of intermediate representations covered are abstract syntax trees, linear operator forms, directed acyclic graphs, control flow graphs, program dependence graphs, static single assignment form, and 3-address code. Basic blocks and control flow graphs are defined and an example control flow graph is shown. Static single assignment form and phi functions are introduced as ways to handle variables in control flow structures. Data flow graphs are discussed as a way to model data dependencies.

Uploaded by

a bCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

52 views27 pagesHigh Level Synthesis - 02 - Basic Concepts

The document provides an overview of high level synthesis and intermediate representations used in digital system design methodologies. It discusses the use of intermediate representations to break compilers into manageable pieces and isolate parts of the design process. The key types of intermediate representations covered are abstract syntax trees, linear operator forms, directed acyclic graphs, control flow graphs, program dependence graphs, static single assignment form, and 3-address code. Basic blocks and control flow graphs are defined and an example control flow graph is shown. Static single assignment form and phi functions are introduced as ways to handle variables in control flow structures. Data flow graphs are discussed as a way to model data dependencies.

Uploaded by

a bCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 27