0% found this document useful (0 votes)

79 views61 pagesCoa 03 Function Interconnection

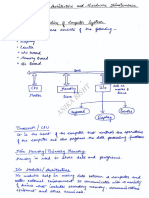

This document provides an overview of computer functions and interconnection. It discusses implementing functions via hardwired or software-based approaches. It describes the basic components of a computer including the control unit, arithmetic logic unit, memory, and input/output. It then explains the instruction cycle involving fetch and execute steps. The document discusses interrupts and how they allow other modules to interrupt normal processing. It also covers how components are interconnected using buses for data, addresses, and control and how this allows different units to communicate.

Uploaded by

muhammad farooqCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

79 views61 pagesCoa 03 Function Interconnection

This document provides an overview of computer functions and interconnection. It discusses implementing functions via hardwired or software-based approaches. It describes the basic components of a computer including the control unit, arithmetic logic unit, memory, and input/output. It then explains the instruction cycle involving fetch and execute steps. The document discusses interrupts and how they allow other modules to interrupt normal processing. It also covers how components are interconnected using buses for data, addresses, and control and how this allows different units to communicate.

Uploaded by

muhammad farooqCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 61