Chapter 2

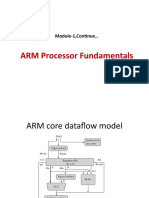

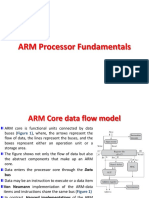

ARM Processor Fundamentals

(Note: MAC = multiply-accumulate unit)

- A 32-bit processor implemented either by

Von Neumann architecture ( shown above)

or

Harvard architecture with 2 types of instruction sets—

load and store instructions

- Instructions have 2 source registers (Rn and Rm) and one destination

register (Rd)

- Rm can be preprocessed in the barrel shifter before it enters the ALU

1

�2.1 Register

- Up to 18 active register:

16 data registers (r0~r15) : for holding either data or address

2 processor status registers

- r13 : stack pointer (sp)

- r14 : link register (lr)

- r15 : program counter (pc)

- r0~r13 are orthogonal (equally well application)

- cpsr : current program status register

- spsr : saved program status register

2

�2.2 Current Program Status Register

Divided into 4 fields (each with 8-bit wide):

- Flags : holding instruction conditions

- Status : reserved

- Extension : reserved

- Control : indicate the processor mode

3

�2.2.1 Processor Modes

- The processor mode determines which registers are active and

the access rights to the cpsr register itself.

- 7 processor modes:

Processor mode Abbrev. Description Notes

Noraml program exection

User usr

mode

Run privileged OS tasks

System sys P

A protected mode for the OS

Supervisor svc p, e

Implements virtual memory

Abort abt p, e

and/or memory protection

Supports software emulation

Undefined und p, e

of hardware coprocessors

Used for general-purpose

Interrupt irq p, e

interrupt handling

Supports a high-speed data

Fast interrupt fiq p, e

transfer or channel process

[note] Privileged modes : p Execption modes : e

- Each process mode is either privileged or nonprivileged

A privileged mode allows full read-write access to the cpsr

A nonprivileged mode only allows to read access to the

control filed in the cpsr but still allows read-write access to

the condition flags.

4

�2.2.2 Banked Registers

- 37 registers in the register file.

- 20 registers, called banked registers (identifed by the shading in the

diagram), are hidden from a program at different times.

- All processor modes except system mode have a set of associate banked

registers that are a subset of the main 16 registers.

- A banked register maps one-to-one onto a user mode register

- The processor mode can be changed by a program that writes directly to

the cpsr, if it has the privilege.

- The following exceptions and interrupts cause a mode change:

+ Reset

+ Interrupt request

+ Fast interrupt request

+ Software interrupt

+ Data abort,

+ Prefetch abort

+ Undefined instruction.

5

�2.2.2 Banked Registers (cont.)

- The cprs is not coped into spsr when a mode change is

forced due to a program writing directly to the cpsr.

- The saving of the cspr only occurs when an exception or

interrupt is raised.

6

�2.2.3 State and Instruction Sets

- There are 3 instruction sets :

ARM – 32-bit instructions

Thumb – 16-bit instructions

Jeazelle – 8-bit instructions

- No intermingle sequence of different instruction set is

allowed.

- The hardware portion of Jazelle only supports a subset of the

Java byecodes; the rest are emulated in software.

2.2.4 Interrupt masks

- Two interruput marks—I and F—are used to stop specific

interrupt requests from interrupting the processor.

- The mask bits, 7 and 6 (or I and F), are used to control the

masking of IRQ and FIQ, respectively.

7

�2.2.5 Condition Flags

- The hardware only sets the flags.

- To clear the flag you need to write to the cpsr.

- Bit 5 is used to set for thumb-enable.

- Bit 24 is uese to set for Jazelle-enable.

8

�2.2.6 Condition Execution

- Most instructions have a condition attribute that determines if

the core will execute it based on the setting of the condition

flag.

- The condition attribute is postfixed in the instruction

mnemonic, which is coded into the instruction.

9

�2.3 Pipeline

- to speed up instruction execution

- ARM9 : 1.1 Dhrystone MIPS per Mhz—an increasing in

instruction throughput by around 13% compared with an

ARM7.

- ARM10 : 1.3 Dhrystone MIPS per Mhz—an increasing in

instruction throughput by around 34% compared with an

ARM7.

-

10

�- 2.3.1 Pipeline Executing Characteristics

- In ARM state, the pc always points to the address of the

instruction plus 8 bytes.

- In Thumb state, the pc is the instruction address plus 4 bytes

- The execution of a branch instruction or branching by the

direct modification of the pc causes the ARM core to flush its

pipeline

.

- ARM10 uses branch prediction which reduces the effect of a

pipeline flush.

- An instruction in the execute stage will complete even though

an interrupt has been raised. Other instructions in the pipeline

will be abounded.

11

� 2.4 Exceptions, Interrupts, and the Vector Table

- When an exception or interrupt occurs, the processor sets the

pc to a specific memory address.

- The interrupt address is within a special address called vector

table

- The entries in the vector table are instructions that branch to

specific routines designed to handles a particular exception or

interrupt.

- The memory map address 0x0000000 is reserved for the vector

table, a set of 32-bit words.

- On some processes the vector table can be optionally located at

a higher address in memory—starting at the offset 0xffff0000.

12

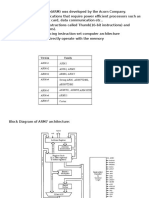

�2.5 Core Extensions

- To improve performance, manage resources, and provide

extra functionality.

- - Three hardware extension: cache and tightly couple menory,

memory management, and coprocessor interface.

2.5.1 Cache and Tightly Couple Memory

- Two types of cache:

+ cache for the combination of data and instruction which is

attached to the von Neumann-style core.

+ cache for separated data and instruction which is attached

to the Harvard-style core.

13

�2.5.1 Cache and Tightly Couple Memory (cont.)

- The tightly coupled memory (TCM), a type of fast SRAM, is

located close to the core for the real-time system.

- TCMs appear as memory in the address map and can be

accessed as fast memory.

- A combination of caches and TCMs is shown below.

14

� 2.5.2 Memory Management

- Generally, embedded system use multiple memory

devices—ROM, SRAM, FlahROM, DRAM

- It’s necessary to have a method to help organize these devices

and protect the system from applications trying to make

inappropriate accesses to hardware.

- ARM cores have 3 different types of memory management

hardware:

+ No extensions – nonprotected memory for small, simple

embedded systems.

+ Memory protection unit (MPU) – using a limited number of

memory region which are controlled with a set of special

coprocessor registers, and each region is defined with

specific access permission.

+ Memory management unit (MMU) – using a set of

translation table to provide fine-grained control over

memory, which are stored in main memory and provide a

virtual-to-physical address memory map as well as access

permission.

15

�2.6 Architecture Revisions

Every ARM processor implementation executes a specific

instruction set architecture—ISA.

2.6.1 Nomenclature

- JTAG : IEEE1149.1 Standard Test Access Port

- EmbeddedICE macrocell : the debug hardware built into the

processor that allows breakpoints and watchpoints to be set.

(ICE : in-circuit emulator)

- Synthesizible : meaning that the processor core is supplied as

source code that can be compiled into a form easily used by

EDA (electronic design automation) tools.

16

�2.6.2 Architecture Evolution

17

�2.7 ARM Processor Families

-end-

18