0% found this document useful (0 votes)

88 views41 pagesCmos Process Flow 1

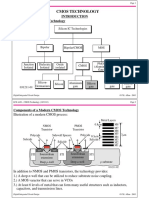

The document describes the key steps in fabricating CMOS integrated circuits using different process flows. It discusses wafer preparation, oxidation, lithography, etching, and metallization. Specifically, it covers growing silicon crystals with controlled doping, oxidizing silicon to form insulating silicon dioxide layers, using photolithography to pattern circuits, and constructing CMOS inverters using N-well, P-well, and twin-tub processes. The fabrication process involves carefully controlling multiple steps to build up functional transistors and logic gates on a silicon wafer.

Uploaded by

barnwaldivyanshu7Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

88 views41 pagesCmos Process Flow 1

The document describes the key steps in fabricating CMOS integrated circuits using different process flows. It discusses wafer preparation, oxidation, lithography, etching, and metallization. Specifically, it covers growing silicon crystals with controlled doping, oxidizing silicon to form insulating silicon dioxide layers, using photolithography to pattern circuits, and constructing CMOS inverters using N-well, P-well, and twin-tub processes. The fabrication process involves carefully controlling multiple steps to build up functional transistors and logic gates on a silicon wafer.

Uploaded by

barnwaldivyanshu7Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 41