0% found this document useful (0 votes)

26 views14 pagesExp 4

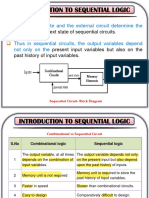

The document discusses the synthesis of various types of flip flops including SR, JK, D, and T flip flops. It explains the components, theory, circuit diagrams, characteristic tables, and truth tables of each flip flop. The procedure involves using logic gates to construct the flip flops in a simulator and testing their output by providing different input combinations and clock pulses. The synthesis of flip flops was executed successfully for all four types.

Uploaded by

Cherry Charan TejCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

26 views14 pagesExp 4

The document discusses the synthesis of various types of flip flops including SR, JK, D, and T flip flops. It explains the components, theory, circuit diagrams, characteristic tables, and truth tables of each flip flop. The procedure involves using logic gates to construct the flip flops in a simulator and testing their output by providing different input combinations and clock pulses. The synthesis of flip flops was executed successfully for all four types.

Uploaded by

Cherry Charan TejCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 14