0 ratings0% found this document useful (0 votes)

46 views23 pagesUnit-4 MPI

Uploaded by

hofehag577Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

0 ratings0% found this document useful (0 votes)

46 views23 pagesUnit-4 MPI

Uploaded by

hofehag577Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

You are on page 1/ 23

PROGRAMMABLE PERIPHERAL INTERFACE (PPI) 8255

‘The 8255 (PPI) is a programmable, parallel input/output device. It can be programmed to

transfer data under different conditions, from simple input/output. It is flexible, versatile and

economical (When multiple input/output ports are reqired), but some what complex. It is widely

used with almost any microprocessor.

The 8255 has 40 pins, out of these 24 input/output pins can be grouped in 8-bit parallel

ports : Port A and Port B, with the remaining eights bits as port C. The port C can be used

as individual or be grouped in two 4-bit ports namely, port Cyppr (Cu) and port CLower (Ci)

as shown in fig. 10.1. The function of these ports are defined by writing a control word in

the control register.

Port A

82554

Port ©

Port 8

Fig. 10.1 : 8255 Input/Output ports

‘Scanned with CamSeanner

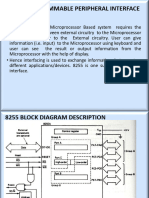

a lock Diagram of the 8255 ne

rs block diagram is shown in fig, 10.2

‘Various elements and the

ie ir functions areas follows

i is 8 pins (PAo~ PA.) fi in

es = Coisatns a ‘or receiving/sending data it

18 data itis used as 8 bit parallel

port B: Also

used as 8-bit parallel port It contains 8 pints (PBy —

sending data. :

PB;) for receiving’

art C : Used as 8-bit parallel port. It can be divided into two

and Ciower (Cx): It contains 8-pins (PC, —

can also be used for handshake signals,

i) Control Logie

{90 4-bit ports: Cuppee (Cu)

PCr) for receiving/sending data. Port C pins

The control section has six lines. Their functions are as follows: *

RD (Read) : This control signal enables the read operation. This is ative low signal. When

it oes low the microprocessor reads data from a selected input/output port of the 825

oe

Fe

mics Bel OEO=

eft Gag PAPA,

Supplies Guo pf A a

conto

+

foe

n v0.

Ne

spe

Bidirectional Data Bus Mie

Dy

cl

WR

a

nt

Reset

‘Scanned with CamSeanner

Pin Configuration

Pat of PA,

Pa, 2 30/51 PA,

Pa, 3 385A,

PA, ea arpa,

RDC|s WR

wsef5 35/5 reser

no c|7 Bo,

acts 3650, 0,» Data Bus(Beirectona

acs 32/50, reser Reset input

PC, C10 .8255A 31 Foe

rein soo, s idee

PC, 12 2k, Ro Readinput

Po, 13 20,

peste abo, Wt input

PC, 415, Ev. Port Adress

Po, 16 258, PA, PA Port (Bt)

Po, 17 24 pe, Pcr-PC) Pon 8 (61)

8, 18 23 ps, Vee +5:Vols

Pe, H19 2b pe, aS 0 Vote

8, {20 21 ps,

Fig. 103 : Pin configuration of 8255

WR (Write) : This control signal enables the write operation. This is also an active low

signal. When it goes low, the microprocessor writes into a selected input/output port or the

control register.

RESET(Reset) : It clears the control register and sets all ports in the input mode. Its

active high signal,

(ii) Address: Logic

‘Aq Ai + These pins are generally connected to microprocessor address lines - Ay and

Ay The combination ofthese two is used to identify the address of various ports and cont!

register. For this purpose internal decoder is used.

‘Scanned with CamSeanner

4l

Register

EN

cs

a | tet

Ay intemal p2->c

‘i Decoder [Ot >

Lex fo>4

Fig. 10.4 : Control Logic diagram of 8265

CS (Chip Select)

Itismaster chip select signal. Itis active low signal. When t oes low chip will be selected,

‘Address line other than Ay and A, may be used in-any combination to make the chip select

ogc.

Addresses of ports and control register can be determined b

lines. This is shown in table 10.1 and in fig. 10.4

Table 10.1 : Address decoding for 8255

yy combination of CS. Ar, Ao

a i Port Selected

0 0 a Porth

° o z rote

o 4 = Pon ¢

5 7 1 onto! Register

: 7 x 7255 nol seleced

‘Scanned with CamSeanner

(iv) Control Register

Register which is internal to the 8255 chip is called control register. The contents of thi,

register are known as the control word, Control word specify inpu/output function and modes

of various ports of 8255.

Control register can be accessed to write a control word when both Ag and Ay are

high(shown in table 10.1).

10.2.2 In terfacing Steps

To communicate with peripherals through the 8255, three steps are necessary.

1. Determine the address of ports A, B and C and of the control register by the use

of chip select logic and address lines Ag and Aj.

Determine the control word and write it into the control register.

3. Write input/output instructions to communicate with peripherals through ports A, B

and C.

‘Scanned with CamScanner

40.2.3 Modes of 8255

All the functions of 8255 are classified according to two modes.

(BSR (bit set/reset) Mode

(i) Input/Output Mode

The modes of 8255 are shown in fig. 10.6.

Control Word

Dee,

ol

BSR Mode Input/Output Mode

(Bit Set/Reset)

For Port C Mode 0 Mode 1 & ote 2

Mode Simple Handshake directional

eit Input/output for inpuloubut em for

Band C por

ee, eee andlor B

Port C bits Port B; either

are used for in Mode 0 or 1

handshake

Port C bits are

used for

handshake

‘Scanned with CamSeanner

BEE) PROGRAMMABLE INTERVAL TIMER (PIT) — 8253/8264

The 8253/8254 programmable interval timer is similar to software designed counters and

timers. Accurate time delay can be generated by both 8253 and 8254. Software techniques

for generation of time delays are not accurate and makes microprocessor busy in delay loop.

Thus to overcome this difficulty additional hardware in the form of 8253/8254 is used.

8253/8254 can be used for applications such as a real-time clock, an event counter, adigital

fone shot, a square wave generator and a complex waveform generator,

The 8254 includes three identical 16-bit «

‘one of the six modes.

ers that can operate independently in any

Iris packaged in 24-pin DIP and requires a single + SV power supply.

To operate a counter, a 16-bit count is loaded in its register and, on command, begins to

decrement the count until it reaches to 0, At the end of the count, it generates a pulse that

can be used to interrupt the MPU. The counter can count either in binary or BCD.

8254 is an upgraded version of the 8253, and they are pin-compatible,

The features those differ for both devices are —

1, The 8254 can operate with higher clock frequeney range (DC to 8MHz) and the 8253

ith clock frequency range (DC to 2MHZ).

2. The 8254 includes a status read-back command that can latch the count and the status

of the counters,

‘can operate

The pin diagram of $254 is shown in fig. 10.21

in Configuration

oft Bp ve.

oe 23a WR

pcs 22/5 RD

os apace

o.cfs 2a,

cs wha,

7 isc,

o.cys 175 out,

cx cf 10 care,

: out, }10 ssa,

care, 11 14 our,

ono | 12 13Ficate,

Fig. 1021 : Pin dlagam of 8253/8264

‘Scanned with CamSeanner

40.3.1 Block Diagram of the 8253/8254

Figure 10.21 is the block diagram of the 8254; i i

data bus buter, read/write control logic and a control register. F

(CLK and GATE) and one output signal (OUT)

(@ Data Bus Buffer

This tri-state, 8-bit, bidirectional buffer is connected to the data bus (Dy ~ D3) of the

microprocessor. The data bus bufler has following,

includes three counters (0, 1, and 2), @

ach counter has two input signa}

basic functions

(a) Programming the 8253/8254 in various modes

(b) Loading the count register:

(©) Reading the count value

(i) Controt Logie

The control section has five signals.

ve low signal which is used to read the value of the counters,

RD (Read) : It is an a

For peripheral mapped 10 mode, itis connected to TOR signal and for memory mapped VO

mode, MEMW signal is connected to this pin.

ive low signal which is used to write command or data in counters

or control register. For peripheral mapped UO mode, JOW signal is connected to this pin and

for memory mapped 1 mode MEMW signal is connected to this pin.

‘Ay Ay t Microprocessor address lines Ay and Aj are connected to these pins. Combination

of these two pins are used to identify various counters and control register

€S (Chip Select) : It is an active low signal to make chip select logic, address lines other

than Ag and A; may be used in any combination. If signal at this pin is low, then the 8253/

£8254 will function; otherwise it will not

Table 10.2 : Address decoding for 8253/8254

ss Ai & Selected Counter

2 a 0 Counter 0.

2. wy 1 Counter 1

2 z 0 Counter 2

2 4 1 Control Register

- us x a2sva2a not selected

‘Scanned with CamSeanner

Counters

The chip 8253/8254 includes three 16-bit counters namely : Counter 0, Counter 1 and

counter 2, These are presetable down counter: Each counter has is own 16-bit count epister

to set the count value for the respective counter. The following signals are related to these

counters

CLK 0, CLK 1, CLK 2 (Clock Signal): These are input signals for counter 0, counter 1,

counter 2 respectively. To g i

werate delay, contents of the respective counters are decremented

ATE 0, GATE 1, GATE 2 Gate Signal) : These are input signals for counter 0,

counter 1

tr 2, respectively. To start and stop counting of the respective counter, GATE

sianalis used. When GATE signal is high, the counting starts and when it goes low, the counting

stops:

OUT 0, OUT 1, OUT 2 (Output Signal)

1, counter

These are output signals for counter 0, counter

respectively. OUT signal goes high when contents of a counter reaches to 720

itean be used as an interrupt signal for microprocessor to indicate that the counting has been

completed.

(iv) Power Supply

Vcc ~ It is connected to + SV.

GND ~ It is connected to OV.

oh

can

oe) Bee [ceo

2% puter

Sass sees

=e

=e

A ——>| onic

A

oa

Control

‘word

register

Fig, 10.22 : Block diagram of 8253/0254

‘Scanned with CamSeanner

(©) Controt Word R

This register selected when line Ap and A, are a logic 1 (AoA) = 11). It is used to wrig

‘ 3 the counter to be used, its mode and either a read oF a wig

10.23.

‘a command word which spec

‘opration. The control word format is shown in fi

>] a a] o af [9 a

Sy SGM OM

$C ~ Select counter M— Mode

$6 | 8 im | ms | my | Mode section

[0 | Select counter 0 o fo [0 | Mode 0

0 | 1 [select counter + o Tots | mois

+ | 0 | Select counter 2 x [To [ede 2

egal for 8263 = [Ts | odes

1 | 1 | Reaa-Back command for 8254 atofot odes |

(See Read operations) i ee

RW — Reaamrite

RW, | RW B00:

© | © | Counter tate command © | Binary counter 16 — bis

(See, Read operations) 1,| Binary coded decimal (CD)

© [_1_| Reaarwte fast signifcant byte only Counter (4 Decades)

+ [9 | Readirte most signfcant byte only

1 | 1 _| Readiwite least signiicant byte frst

then most significant byte

Note : Dont care bits (~) shoul be 0 10 ensure compatitiliy with fre Intl products

12 10.23 : Control word format for 82638264

10.3.2 Modes of Operation of 8253/8254

‘The 8253/8254 can operate in six different modes by writing.a suitable control word. Thes®

modes are described below :

( Mode 0 + Interrupt on terminal count

(2) Initially output will below after the mode set operation

(b) After the count is loaded into the count register, the output will remain low and the

counter will count

‘Scanned with CamSeanner

fo, When counter reaches to zero the out wll go high an

j rebated. This cn be wel aan mempsipal cere

gal to microprocessor

spe coniton 1 enable counting is GATE =.

i ig, 1026 shows tha the counting (m ~

sacporrlysopped, when the GATE is disabled and counting sas spain hen te GATE

isat logic |

ox_J | ee a ea Pe

re 3 7 ee ee

owe ae ae

eee

Bae, rararc naviesate Omer

(a) The output wil be initially high.

(b) When the count is loaded and GATE is triggered, the out signal goes low. The count

saris now.

(6) Atthe end of the count, (count reaches to zero) the out

fone shot pulse.

‘When the trigger input is applied again,

signal low: In this mode, the 8253/8254 can be used as

Yaveforms for various signals in mode 1 of 8253/8254 are shown in fig. 10.25

ut goes high. This is like the

the counter will estar counting by making OUT

‘4 monostable multivibrator. The

ux

am

‘Scanned with CamSeanner

Mode 2 : Rate Generator

This mode functions like a divide by-N counter

(@) The output willbe initially high.

(©) The output will go low for one clock pulse before the ten

(©) The output then goes high, the counter reloads the initial count and the process is

repeated

(@) The period from one output pulse to the next equals the number of input counts in

the count register.

‘The count = isillegal in this mode. IfGAT

counting.

itenables a counting; otherwise it disables

= nL

mes eS

Fig, 10.28 : Mode 2 : Rate Generator

(iv) Mode 3 : Square Wave Generator

This mode is designed to be periodic. The output of this mode is square wave signal. The

‘count value for this mode could be even or odd. ‘The operation of 8253/8284 for odd and even

‘count is different

Even Count

(a) Initially outputs high,

(b) Counter is decremented by 2 on the falling edge of each clock pulse.

(©) When the counter reaches to zero, the state of output is changed (low to high or high

to low)

(@) The counter is reloaded with full courit and whole process is repeated.

Odd Count

(@) Initially outputis high,

(b) The count is loaded, the first clock pulse decrements the count by 1, subsequent clock

pulses decrement the count by 2,

(©) When the counter reaches to zero, the state of output is changed (igh to 1)

‘Scanned with CamSeanner

Tt it is reloaded, the first cl

1) The count is » the first clock pulse decrements the count oi

jock pulses decrement the count by 2. oe Sh by Stabeewiatt

{@) When the counter reaches to zero, the state of output is changed (low to high).

{9 The counter is reloaded with full count and whole proces is repeated.

yorious waveforms for mode 3 of 8253/8254 are shown in fig. 10.27.

aSUUUU LA

je ea eet eet aed

eS aerials ee lot

la ie to ae ie

1 eee :

Fig. 10.27 : Mode 3: Square wave generator

ee et ee ee

‘Nate: Ifthe count (N) is even, N/2 clock pulses provide the upper half of the square wave and

'N2 clock pulses provide the lower half. Whereas if the count (N) is odd, the wave stay high for =,

(+ 2 clock pulses and stay low for (N ~ 1)/2 lock pulses. 5

t

(8) Mode 4 : Software Triggered Strobe 5

(@) The output is initially low.

(©) At the end of the count, the output goes low for one clock pulse:

This mode is similar to mode 2, but itis not periodic. The count is not automatic reloaded;

ace foaded again for subsequent outputs. The waveforms for mode 4 are shown in fig.

128,

‘Scanned with CamSeanner

(vi) Mode 5 : Hardware Triggered Strobe

(a) The output will be initially high.

(b) The counting is triggered by the rising edge of the GATE.

(©) The output will go low for one clock pulse at the end of count.

This mode is similar to mode 4, except that it is triggered by rising edge of the pulse at

the gate.

= J 4 eS ee See

Wns a ee Si ae

Biter clei tig! sf ltet oe e

Crete ee ri of i Pel a

ppp A ee

Ore ia ee eee cloner

Fig. 10.29 : Mode 5 : Hardware Triggered Strobe

Note : In mode 5, if another trigger pulse is applied through GATE before the counter reaches

to zero, the count is reloaded and counter will restart. This is called retriggering,

‘Scanned wih Gamseamer

PROGRAMMABLE INTERRUPT CONTROLLER (PIC) ~ 8259

The 8259 can be used by provide additional interrupts other than software and hardware

interrupts of 8085 microprocessor. The $259 interrupt controller can

@ Manage eight interrupts according to the instructions written into its control registers

This is equivalent to providing eight interrupt pin on the processor by connecting to

it INTR pin of 8085 microprocessor. Thus, we have total 12 interrupts lines by using

one 8259(8 new and 4 earlier interrupt lines) (TRAP, RST 7.5, RST 6.5, RST 5

with the loss of INTR line)

Gi) Vector an interrupt request anywhere in the memory map. However, all eight interrupts

are spaced at the interval of either four or eight locations. This eliminates the major

drawback of the 8085 interrupts in which all interrupts are vectored to memory

locations on page 00H.

(iii) Provides eight levels of interrupt priorities in a variety of modes, such as fully nested

mode, automatic rotation mode, and specific rotation mode.

(iv) Mask each interrupt request individually

s, in-service interrupts and masked interrupts.

(v) Read the status of pending interrup

(vi) Be set up to accept either the level-triggered or the edge-triggered interrupt request.

(vii) Be expanded to 64 priority levels by cascading additional 8259s.

(si) Be set up to work with either the 8085 microprocessor mode or the 8086/8088

microprocessor mode.

‘Scanned with CamSeannes

_— ;

“pat Block Diagram of 8259

Fig, 10.33 shows the internal block diagram ofthe 8259. 11 ineludes eight blocks : control

s eight blocks : contro!

idiwrite logic, data bus buffer, three re

i gisters (IRR, ISR, and IMR), prio cl

buffer: The diagram shows all the elements of a oa fad epi

locks. The fution-of thesebleels are ai follans me ee

tose, Fe

and casende

additional

4, Control Logic

‘This block has two pins : INT (interrupt) and INTA (interrupt acknowledge). The funetion

of these are

(INT (Interrupt

asserted, this signal goes high. Th

interrupt is

tis an active high output signal. Whenever a vi

sonnected to INTR pin of the

INTA (Interrupt Acknowledge) : It is an active low input signal. The INTA

interrupt acknowledge signal from the microprocessor, This is connected to INTA

pin of the microprocessor.

2, Read/Write Logic

Read/Write logic has following signals

) Ay: When the address line Ao at logic 0, the controller is selected to write a command

or read a status. This is connected fo Ap address line’of the microprocessor

RD (Read), WR (Write) and CS (Chip select) + These pins have their usual

functions.

3. Data Bus Buffer

It has bidirectional data pins (Do

microprocessor. The data buffer allows t!

status word from the 8259.

4. Cascade Buffer/Comparator

This block is used to expand the numberof interrupt levels By ‘cascading two or more 8259.

The pins associate with this block are

(CAS 0 — CAS 2(Caseade Hines) +

8259 in cascade mode.

connected to the data bus of

— Dy). These pins are

trol words to 8259 and read a

he 8085 to send con

‘These lines are used fo connect more than one

sffer) + It is used to define the 8259 as master!

(i) SP/EN Glave Programv/Enable 8

itoper

than one 8259 are use

re, with 5P/EN connected to

rates asa master. Then SP/EN pinis connected

slave, When single 8259 is used,

‘one 8259 can be

to + SV (logic 1). When more ) are high it means that the request is stored and the corresponding

IRR bit is set.

(i) All the three registers are checked by priority resolver and INT pin set high.

Gil) Microprocessor acknowledges the interrupt by sending INTA pulse.

‘Scanned with CamSeanner

When INTA pulse is received form the microprocessor the ISR bit with the highs

is set and the cor ing pee ee

priority is set andthe corresponding IRR bits reset. Ther after call instruction cod

(CD His set on pin(Dp ~ D>). Since all the RST instructions re 1 byte call a 5

are | byte cal instruction

having some vectored location

9) Two more INTA signal on the data bus are placed while decoding the CALL

instruction.

(oi) Thetwo INTA pulses are defined as that lower 8 bit address i released at the second

her 8 bit address is released at third INTA pulse. It completes

NTA pulse and the hi

the 3 byte CALL instruction,

TA pulse; the ISR bit is reset either automatically with the help of AEO!

(iy At thied TN

of

(Automatic End of Interrupt) or by a command word should be given at the en

subroutine which is determined by intialization command word

10.43 Priority Modes

Many types of priority modes are av

during the program by writting appropriate command words,

commonly used are as follows

lable with 8259. They can be changed dynamically

Priority modes which are

(0 Fully Nested Mode

iets mde the inverrustxqsiatom IRs IRqate arises emslebest © lowes

pry, IR, is having highest priority and TRy is having the lowes! pron ‘When an interrupt

itcinowledged, the highest priority request is detrnined and is Yociorl0a00 placed,

on the bus. Also any IR can be set to highest priority

SS ee Rm mn)" |] ®

DLs - 5 . ° 1 2 3

+ z

Lowest Highest

Priory ‘Pry

interrupting devices.

i) Automatic Rotation Mode =a a

rity assigned to no, of i

(eed regeives the lowest

ih ]

some applications there ean be edu served

Bis te help af ais mode, the mare stert ance. oa

Pron,

‘Scanned with CamSeanner

IR IRs IRe IR,

1 2 3 4

Lowest

Priority

Assuming that IR has just been serviced, it will receive the seventh (lowest) priority.

(iii) Speicifie Rotation Mode

In this mode user can select any interrupt request for the lowest priority. The programmer

by programming the bottom priority and fixing other priority can change any priority.

‘Scanned with CamSeanner

KEYBOARDIDISPLAY CONTROLLER - 8279

a matrix keyboard and multiplexed display.

The 8279 is a hardware approach to interfa

Software approach is also possible to interface keyboard and display unit. The disadvantage

of the software approach is that the microprocessor is occupied for a considerable amount

of time in checking the keyboard and refreshing the display

‘The 8279 is a 40-pin device (shown in fig. 13.7) with two major segments : Keyboard

and display. The keyboard segment can be connected to a 64-contact key matrix. Maximum

8 keyboard entries (codes) can be stored in the FIFO (First In First Out) RAM. Every time,

a key is pressed, an interrupt signal is generated, to request the microprocessor to read the

key code.

‘The display segment can provide a 16-character scanned display interface with such

devices as LEDS. This segment has 16 x 8 R/W memory (RAM), which can be used to read/

Write information for display purposes. The display can be set up in either right-entry or left—

entry format.

‘Scanned with CamSeanner

at

wen

slam,

37 enrusta

ee | ace RUC

A,

1

a 2

RQ Rly CLK 9.

ROL 4

Pee 5

6

1

Key iat 36 | SHIFT

da RU, ira:

§ Ay 4 pos,

i RL} 8 abs,

3 Son eseri 6 a

y FO. ‘OUT B,

WRC = our,

ba, ‘OUTB,

ee aie ours,

ii DB, OUTA,

= DB, OUTA,

08, ouTA,

0B, UTA,

a, a

8, S

A

Pi contiguraion

Fig. 137 : Pin Diagram of 8278

13.4.1 Block Diagram of 8279

The block diagram is shown in ig.

section, Scan section, Display section

1. [Keyboard Section]

The function of various pins of this section are

Se haeaaicst Tommasi nt 3st a, conpeted a IGA RD URE of

4 keyboard.

( smnr : 1

shift input status is stored.

into four major sections : Keyboard

3.8, Itean be divid

‘and Processor section.

is used {nthe scanned Keyboard. On key closure or key is closed the

‘Scanned with CamSeanner

Gil) CNTLISTB (Control/Strobe) : The status of the SHIFT key and the control key

cean be stored along with a key closure. The keys are automatically debounced, and

the keyboard can operate in two modes

(a) Two-key lockout mode : In the two-key lockout mode, iftwo keys are pressed

simultaneously, only the frst key is recognized.

(b) N-key rollover mode : In the N-key rollover mode, simultaneous keys are

recognized and their codes are stored in the internal buffer; it can also be set

up so that no key is recognized until only one key remains pressed.

[Sa Seton]

‘The scan section has @ sean counter and four scan lines (SLo ~ SLs). These four scan

lines can be decoded using a 4-to-16 decoder to generate 16 lines for scanning. These lines

‘can be connected tothe rows ofa matrix keyboard and the digit drivers of a multiplexed display.

3. [Display Section!

The

ese lines ean be used, either as a group of eight lines or as two groups of four, in combinat

‘The display section has eight output ines divided into two groups Ay ~ As and By ~ By.

‘with the scan lines for a multiplexed display. The display can be blanked by using the BD

line. This section includes 16 x 8 display RAM,

4.

[Processor Section

‘The function of various pins of this section are

() DB, —DB, : These are bidirectional data bus lines, used to transmit the commands.

Gi) IRQ: Its an acti

FIFO RAM. This

availability of data.

high signal. It goes high whenever data entries are stored in

ignal is used to interrupt the microprocessor to indicate the

‘Ag: When Ay is high, signals are interpreted as control words or status. When Ag

{goes Tow, signals are interpreted as data

(iv) €S(Chip Select) : It is an active low signal and used to enable the chip.

(¥) RD (Read) : It is an active low signal and used to read the input.

(vi) WR (Write): It is an active low signal and used to write the input.

(vii) CLK (Clock) : It is used to generate internal timing.

(vill) RESET : It is active high signal and used to reset the 8279.

‘Scanned with CamSeanner

—- WR

RD | a IRQ

Eee ee)

Data v0

Buffers [—] contro ae

RESET as,

cux|

Tntemal data bus @)

ospay |. 10x28 | | Lfconnorand|e! [ex k= keypoora

address [>| display | L 5] ~ timing FIFO/senor debounce

registers RAM || registers aM and control

Dipiay "a L

rogers |__| como | _[ecancoinir] —[Retum

i U a

‘Scanned with CamSeanner

You might also like

- 862 Microprocessor and Microcontroller Lecture 16 Interfacing @SEM2JOBNo ratings yet862 Microprocessor and Microcontroller Lecture 16 Interfacing @SEM2JOB36 pages

- 8255 PPI Pin Configuraion and ArchitectureNo ratings yet8255 PPI Pin Configuraion and Architecture21 pages

- 8255A Programmable: Peripheral Interface (PPI)No ratings yet8255A Programmable: Peripheral Interface (PPI)26 pages

- #Tutorialspoint Programmable Peripheral Interface 8255: Block DiagramNo ratings yet#Tutorialspoint Programmable Peripheral Interface 8255: Block Diagram26 pages

- The IN and OUT Instructions in The 8086 MicroprocessorNo ratings yetThe IN and OUT Instructions in The 8086 Microprocessor10 pages