0% found this document useful (0 votes)

28 views2 pagesExp 1

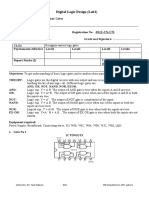

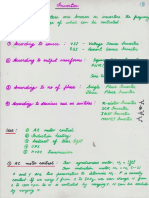

1. The document describes an experiment to study logic gates and verify their truth tables.

2. It requires AND, OR, NOT, NAND, and NOR gates to build circuits and complete their truth tables.

3. The tasks are to write the truth table for a 3-input NAND gate and complete the truth table for a circuit diagram.

Uploaded by

Rubaiyat JakyCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

28 views2 pagesExp 1

1. The document describes an experiment to study logic gates and verify their truth tables.

2. It requires AND, OR, NOT, NAND, and NOR gates to build circuits and complete their truth tables.

3. The tasks are to write the truth table for a 3-input NAND gate and complete the truth table for a circuit diagram.

Uploaded by

Rubaiyat JakyCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 2