0% found this document useful (0 votes)

175 views11 pagesAssignment 4

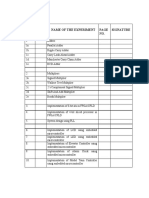

The document describes an ASIC design lab assignment involving floor planning, placement, and clock tree synthesis using Synopsys tools. Key steps include writing scripts for data preparation, floor planning, placement, power planning, and clock tree synthesis before running commands and checking reports.

Uploaded by

ruchirraval19Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

175 views11 pagesAssignment 4

The document describes an ASIC design lab assignment involving floor planning, placement, and clock tree synthesis using Synopsys tools. Key steps include writing scripts for data preparation, floor planning, placement, power planning, and clock tree synthesis before running commands and checking reports.

Uploaded by

ruchirraval19Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 11