0 ratings0% found this document useful (0 votes)

220 views55 pagesEmbedded Controller Solved Question Papers

Embedded c vtu solved paper

Uploaded by

deepakupadhyay5710Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

0 ratings0% found this document useful (0 votes)

220 views55 pagesEmbedded Controller Solved Question Papers

Embedded c vtu solved paper

Uploaded by

deepakupadhyay5710Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

You are on page 1/ 55

j

i

i

i

|

i

j

|

j

UsN

CUT TT TTT

OGESS2

Fourth Semester B.E. Degree Examination, May/June 2010

Miero-Controllers

Time: 3 hre. Max. Marks: 160

Note: 1. Ansuerany FIVE full questions, selecting at least TWO questions from each part

2. Standard notations are used.

REA

Q.1 9, Give the Besic block diagrams, uf a microprocessor end a mictcentroller and justify thet a

microcontroller is aa onchip computer. (08 Mans)

bh, What is Harvard architcomre? Show that 80S | uses Harvard arhicesrues, {06 Marks)

©. Betty discuss the feateres of 8051 micracuntoller, (06 Mavis)

Q.2 Explain the following in brief, with respext to 8OS

(i) ‘The pin that conmects the external memory

i) The port Bal kas open-drain output

(8) Asynchronous input ping of microcontrollers,

iv). The epistr thal sequencesthe ro gean exceutinn

{9} Program stains word (10 Maris)

1», Write the cirewié diagram for Port). Explain the input, oupot operations in 8081 using Port.

(1 Baris)

Q.3 a. Give the mode werd, (TMOM) and the control woud, (ICON) values ta perform the followigg

operations:

(i) Timer 0/in auto reload mode 2H

(ii), Timer 1 in mode 10H (06 Maris)

b, Explain the serial dats interrupts"TI and RU in 8051. (06 Ntavtsy

4 Name the addressing 1udes of the following instructions:

(i) HOVO A, @A + DPTR

(ii) MOL AB

(ii) MOV B, HOFF

(iv) SUBB A, 4h, (04 Maris)

«L Explin any too data taster instructions and any one arithmetic instruction in 8051, (UM Mark)

2

oi

‘Name the instructions which perform bit Jevel logical operations: in. 8051. Give an example to, They,

level logis operation,

‘irite an assctnbly program in 8051 to add two 16 bit numbers stored in extemal memory, ape,

aadltion stove the results in intemal data memory (06 Marks,

Write the result st

sd ivestion Papers

(6 Many

itement aller execution of each instruction:

Mov 81h, #30 nh

MOV RO;

PUSH 00

PUSH oo

POP

POP

Mov

RL

PoP

POP

MOVX @ DPIR, a

Werte an assembly program in 8051 fo convert

decimal number and send the result on to port

01

20

a

82

83

Yoac hb

a

HOFF h

80h

h

h

(8 Marks)

_PartR

a given two digit hexadecimal number to its equivalent

2 byte by byte.

(06 Marks)

How is ‘call? subroutine different from un internupt service routing? Give an example to show call

Subroutine’ operation in 8051 (06 Marks)

‘What are the final numbers in A, 1 and OV flag after the execution?

HOV AR, HTB

MOV OFO, #02 h

MUL AB .

Mov B, # OFZ h

MUL AB (04 Marks)

Give the magnitude of different data types used! in embedded (04 Marks)

‘Write the block diagram to show mode 2 operation of timer I, as. counter, also waite the programming

steps to perform the same,

Find the delay generated by tiner © in the following code.

the instruction overhead. What count has to be loaded in TLO and THO if delay has to be increased to

25 msec?

HERE:

AGAIN

(06 Marks}

lculate the delay generated excluding

CLR P2.3

MoV TMOD, #01

Mov TLO, #3E h

MOV THO, #5 BB h

SETB P2.3

SETB TRO

NB TEO, AGAIN

CLR TFO

cuz B23 (08 Maris

Solved Question Papers O-3

©, What is asynchronous serial communication? Explain the different modes of serial communication

in 8051 (06 Marks)

QT a Write 8051 °C’ program to receive bytes of data serially and put them in PI. Set the baud rate as 4800,

§ bit data and one stop bit (06 Marks)

b. Explain the different interrupt vector addresses in 8051, (04 Marks)

Write a 8051 °C’ program that continuously gets a single bit of data from P1.7 and sends it to P1.0,

hich creates a square wave of 200 ys period on pin P2.5. XTAL frequency = 11.0592 MHz.

(10 Marks)

Q8. a. Interface LCD to 8051 and write a 8051 assembly/805 1 ‘C’ program to send *M’, ‘A’ *S’, ‘T’, “E’, ‘Re

to LCD display (10 Marks)

b. Show the interfacing of a stepper motor to 8051 and write 8051 assembly/805 I °C’ progeam to rotate

stepper motor 2 rotations clockwise and one rotation anticlockwise with appropriate delay.

(10 Marks)

)

e

3

w

to

ks)

Fou

‘ourth Semester BB. Degroe Examination, May/June 2010

PAREA

tran

md

athe

et

legeun

ai

Begone

insta a]

| [Pron se Ss es]

A microcontroller ig 2 general purpase devie, but one 0

\ iro ee deve, bul one Wha: mean fee

saleulaions-onthoae dra, and contol seinen! ase on iscalelaiune Se end

‘ary in dats size from 4 10 32 bits. Bit uns are produced an huge valance for veg ee el

and. 8bit ynits arc the most versatile. 16+ and 32-bit unig arp used in high cee PReations,

processing applications, seeped corte aa

Signal

1. ob. Harvard architecture:

Gi) (uses separace memories Sor program and data

ii) ‘There isin need to have lime-divisina multiplexing

(iii). ‘There isa great amount of peratletisn”

(iv), Fes Intel MCS-S1 family

&

Lb

Goivwrt uation Papoce +5

Refer 1b of Jan/Feb 2000.

(i) The pin that connects the extemal memory:

UA. Avis the program store enable pin (no. 29). It inan active low-auipat signal, When it has to access

the program code ftom an external ROM, it ix connected to the enable pin of the ROM chip. ‘To oecess

the program code, EA should be guarded. Then PSEN will go low to cnablethe external ROM to place

byte of program code on the dats bus

(hi) The port that has open drain output:

Port 036 an open drain. Hence, pull-up resisters arc required, With resisters connected, to make it an

input por, the port should first be programmed hy writing | 10 all bits whose corresponding pins act as

input

(iii) Asynchronous input pins of micracontrollers:

B,D & De The 6051 has sevial data coramunication eirult that utes register SBUF to hold data.

Register SCON controls data communication, registers PCON contwols data rates, and pins R,D and

T,D connect to the serial data network,

(iv) ‘The register that szquances the program execution:

PC: Program Control

{Lis an S-bit register, which can holds the address of the next instruction to be executed next.

(¥) Program status word:

PSW: It is an &-bit register

it has 4 flags that respond automatically to the averconmes of month operations and 3 genera-purpore

flaps which can beset to | or 0 by the programmer at desired. The fags awe CY-cary flag, AC-auallary

carry flag, overflow oraverflow flag. and P-Parity flag.

Features of Port 1

|). Pert I pins have no dua! functions

2. The port occupies a grand total of spins

3. Inmay be an input oF output port

4. is in comrast to port 0

5. ‘This port does not need pull-up sesisters

Covet gals

Fad ae

rts te Corto

‘i |

6 Soived Question Papers

3

atid

(i)

a

(ii)

(id)

ww)

3. (a)

&

4 a. (a)

(b)

©)

4. be Ext

Timer 0 in auto-reload

ron =[o fo [oo [o [0

Vimer 1 in mode 1

rwop= {0 [o [o [1 [0 [o

MOVC A, @A + DPTR Indexed addressing mode

MUL AB Register addressing mode

Mov B, #OFFH Immediate addressing mode

SUBB A, 45H Direct addressing mode

MOV A, R,

‘The contents of R, are copied into an accumulator

ex: A, = 2011, R= 07H

MOVA,R,

Afler the execution af the instruction the contents of R, ate copied into A, that is, the contents

of A consist of O7H.

MOV SIH, #30H

‘The value 30H is stored at location $141 in data memory.

ADDA,B=>A-A+B

‘The contents of both A and B are addled, and the result is stored in accumulator A.

Bit-level AND

ANL C,b AND G, and the addressed bit b, store result in C.

ANL CAND Cand the complement of the acess bit, tre result in C, but b isnot altered

Bit-level OR

ORL C, b OR ¢, and b; store result in C;

ORL G, fb OR cand complement of bz store result in C, but bis not alter

Complement bits

CPL C complements the carry flag

CPL b complement burt b,

ex: CLR C; clears carry flag; cy = 0

SETR 01H; bit address O1H =

ANL C, ‘0]H; AND C:and complement of location 01H =6,

jeral memory sddress 1500H: O41

150111: 02H

Movx BPTR, # 1500H

MOV A, @DPTR

Ne DETR

MOV B, @DPTR

ALD A, B

MOV 45H, A; Store the result in 458! location (interna! memory)

ND

”

Sohed Question Papers OFT

MOV 81H, #30H Store 30H in stack pointer sp

Mov RO, HOACH —¢ Store OACH in register RO

PUSH 00 Store vahue of RO in stack at 3170

PUSH 00 * Store value of RO an stack at 32H

POP 01 + Copy the value af top of the stack 32H in Ri andl decrement stack by T

POP 80H Copy the top of the stack inte port 0. (OACH)

mov A, SOPFH 5 A=OFFIL

XRL A, BOE ASA contents of SOH

= 53H

ROP 82H } Retrioye $24

POP 834 ; Retrieve 83H

MOVX @DPTR, A. 5 Store accumulator value in OPTR

PARTB _

a

ons 00008 :

OW A, A0PFE Ax OFF

Mov B, #10 B10

piv AB 5 A=AB

sou p2, 8 1 Send the remainder in 1} 40 port

row B, #29 5 Lat B=10

DIV AB Sond the remainder in B to port

wav pa, 8 ‘Ais sent to port 2

Nov p2. A

aD

bh, Refer 3a of Jan‘Feb 2010.

©

vov a, #78H

Mow Fo, HO2H

vB, HOFEH

UL AB

‘The fl values of A = MEL

“tH

a

AaTBII

OFO which is B= 02

; AWAKE

, B=OFEH

A=AxB

Range

Oi

ae |

~ aoe |

=SET6Bi0 #32767

O-8 Solved Question Papers

bw Timer |—> | Timer 0

| cate | 1Jo}olo 0 feu

twop=| 0 | ed

+ mode 2 is auto Reload.

Programming Steps: ‘

Set timer T= 1.

Initialize TMOD value of mode 2 and timer | that is, 60H.

Initialize the THI and TL1 with OOH.

Set TRI= 1 ;

Make a loop so that TL gets increments and then transfer it to port pl.

‘Wait until the timer flag is set (TF 1 = 1),

Stop te timer.

Clear the TF flag,

Repeat from step 2 for the next delay.

een eueune

CLR P2.3

HERE: NOV TMOD, 401

wov TLO, #3EH

OV THO, ¥oneq

SETA p2.3

STB TRO

AGAIN: JNB TFO, AGAIN

CLR TFO

cLR TRO

CER P2.3

From the above program:

Initial value ~

ysl frequency

12

Max value ~ Required delay x

= DB3E -1= FFFF ~ Required day x OO

Remived delay =

9s oF the shove camo! genet 19 me. To generate 7S, heen vu willbe

(FRRF—x+1)x1 085 s=25 19° :

x= 42495 {

2=ASFFA,

6 ©. Serial data transmission using ASCH becomes so universal hat sp

Asynchronous Receiver and Transmitter (UART) were developed to perform the tasks of

bit parallel data byte into a 10-bit serial stream and converting 10-bit serial data into

byte. When the second-generation 8051

The 4 modes are as follows:

Mode 0: Shift register mode (8 bit)

ecialized integrated citcuits, universal

onverting an

an $-bit parallel

He was designed, the UART became a part of the circuit,

Mode 1: Standard UART moste (8 bit)

Mode 2: Maliprocessor fixed mode (9 bit)

Mode 3: Multiprocessor variable mode (9 bil)

‘Mode 0: Shift register mode;

data and the shift clock

crystal frequency.

«Timer 1 | Timer 0

rwop= [a] o[1 [0 |o[o]o[0|-201

(Timer | and mode 2)

frequency

Count THI = wants nnd

Cons baud rate

=4

include < reg 51.n>

Void main ()

{

unsigned char *;

pl = OXFP;

THOD = 020;

‘TH = OxFA; // -6

‘SCON = 0X50;

pa

while (1)

}

lb,

Interrpt OM ocation Function

RESET. ‘00H anioads PC with 00 |

INTO |___ ows External hardware itoruplO

To Timer O interrupt

INTH 00n3H External hardware interrupt

i _| ‘DOIBH Timer }interwupt

R&T! ouz3H Serial communication interrupt

Sctved Question Papers 9

Made 0 is not suitable for the interchange of data between 805 Ijic, Mode 0 uses SBUF as an 8-bit shift

ropister that transmats and receives data on port 3.0 while using pin P3.1 to output the shift clock. The

re synchronized using the six internal me states, and even for me using the same

0.10 Saved Question Papers

he

Considering Timer TL and mode f

Timer 1 | Timer 0

mon [ooo ol] o| [o]= 108

Pi p10} —[Doveez

Lo.

_ —

z08

jeje

T= Toy + Tope = 100-4100= 200 prs,

Tow = Tare = 100 ps

Talal valid 1= Mig vale Regains EL feet

FREF 1001078 x 0592 410

n

aa

°

;

ASRATER ;

ping

* HDD44780 (Hitachi) is an alphanumeric LOD panet

© Itconsists of 16 characters and two lines,

C program to display “Master” on LED panel

#fincludecregs1.h>

Str ldata = 0x60;

abit rs = 7377;

Bbit rw = P36;

Bbit en = P3975;

Bbit busy = PO*7;

void MSDelay (Unsigned int);

void Ledemd (Unsigned char);

void leddata(Unsigned char};

void Ledready() ;

Unsigned char idata mag[6] - (MASTERY);

{

i

{

‘old main ()

Ledemd (0x38) ;

ledema (0xde) ;

Ledema (8x01) ;

Ledemd (0x06) ;

Acdemd (0x83) ;

for(} = 0; 4<6s jt)

leddata (msgl}]) 3

}

while (i) {

edema (0x03) ;

}

}

void Icdready()

(

busy

vs = 0

rw;

while (busy == 1)

{en = 0;

mspelay (i) +

en =

}

return;

J ta edema (unsigned che}

{

dedready (1;

]data = value;

ys = 0

rw=0

en = 1

MgDelay 1);

en = 07

return}

| a Lnddata funsigned char!

{

edready{}:

jdata = value:

rs = li

aw = 0;

en = 1;

usDelay (1);

en = 0;

retucn;

void N8Delay (unsigned int value)

{

ungigned int x. ¥:

for (x = 0; % < 90; x44)

forly = 0: y < values yeeli

}

Solved Question Papers QH11

42 Solved Guestion Papers

Bb.

Pont

Step Number

1

Clockwise

direction 2

3

4

‘include

void main()

{

Unsigned int count;

count = 2;

while (count

PO = 0x66;

MSDelay (1);

PO = Oxce:

MsDelay (1) ;

0x99;

ay (1);

PO = 0x33;

MSDelay (1);

count --;

}

i£ (count

{ PO = 0x33;

MsDelay (1) ;

PO = 0x99;

MSDelay (1);

PO = 0xec;

MSDelay (1);

PO = 0x66;

MsDelay (1);

2i{

Winding A

1

1

0

0

‘Stepper motor

Anticlockwise

direction

Microcontrollers - Jan. / Feb. 2010

Semester - IV (EC/TC/EEAT/BM/ML)

‘Time: 3 hrs. ‘Max. Marks: 100

Note: Answer any FIVE full questions selecting at feast TWO questions fron: each part.

_ PART.

Qa 9. What is a microcontraller? With 2 neat block diageam explain, Hancint architecture, Distinguish

between i) Microcoutrollr and microprocessor, and i) Harvard architecture and Von Newmon’s

architecture. (Marks 10)

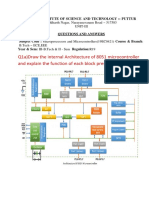

bs. With a neat block diagram, explain the function of eaeh block of 8051 microoonirallerarchitectre,

(Marks 10)

2 a. Mention the addressing modes of 8051 microconivole, Fxpiin each of them withan example for eneh.

(Marks3)

1b. Cortectthe follawing instructions if Found to haveany wrong syntax Explain the gperation of corrected

instructions

i) MOV #C, 0A ii) MOV A,RSI ii) MOV A, @RT

iv MOV 0346H, @RO vi XCHG B, @RS (Marks)

ee Show: the stack 0

sequence of operatons.

mov SP, #70H

mov RS, #30H

affooted aftereach step of the fol

P contents aud wentents of regis

Mov A, #480,

ADD A, RS

MOV RS, A

pusH 4

BUSH 5

POP 4 (Marks 7)

3 With the relevant figure wtea sequence of events tna occur in 8051 migrogoatrotler when the CALL.

and RET instructions arcexecuted «Marks 6)

tb. Wane an ALP in 8051 to find the largest number among the 12. 8-bit numbers stored in the intersal

RAM. (Marks?)

\

\

N

0-44 Solved Question Popers \

\

= (X2 + ¥2) where X1

¢. Writean ALP ip 8051 to perform the following operation: Z suo sre 2 ) whee a h

and 2 are the 8-bit hexadecimal numbers stored in the RAM loc Mente

addition and assume that each addition result with 8-bit number, 2

(Marks 6)

a, Disc es in 8051C,

Qed a, Discuss the data types in 805 / cteee

bb. What are ihe ways to create time delay? Discuss the factors affecting the accuracy of the ia de. .

Wr function in C to create a time delay. and yo

7 ‘ILand display the bytes on pl and p2,

©. Write aC program in 8051 to convert packed BCD 0x39 to ASCII and display lanl

PART-B

Q.5 a. What is te difference between timer and counter? Explain the function of each bit in the TOP. »

Write an ALP to generate square wave on pin PLS of 500 Hz (approximately) with a subroutine to

b,

provide atime delay of 30.38 pts using timer 0. Assume that erystal frequency of 8051 is 11.0592 Hz.

(Marks 10)

©. In what way timer/counter mode 2 programming is different ftom mode 0 and model? (Marke 6)

Q.6 a. Explain fall duplex, half duplex and simplex serial data transfer, (Marks 6)

b. Write the steps required for programming 8051 to transfor data serially (Marks 8)

¢. Writea C program for the 8051 to transfer the letter “C* serially at 9600 baud continuously. Use 8-bit

(Marks 6)

data and | stop bit

Q7 a, Whatare interrupts and interrupt subroutines? Exphin the interrips that are present in 8051?

(Marks

B._Discuss whit happensit interrupts INTO, INT] and TF ae activated a he same time, Assume priority

levels set by the power up reset, Program the IP register to assign the highest priorty toINT and then

discuss what happens if INTO, INT1 and TFI are activated at the same time, Assume that external

hardware interrupts are edge triggered. (Marks 6)

What a level iiggered inierrup? How to gt he edge wiggered interrupt? Explain the procedure to

Semple the Jo level viggered interrupt and edge wiggered interrupt, (Marks 8)

8 4. Explain, with block diagram step by step procedure involved wo interface 4 x 4 matriy keyboard with

8051 (Marks 10)

b. Discuss interfacing of ADCU8O4 with 8051 using ting diagram for ADC. (Marks 8)

OS

Microcontrollers - Jan. / Feb. 2010

Semester - IV (EC/TC/EE/IT/BM/ML)

_PARTA

1. a (ii) Difference between Harvard and Von Neuman’s architecture:

Horvard architecture |Von Neuman’s architecture

fa. Ituses separate memories for a. Itusesa single memory for

_program and data memary. pragram and data memory,

|b. There ismoneed tohave “time |b. Itrequires “time division

division multiplexing.” nut plexing.” _|

© Thereise greater amountof | ¢. Thereis no need to have

“parallelism.” “parallelism.

3, Eg. intel MCS-51 family @, Eg.: Motorola —63HC11

mmicrocontrolier.

1. b. Block diagram of 8051 microcontroller

heres

and | —{rsvi] = fet

Jogic unit BL ear

Is fee

B BI Lr

|

fp __

EE =v)

oPia a

[Posancore] [comor | “}

| [pow] |] fypewe

| eo

| (Se

ears ese —— AeA:

|} [o}-—8

Spacet || [B| _|fz -—Intoat conor

ci-fpien aa incon | [5] | Satatcns

e_| bap aacressble| | taer — FO,

PSEN— system |

XIALI| neve |

TAZ mers |

ESET

vee

Data)

no] Buttes |

O48 5;

2a

2b.

olved Question Papers

Explanation of architecture

(i) Bight-bit CPU with registers A and BF

Jit Arithmetic and Logic Unit

8051 consists of an

arithmetic and logical operations;

(ii) Program counter and data pointer

3051 has a 16-bit program counter, tis wsed te

The data pointer consists of a high-byte (

adress of extemal memory.

(iii) Stack pointer:

the registers are A,

(ALU). It has 8-bit CPU registers that per

B, PSW, PC, DPTR, and SP. form

(hob the address of the instruction to be executed next,

(OPH) and a low byte (DPL). It is used to hold a 16-bit

‘The registers are used to hold the internal RAM address, which is 8 bit wide and is increased before data

are stored during PUSH, POP, and CALL-instructions.

(iv) Internal RAM and Internal ROM

Intemal ROM has 4kB of internal ROM with acd

(@) Four registers have 128 bytes: consisting of 4 register banks and

(b) 16 bytes which may be addressed at bit level,

(¥) Control Registers

}000H to OFF FH, Internal RAM has 128 bytes.

+ containing eight registers,

In 8051, TCON, TMOD, SCON, PCON, TR, and IP are control registers,

(vi) Program Status Word (PSW)

PSW isan 8-bit register, it contains 5 Mags such as camry fla

flag, end user flag and two bits to select the register bank,

(vii) Oseitlator and Clock:

8051 has 12 MHz oscillator clock frequency. Each,

‘each stage lasts for two oscillator periods,

Refer 2a of July/Aug 2009

ja MOV aC, On —Wrong

MOV ¢, #oR —Conrect

jl Mov a, Rt — Wrong

NOV A, Psw.4 —Correct

tothe PSW.

Copy data fram RSI to register A,

g, auxiliary carry flag paring flag, overflow

phase of operation of 8051 lasts for 1 period and

[li wow a, @ 7 —Coneet

tosegister A

Copy the contents of address of R?

[W) Mov o346H, «Ro — Wrong

|? ieee ea Wrong

NCHS A, oR2 —Comeet

[indirect addressi

and address in R3.

We cannot make use of RO-R? far

Exchange bytes between register A

Solved Question Papers Q-17

Operation

vow SE, #70H | SP & 70H Copytheimmaiate data 70H tothe SP.

mou RS, #308 [Rb & 30H Gopy theimmadiate data 30H to RS

Nov A, Haan | Ac 44H Copythe immediate data 44H to A.

ADD A, RS ‘Ae 44/30H ADD A and sogistr FS, and store rasult in A.

MOV Ra, A Ru c= A & TAN Copy the accumulator value in Ra

PUSH 4 TH & RaCopy the AA into stack of location 71H; SP

incremented

PUSH 5 TPH & RS Copy BH ino stack o location 72H; SP is

incremented by one.

PoP 4 FR. (72H) Copy the contents of lacation 72H into Ra; SP

is decremented by one.

1. When a subroutine is called, the conten of the program counter are stored on the stack and the

program execution is transferred to the subroutine address,

When an RET instruction is executed at the end of the subroutine, the memory address stored on the

stack is retrieved and the sequence of execution is resumed in the main program.

siboutine

1

Newt instruction of CALL

Alii

‘The programming technique of subroutine calling another subroutine is called “nesting”, When =

subroutine calls another subroutine all return addresses are stored on the stack.

4, Stack pointer register most be iitaizd perfectly atthe highest memory location of the R/W memory.

S$. CALL. insiruction should be used in the main program accompanied by RET instruction in the

subroutine,

ORG 0000H

SuMP 30H

ORG 30H

MoV R3, #OCH

Mov pprR, #40001

Mow A, @DPIR

MOV RI, A

BACK: INC DPTR

Mov A, @DPTR

CLR C

Mov R2, A

SUBB A, RL

Sc SKIP.

48 Solved Question Papers

Mov A, R2

Mov RL, A

SKIP: DINZ R3, BACK

HERE: SUMP HERE

END

ORG 00H

SUMP 30H

ORG 30H

MOV RO, #058

MOV DPTR, #9000H

ACALL ADDN

MOV A, R2

MOV B, R3

MUL AB

HERE: SUMP HERE

ADDN: MOVE A, @DPTR

MOV R1, A

INC DPTR

MOV A, @DPTR

ADD A, RL

MOV R2, A

INC DPTR

MOVE A, @DPTR

MOV R1, A

INC DPTR

MOVE A, @DPrR

ADD A, R1

j MOV R3, A

RET

4 a. Refer Sd of May/June 2010

4. b. There aretwo ways to ereate atime delay:

(a) Using a simple loop

(b) Using 8051 timers

Whe loops are used to create time delays, the followin

1. The number of machine eycles ard the mumbs

instruction to instruction

2 The enystal frequency connected tothe X1 — X2 input pins, The duration of the clock period for the

machine cycle is a function ofthe crystal frequency,

3. The time delay is affected by the compiler us

program to assembly language program,

ig factors should be considered: i

er of clock periods per machine cyele vary from

sed in C program. The program length varies from (*

#include

void main ()

unsigned char x,y,z;

Solved Ovastion Papers Q-19

unsigned char mybyte = 0X29;

inybyte & OXOF;

x/0X20;

mybyte & OXFO;

yeyoa

p2 = y/0X30;

| }

PART-B

| & a. Thetimers used to generate time delays and counters are used to count the events happening outside the

rierocontrollers.

TMOD register

+ Itisan 8-bit register

» The lower 4 bits are used for timer 0, and

the upper 4 bits are used for timer 1

Timer 1 te — Timer 9 ——+

caw [er [ar] wo| Ga | oF [wi Poo |

Gate: Gating contol when st timexeountris enabled only when INK pin is high and TR pinis set

C/T: Set for counter and cleared for time.

MI and MO are used for mode selection

wn | mo | Mode Operation

o [lo 0 1B-bittimer

ofa 1 ‘b-bittimer

1 | 0 2 | Bebit auto reload |

1 [4 3_| Splitstimer mode

Se

l Mov TMOD, #01

i ERE: MOV TLO, #E3H

Mov THO, HFFH

CPL PL.5

ACALI. DELAY

SaMP HERE

| DELAY

sarB TRO

AGAIN: JNB TFO AGAIN

CLR TRO

cue TRO

REP

Calculation

1, 3038 ps 1.08 ms = 26.12

2. 65,536 — 28.12 = 65507.8

3, Hex equivalent value is FFE3H,

0.20 Solved Question Papers

§, ©. Itshould be emphasized that mode 2 is an 8-bit timer. However, it has an sloroalng capabity,

°° Sto reload, THs ode vith the nia ent, anda copy of tis gen tT This teoating ena

TH unchanged wielding o opyof the orginal val, It allows enly values oF 00 to FF to

loaded into the timer’s register TH, and it will go back to step 4; but in mode 0 and mode 1 program.

ming, it will go back to step 2

i tk

xu |_.e Overtow

| swe as tag

cit=0

Te ges high

when FF-> 0

xm. | [ae

>PR-HE]

lo

Fig.2

‘The difference between ode 1 programming and mode 2 programming is as shown above in Figures 1

and 2. In mode 1 progéamming, it counts up until it reaches its limit of FFFFH when it rolls over from

FFFFI to 00001; but in mode 2 programming, it reaches its limit of FFH to 00,

6. a, Simplex communication: Here a line is dedicated for transmission. Always, the transmitter sends data

viver receives data such asthe printer.

Transmit Receiver

Half duplex communication: Here a communication link can be used for either transmission or

reception. Data are transmitted in only one direetion at a time. i

Tee jf ae]

WW

L/\

Receiver —]Tanseniter

Fuis dupiex communication: if une aaiz are wansmitied im both ways at the same time, then 1t

is a fall duplex communication. Here transmission and reception can proceed simultaneously, This

communication link requires two wires for data one for transmission and one for reception.

=| Receiver

“Tanssitler

Recover le Transmiter

6. ', In programming the 8051 to transfer character bytes serially, the following steps should be taken.

‘The TMOD register is loaded with the value of 20H, indicating the use of timer | in mode 2 (8-bit

auitoreloaded) to set the baud rate.

b. The ‘TH! is loaded with one of the values to set the baud rate for serial data transfer.

‘ON register is loaded with the value 50H. indicating serial made 1, where an 8-bit data is

ed with star and stop bits

c. The

6

7. a. Interrupt is an input

Solved Question Papers Q-24

a

TRI is set to 1 to start timer 1.

Lis cleared by the “CLR TI” instmetion.

‘The character byte to be transferred serially is written onto the SBUF register.

The T1 flag bit #s monitored with the use of the instruction “JNB TI, XX" to see whether the character

has been completely transferred

To transfer the next character, goto step 5,

fincludecreg51.h>

void main ()

{

TMOD = 0X20;

THL = OXFD;

SCON = 0x50;

TRI = 1;

while (1)

{

SBUF = °C";

while (TI = = 0);

Tr =0

)

}

to a processor that indicates the occurrence of an event. The processor responds to

an interrupt by saving the current machine status and branch to service the interrupt, and then it returns

tonormal execution mode, The interrupt subroutines are located in the interrupt vector address. When

an interrupt event occurs, the contoller executes an LCALL toa specified location ealled the interrupt

vector address in program memory.

The 8051 has 5 interrupts

Interrupt source Symbol Interrupt vector addvess

Exemal event on INTO | 60 OD03H _|

Timer overliow ro uve

vernal event on INT IE 13H

Timer t overtiow | TFL wore 7

| Setialcommunication | ls T ‘naa

7. Bb, If these interrupts are activated atthe same time, they are latched and kept intemally; then, the 8051

it in sequence. Therefore, when the three interrupts just mentioned are activated, [EO (Extermal

interrupt 0) is serviced first, then timer 0 (TEO), and finally IE

Extennal interrupt 1).

MOV IP, #0000108; 1P-2-1 toassign INT higher prierity. The instruction “SETRIP.2" also will

do the same thing as what was just mentioned, as IP is bit addressable

‘The instruction assigned a higher priority to INT] then fo the others: therefore, when INTO, INTL,

and TEO interrupts are activated at the same time, the 8051 serviees INT | first, then INTO, and finally

‘TFO. This is due to fact that INTI has a higher priority than the othet tive due to the instruction '> the

F e IP register 0.

step just mentioned, The instruction inthis step makes both the INTO andl TFO Bis im the TF Fs

Asa result, INTO is given a higher priority over TO.

0-22 Solved Question Papers 2

ilar to all LO port pins) ye

r Pp ly high (similar to is) ani ‘s

he level-triggered mode INTO and INT} pins are normal _ :

tone ie) i ai them, riggers the interupt. Then, the micraconeolle stops whatever .

doing and jumps to the interrmpt vector table to service the interrupt This is called a “level-triggered™ oy

“Jeyel-activated™interupt and isthe default mode on reset of the 8051. /

% To make edlge-riggered interrupts, we should program the bits of the TCON sai The TON

register holds, among other bts, the 10 and TTY flag bits that determine level- or edge-triggered mode

of the hardware interrupts

Sample the low-level triggered interrupt:

Pins PS.3 and P3.2 are used for normal 1/O unless the INTO and INT! bits in the IE register are enabled.

Aer the hardware intempt in the TE register ae enabled the controller Keeps sampling the INT pin for

« low-level signal once each machine eycle, According to-one manufacturer’s data sheet, “the pin must

be hetd in a low state until the start of the execution of ISR.” |

However, on activation ofthe interrupt due to the low level, it should be brought back to high before

the execution of RETI,

Sample the edge-triggered interrupt: In edge-triguered interrupt, the exiemal source should be

held high for atleast one machine cycle and then held low for atleast one machine cycle to ensure that

the transition is seen by the microcontroller.

me _ i

machine j

“ar Seas? | TNT py |

Teles i

|

8. a. The following steps are involved in detecting the pressed key: {

Yoo — —

ea o ;

ime aE

5 de} 4K :

| ad = ‘Nh

de de

1 - =

x 3

| ‘Nth —

| yy

22 & = Wh

Patt

(ou

a)

Pox

tn)

The receive lines are connected to port 0; the scan lines are connected to port 2,

“The receive Lines are connected to AND gates; the output is connected to INTO.

‘The 8051 is configured to accept external interrupts at INTO.

Software wires writes 0's to sean Lines at port 2, and 1's to receive lines at pot 1.

A pressed key generates alow signal at INTO, thereby causing an intemupt.

Interrupt routine fist calls a delay to prevent key debounce errors,

The receive lines in port 0 are reac into register RO to identify the row,

8. Software writes Is to scan lines at port 2

1

2.

4

5,

6

and 0s to receive lines at port 0

Solved Question Papers Q-23

4, Read the scan tines connected at port 2 into register RI.

10. Asingle key pressed will generate a single ‘0° in RO and a single ‘O"in RI.

11, The corresponding row and column identified refer to the pressed Key.

& by Analogs to digital converters are widely used for data acquisition, Most ofthe signals are analogs in

ature and, hence, an ADC is required to translate the analog signals to digital signals

ADC 0804 1C is an S-bit paralle} ADC in the family of the ADC 0800 series.

Following are the steps involved in data formation by the ADC O84 chip.

Step 1: Make CS = 0, and a low-to-high pulse to pin COR to stat the conversion

Sten 2: Keep monitoring the INTR pin, HTNTR is lo, the conversion i Brished and we can proceed

to the next step. If TNTR is high, keep polling until it goes Tow.

step 3: After the INTR becomes low, we make CS= O ands high-fo-low pulse to the RDFa get the

data at the ADC 0804 IC chip.

ep

wa i —

wa ‘Start comeraion

ead ofeonersion

av .

y

a L

CRE OY are "

Ee TS ck =I ‘1

) 4 Wig? | 0 1.280 su

a | i

Wels) low

2

Mint pot

soe

| Ds est — =

Lt xo} —}

‘Time: 3

Note:

Qua

b.

Q20

b.

Qs

b.

Q4e

b.

c.

Microcontrollers July / August 2009

Semester «IV (EC/ TC/ EE/ IT/ BM/ ML)

th Max. Marks: 100

“Answer any FIVE full questions choosing at least TWO questions from each wait.

ARTA |

Define microcontroller and differentiate the RISC and CISC processors. (Marks 5)

With the neat block diagram, explain the architecture of 8051 (Marks 10)

Show the neat schematic interface 8 K external data RAM to 8051 (Marks 5)

What is addressing mode? Explain different addressing modes with examples, (Marks 9)

Specify the memory area for bit level logical instructions used in 8051 and list bit level logical

instructions (Marks 5)

Write an Assembly language program to add two input data’s of 16-bit result in three different

addressing modes, (Marks 6)

Explain the following instructions with their fonction byte and cycle used:

i) CINE dest, source target ii) ACALL target

iti) DINZ R,, rel iv) SWAP A

vy) DAA (Marks 10)

Explain the different types of jurap instructions in 8051 (Marks 6)

What is interrupt? List different interrupts using 8051 with their ISR address, (Marks 4)

Write a C-program to toggle all bits of PO and P2 continuously with 250 msec delay. Use inverting

operator. (Marks 8)

‘What is data serialization? Explain different types with examples, (Marks 6)

Write a 8051 C-programm to conyer a given hex-data OFFI. into its equivatent decimal data and display

the result digits on PO, PI and P2, (Marks 6)

Solved Quostion Papors 25

QS a Explam T mod and T con registers with its bit pattern.

(Marks 8)

»

yplnin mode-2 programming with neat sketch and specify the program steps. (Marks 6)

} Assuming that clock pulses are Fed in to Ply TH, wtite a program for eounter-1 in mode? to count

pulses and display the sinte of TL count on P2.

(Marks 6)

6 a, Explain RS-322 hand shaking signals and specify the purpose of max-232 while interfacing

(Marks 7)

bb. Write 8051 program to transfer serially the message “VTU BELGAUM” continuously at band rate of

9600. (Marks 7)

& Explain the importance of TL and RI fag, (Marks 6)

Explain IE and IP registers with their bit patter and show how priorities change with example.

(Marks 19)

bb. Write $051 interrupt progeam to do the following:

) Receive data serially P2 onc! sent itta PI continvously,

ii) Maike timer-0 to generate a sqqnare wave ofS Id frequency af port PO.L. Assume XTAL— 11.059

Mil.ata band of 9600. (Marks 10)

Q8 a. Explain the registers and pins of LOD and write an ALP to display message “HELLO” on LCD

displays, (Marks 10)

Desorihe the 051 connection to stepper motor and write-an Assembly language program to rotate the

motor clockwise for 180°. Assuming motor specification 1.8°/step. (Marks 10)

Microcontrollers July / August 2009

‘Semester «IV (BO/'TC/ EE/T1/ BM/ ML)

1. a. The prime use ofa micmcontrolleris to contral the operation of a machine using a fixed program that is

stored 1 ROM which does not change over the life time of the system.

| RISC

cis

1. Simple instructions taking one cyle

1. Complex instructions taking mutiple cycles

2. Nery few instructions refer memory

2.Mast ofthe instructions refer memary

3. Instructions ate executed byharch

[4 Fred-formatinstrustions

Few instructions

3. Instructions are executed by microprogram

5. Many instructions

6. Muliple register sets

5. Single resister'set

[7 tHahiy pipelined

7.Not pipelined

1. b. Refer Ib of JanFeb 2010,

RAM Starting address

RAM Ending address

‘Dy Anz Ag

ax AM

2,

Solved Quastion Papers O27

a, BOSE uses 4 addressing modes inorder to access dala,

a. Immediate addressing mode

b. Register addressing mode

¢, Direct addressing mode

Indirect addressing mode,

{a) Lmmediate addressing mode:

The siraplest way to ect data toa destination isto make the source ofthe data a part of the opcode. ‘The

sala arethen immediately available as a part ofthe instruction itself

When the 8051 executes an immediate data move, the program countes is automatically incremented

to point to the byte following the opcods byte in the peogram memory, Whatever data arc found are

copied tothe destination address.

(b) Register addressing mode: * ss

jn this mode, rewisters are used along with the instructions. Rogister A, DPTR and RO to RT may be

named 03 a part of the opeode mnemonic

ex: MOV AR,

(©) Direct addressing moder

Th this addressing mode, address of the operand is directly specified in the instruction itsc}f, All 128

hhyies oF the internal RAM and the SFiRs may be addressed directly using single-byte address assigned

to cach RAM location and each SFR,

ex: MOV A, 54H (or} MOV A, SBUF

(d) Indirect addressing mode:

The indirect addressing mode uses a register to hold the actual address that will finally be used in the

data mae; the register ilsel Tis nor the address, but rather a number in the register. Indirect aklressing.

for moving opcodes uses registers RO or RA, offen called a data pointer, to hold the address of ome of the

data Jocations in RAM from adkdress 00 to FH.

“The memory area for bit-level logical instructions isin the internal RAM byte address 20H to 2FHL

ANL sb 5 AND « and the addressed bit; put the result in ¢

AetLe, th , AND

void NSDelay(unsigned int);

void main()

{

PO = OX5SH

P2 = OX55H

While (1)

{

BO = -PO;

P2 = -PO;

MSDelay (250);

}

}

vel MsDelay (unsigned int itime)

unsigned i, 3;

for(i = 0; 4 < itdme; ist)

for(j = 0; j < 1275; j¥*);

}

4. b. Serializating data are a way of sending bytes of data one bit ota time through a single pin of the micro-

controller. There are 1wo ways to transfer a byte of data serially.

{i) Using the serial port, When using the serial port, the programs have very limited control over the

sequences of data trans

(li) The second method of serializing data isto tennsfer data one bit time and control the sequence of

data and spaces in between them, In many modern generations, of devices such. as LCD, ADC, and

ROM are serial versions.

Ex. L: Write a € program to send out the value 44H serially one bit at time vin PLO. The LSB should

20 out

include

Sbit Pibo = P1*O;

abit req ALSB = ACO;

Void main ()

{

Unsigned char conbyte = 0x4;

Unsigned char x;

CC = Conbyte;

Solved Duvestion Papers (+31

Por (x = 0; % © By xea)

\

PibO = reg ALSB:

ACE = ACC o> 1;

}

}

Ex. 2: Write aC pengram to bring ina byte of data serially one bit at a time via P10, The MSB: should

conve fist,

finclude

Sbit PlbO = P10;

Void main{}

4

Unsigned chat x;

forlx = 0; x < 8; x++}

{

reg ALSB = PIbO;

ACC = A xe 13

a

P2 = ACC

)

#include

void main()

& dione char x, binbyte, dl, 42, 43;

binbyte = OXFF;

x = binbyte/10;

dl = binbyteti0;

dz = xt10;

a=

Po = al;

PL = 42;

Fe = a3;

)

seattle fof Le via

“Tan [am [to | reo | tet | mi | to | mmo

L Bit no ‘Symbol Funetion |

7 Tri Timer 1 overflow flag. ‘Sot when timer alls from af 15 and Os cleared when

processor vectors to aNeCute interrupt service routing located at progeam

address OOH =

6 TAL | Timer rum control bit, Set to 1 by program to enable timer to count, Cleared

by programe halt -

5 TAO | Timerdoverlow flap. Set when tier rls from all 1s ands cleared when

process wactor te execute ISA loca ad at programe address OOOBH

4 TRO Timer 01" contro! bit. Set to | by program to enable timer to count. Cleared

bry progtea to at

0-32 Solved Question Papers

3 {Er Externat interrupt 1 edge a. Sato | by program when a high-low edge sigray

isroveived frompartd

a m External interrupt signal type control bit. Set to 1 by program to enable

axtoral interrupt tobe ceared by a faling-edye signal

1 10 | External interrupt 0 edge fag, Set to 1 when a high-to-tow edge signal is

received on part3

External interrupt0 signal type control bt. Sotto 1 by program to anable

external intorrupt Oto be tiggered by a falling edge signal. Set to O by program

fo enable a low-level signal.

‘Twone

<——— Timer —— Timer 9 ——

nore {a s{4fafa2}tita

Gate | oT | mi | mo | ae | ot | m | mo

Bit | Symbo! Function

18 | Gate | OR gate enables bit that controls RUN/STOP of timer 10. Seto | by program to

enable timer to run if bit TRYGin TCON and signal on external interrupt are set

82 C/T__| Set to 1 by program to make tier i/0actas a counter by counting pulses

a MI_| Timerfcaunter operating mode sefect itt Set/leared by program to select mode

40 MO__| Timer mode selection

Mt Mo Mode

0 0 0

o 1 1

- 1 0 2

_ 1 1 3

5. b, The following are the characteristies and operations of mode 2:

1. Itis an &-bit timer; therefore, it allows only values of 00 to FIH to be loaded into the timer repister TH.

2, After TH is loaded with the 8-bit value, the 8051 gives a copy of itto TL. ‘Then, the timer should be

started. This is done by the instruction “SETB TRO” for timer 0 and “SETB TRI” for timer 1

3. After the timer is started, it starts to count up incrementing the TL register. It counts up until it

reaches its limit of FFH. When it rolls over from FFH to 00, it sets high the limit of FEH4 and makes

the timer flag high TF.

4, When the TL registered rolls from FFH to O and Tis set to I, TL is reloaded automatically with the

original values kept by the TH. To repeat the process, we should simply clear TF sand let it go without

‘any need by the programmer to reload the original value,

TAL he UL i

csalator {a} m =)

cT~o

Ralona

™ i)

Solved Question Prpers Q-33

te

MOV TMOD, #0110 00008; Initialize counter 1 in mode 2, C/T = 1

Mov TLL, #0

START: SETB P3.5

BACK: SETB tri

MoV A, Tha

MOV P2, A

NB TFI, BACK

CLR TRI

CLR TF2

SUMP START

ba

Pin no. Pin description B

ec oved ling signal detectar

Regaived data

Trensmited date

Signatyourd ____|

[Date terminal eady _

Signs! ground _

| Data set ready |

equestto send |

[Rincat

ORS oonDst

SgMP 33H

ORG 30H

Mov TMOD, #2011

Mov THA, #-38

MOY scON, $501

SETB TRL

AGAIN: MOV A, #'V!

REALE TRANS

Nov A, #0T"

RCALL TRANS

NOW A, HU!

ACALL TRANS

NOW A,2'R!

MOV A,#'E*

ACALL TRANS

MOV Bi, 8°L"

CALL TRANS

NOY AAG!

ACALL TRAIS

MOV A, HA!

ACALL TRAKS

nov ago"

(34 Solved Guostion Papers

ACALL "TRA

MOV AQ

ACALL TRANS.

AGAIN: SOMP AGAIN

TRANS: Mov spur, a

HERE: NB TL, HERR

CLR TT

BT

END

& c Importance ef 7)

1

1. ‘The byte character tbe transmitted is writen into SBUF register

2. The start bit is transferred

3. The &-bit character is transferred one bit ata time

4.

‘The stop bitis tansfred. It is during the transfer of the stop bit thatthe 8051 raises the TI flag, thus,

icicating that the lst character was transmitted and itis ready to for the next character.

hs the T fag, we make sure that we arc not averlapping of overloading

Afier SBUB js loaded witha new byte, the

‘TI flag bit should be foreed to 0 by the “CLRVTI” instruction

fm order for this new yt to be transferred,

a

Importance of RI lag

A. Tt receives the star bit, thus indi catin

i¢ that the next bit is the fiest bit of character byte it is about to.

receive,

The B-bit chorncter is received

Placed in SBUF,

The stop bit is received. When receiv

character byte has been receiv

character,

By checking the RI flag bit when it is taised, we know th

sitting in the SBUE register

Afler the SBUF contents are copied inte a safe place, the RE flag bil should be forced to 0 by the

“CLR RI” instruction in order to allow the next received character to be placed in SBUF: failure to

da this causes logs uf the reeaived character.

‘ne bit ata time. When the las bitis received, a byte is formed und

ing the stop hit the 8051 RE=

ed and should be picked wp before it goss

indicating that an entire

overwritten by an incoming

hat the character has been reveived and is

ie

1 6 5 4 3

(eee Dos on

21 8

[ea Tee Tae |

oa | a 7]

HEA) Enable imternapts:

a | incsed 3

SleTa. Reserved far fatare

\ aes} | Ena

SiN!) [Enable ima overfiow tiag

| EAD)

Enable external interrunt

\ ETO)

$s

i Enable tino 0 overflow intorupt

ee Enable extemal interrupt

Salved Questian Papas O35

Pr

7 8 6 UH

— [em [ps [em | pan | pro | xo

Bit mumber Fonction

786 Notused

5 Reserved for future use

4 Priority of serial port iuerept

3 Priority far timer 1 overfosrinterrunt

=

1

0

\

Priority for external nterupt

Priority for timer Ooverflay interrupt

Priority for extennal ntl

() #includacregSL.ns

bit wave = POTD

void timerd()

1

Wave = -aver

| 1

| wid serial 0)

| {

} tf (TF == 1)

' {

| eee

| elee

| {

pp = SPUF:

1 = 03

)

|

void mein()

(

Uheigned char «

2 > OXFF;

MOD ~ 9X22;

THI = OXFD,

scan = OKO;

uu = ORG:

1g = 0x92

el = 1s

TRO

while Wt

1.3 Sohed Question Papers

q

p2 = SRUF;

SHUF = x;

Pl = x

}

}

Ra The LCD module is organize in two lines, cach

Ground

of 20 characters. The module has 14 pins

Deseription

_

+#5¥ power supply

Used for cantraling LED contrast

‘When fi,= 0, data register is selected

When 8; = 1, command register is selected

4 Riv f= Wiv = 1 for reading

IM = Ofor writing

5 E 1 ‘This pin is used by LCD 10 latch information available atts data

pins:

me | DB-0B, WO | These pins are used to send information ta the LCD or read the

| contents ofthe internal registers of the LCD.

ALP to display message “HELLO” on LCD display:

MOV SIR, #30H ; 4initilize state pointer

MOV A, #3CH

LCALL COMMAND

Mov A, #0EH

LCALL COMMAND ; set the coninand code to set display and

cursor ON

MOV A, #01H

LCALL COMMAND

MOV A, #E6H

LCALL COMMAND

MOV A, 8TH } Display the

LCALL DISPLAY

MOV A, A’EY

CALL DISPLAY

MOV A, #rL! ; Display ‘L’

LCALL DISPLAY

MOV A, abt

LCALL DISPLAY

Mov A, qo" + Display *’

LCALL DISPLAY

HERE : SSMP HERE,

Display Routine:

Display ‘2!

; Display ‘b’

letter 7H’.

UCALL READY Check whether LCD is ready

MOV PI, A issue data

ab

SETA P3.2

CLR P33

SETS 3.4

CLR Psa 3

RET

ORG OOH

MOV A, HOST

mov RO, #2007

BACK = RRA.

wov Pl, X

ACALL DELAY

NZ RO, BACK

MERE. : SUMP HERE

DELAY : Mov R2, #105

LOOP? : HOV RL, #075H

LOOP] = DINE RL, LeCr

pug B2, LOOP?

RET

END

Soho Question Papers: 37

RS = 1 to isme data

= 0 to enable writing

Make

Make

Make

make

USN

LL)

Microcontrollers ~ Jan. / Feb. 2009

‘Semester - IV (EC/ TC/ EE/ 1T/ BM/ML)

Time: 3 Howes

Note:

Qa

b

Q3 a

os

Maxinmam Marks: 100

wor any FIVE fiell questions, selecting at least TWO questions fram each part.

PART-A

Differentiate between a microprocessor and a microcontroller. (Marks 6)

Lis! he salient features of 8051 microcontroller. (Marks 6)

Explain the memory organization in 8051 controller (Marks 8)

Explain the following instructions with suitable exarbples. ’) SWAP ii) MOVX ili) XCHD iv) DA A.

(Marks 6)

Write an assembly language program using 8051 mnemonics to convert 2 digit BED to binary,

(Marks 0)

‘What isa stack? Explain with examples the PUSH and POP instructions. (Marks §)

Differentiate between a counter and timer, Explain the timer modes of operation in 8051. (Marks 6)

Name and explain the signifieance of interrupt of 8051 controllers. (Marks 6)

\Wite 051 C prograrm to toggle all bits of port PO continuously. Use timer to generate the delay of

Vs

nveen vach logele. (Marks §)

[Differentiate between SMP and CALL instruction. Explain with suitable examples the different ranges

assvciated with call instructions, (Marks 0)

Explain with suitable examples LCALL and SCALL instruction in 8051. (Marks

Write on assembly language program fo realize an exclusive OR gate. Assume PIO and PI, 1 as inpers

and P2.0 as ootput bit, (Marks 1)

PART-B

5 a, Write an 8061 C program to wansfer the message "Ciood morning” serially at 9600 baud, 8-bit daw,

1 slip bit (Marks ®

Solved Question Papers O38

bb Explain serial port of 8051, Explain the significance of SCON register indicia (Marks 6)

‘c,. What isthe usc of MODEM inserial coma nication? Describedifferent types of modulation techniques

(Marks 8)

sused in MODEM.

(qa, What i ey bouncing? How i i eliminated?

a port of 8051 and explain its operation

«_ Withaviablehardvare and sofware etre, explain an inefis of 7 segment display in multiplexed

(Marks 10)

connection.

bb. Show a sitnple Keyboord interfice with (Marks 6)

ing such an

als of importance while interfaci

(Marks 19)

Q7 a. Explain the salient features of an ADC What are the sign’

ADC 10 18051 controler?

to R051 controler Witte stare equzed to obta

bh. Show a scherse of interfacing. an 8-bit ADM

the ontp rom sah an iteraoe, Discuss patie pplication. (Marks 10)

8 4. Show an inverfoee of 051 controler with a lEPPET snotor dive ercit and explain ts principles of

(Marks 10)

operation,

Wiitean 8051 ascanbly language poogram to (ep) control topper moor using eonsections given in Figure

_ "

ad =f

|.

ao

Pa

taotoe

vein

i

WW

2

|

Assume eode sequence is stored in a mein i

a memory Location pointed ode, Use 4

routine, Coounent cn each of instruction used. eee bg TR code Use allo das

SOLUTIONS

Microcontrollers - Jan./ Feb. 2009

Semester - IV (EC/'TC/ EE/ IT/ BM/ML)

PARTA

| Microprocessor ‘Microcontroller

2. Ieontsins ALU, stack painter, general-

Purpose registers, program counter clock

fining cccut, end interrupt circuit

a, contains circuits assembled ina

microprocessor and has a built-in RAM, ROM,

VO devices, timers, and counters.

. Ithas many instructions to move data b. Ithas few instsuctions to move data between

between memory and CPU ‘memory and CPU

¢. Ithas one oF tivo bit handling instructions

Ithas nny bit-handing instructions.

d. Access time is more for memory and [yO r

‘Accesstime is less for builtin memory and

devices WO devices

«©. Iteontsins only one mamory mapping for bath | e, IReontains a separate memory or both data

| ata and eodo and code

1. b. Features of 8051 Microcontroller

(4096 bytes program memory on chip

(i) 128 bytes data memory on chip

(ii) Four register banks

(iv) 128 user-defined software flags

(v) 64 KB each program and extemal RAM accessiblity

(vi) Moliple-mode, high-speed programmable serial port

(vii) Two 16-bit timers‘counters

(vill) Two-level prioritized interrupt structure

1c, Intertal memory

‘The intemal RAM organization of 8051 has 128 types.

‘This memory is organized into 3 distinet arcas

{a} Working registers (b) Bitaddressable (©) General-purpose registers

‘Working Registers:

The address range of working registers is OOH to IFH that is, the first 32 bytes. It is organized into 4

register hanks of 8 registers cach, RIO, RBI, and RBZ.

Bit Addressable

‘The #051 has 16 bytes of bit-addressable area. It accupies 20H to 2FH,

General Purpose Registers

“The RAM area above the bit-addressable aren from 30H to IPH is called general-purpase registers.

Gohed Qurstion Papers O41

The 8051 has4K bytes af internal program memory and 256 bylesafanternal memory. Ht ean access

upto 64K B programs 2s wel as dala memory. Lach maemiory has deren mechanisms, control signals,

and warwins funetions,

veins pee

ny

| Sacred ——

4 :

||

Ln con com |

LT oL

2. a. (SWAP A:

‘The abowe instmction imterchangis thi LSB of sccummulator wit the MSD of accunivalater

Before execution Ar2SH) 0010 101

Aficrexecutinn — ALS2H: 9101 DIO

Ai) MOV «dese, source

‘The MOV instructions transfer data between the accumulator and a byle of external data memory,

Fx MOVK A, Ro

MOVE Ro, {

cay) NCH

Format: CIID A, aR

XCHT exchanges the lower nibble of the aceurmalaiar (bils 74), generally represetiting, a

‘jexadecimel or RED digit, with thet of intemal RAM lovatiow indinecly addressee by the specified

register No flags ane affected.

Ex. Ra 2011, A=34H GiRo~ 75H

CIDA, Ro

After exeentian:

liv) DA AY

TDA A edjusts the eight-bit value in the aeenmulator resulting Jum earlier uddition of tow variables

modi tvra fourbic dis, Any ADD or ADC insinustion may have been used to perform the

addition,

Ac Sail

Ro= aah

+

BOW

(DA A)_+ 66H

cay [238

oe

2 b.

Sotved ve

on Papert

mow B, HOO

Mow A, #18

yoroy ; Save ACC in

A= A (AND) OFH

pust

ack

SWAP A

Mow B, #10 A = reverse

B= 10

; A= AB

; yetrieve ACC

ANL A, #0FH A= A (AND) OF

ADD A, B ) A= A 4B (Result is in A}

Stack 24

A stack refers to an area of internal RAM that is used in conjunction with certain opcodes to store and

‘eineve data quickly. The stack pointer (SP) is an 8-bit register used by the 8051 to hold stack address

that is called top ofstack. The SP is st to 07H when the 8051 is eset. In PUSH and POP operations, it

is implied that the SP holds the indirect address,

PU

‘The PUSH instruction increments the stack pointer by one and copies data from the source address to the

internal RAM location addressed by the SP. Before the operation, since the SP is incremented, the data

are stored from a low address to a high address in the intemal RAM. As the data are pushed, the stack

‘grows in the intemal RAM. The top of the internal RAM is at 7FH., So, if we go on PUSHing the data

onto the stack after 7FH, the data are Jost. Figure 2 shows the PUSH operation.

|

Stack pointer (SP)

| {SPis inoromonted belore

PUSHing the data)

etna RAM

Fig.2 PUSH operation

ror

“The POP instruction copies the contents of the internal RAM location addressed by the SP to the

destination address (specified in the POP instruction). Then, the SP is decremented by one, This ensures

that the data placed on the stack are retrieved in lhe simme order as they were stored.

You might also like

- VTU Exam Question Paper With Solution of 18EE52 Microcontrollers Feb-2021-Ranjitha R100% (5)VTU Exam Question Paper With Solution of 18EE52 Microcontrollers Feb-2021-Ranjitha R30 pages

- WINSEM2024-25 BECE204L TH VL2024250504065 2025-01-23 Reference-Material-INo ratings yetWINSEM2024-25 BECE204L TH VL2024250504065 2025-01-23 Reference-Material-I5 pages

- Unit - IV 1. What Is Mean by Microcontroller?: Internal Blocks of MicrocontrollerNo ratings yetUnit - IV 1. What Is Mean by Microcontroller?: Internal Blocks of Microcontroller6 pages

- ON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. ProfessorNo ratings yetON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. Professor66 pages

- Iv Semester B.Tech (Electrical & Electronics Engineering) Grade Improvement Examinations, August 2021No ratings yetIv Semester B.Tech (Electrical & Electronics Engineering) Grade Improvement Examinations, August 20215 pages

- The 8085 Microprocessor Architecture, Programming and Interfacing PDFNo ratings yetThe 8085 Microprocessor Architecture, Programming and Interfacing PDF626 pages

- ECE3003 M A 2018: Icrocontroller and Its Applications SsignmentNo ratings yetECE3003 M A 2018: Icrocontroller and Its Applications Ssignment43 pages

- Microprocessor and Interfacing Exam 2012No ratings yetMicroprocessor and Interfacing Exam 20122 pages

- The 8085 Microprocessor Architecture Programming and Interfacing K Udaya Kumar100% (1)The 8085 Microprocessor Architecture Programming and Interfacing K Udaya Kumar626 pages

- Answer Any Five Questions Choosing at Least Two From Each PartNo ratings yetAnswer Any Five Questions Choosing at Least Two From Each Part4 pages

- 13 - CPE220 - 1019 - Theory Final Exam Answer KeyNo ratings yet13 - CPE220 - 1019 - Theory Final Exam Answer Key7 pages

- ET7102-Microcontroller Based System Design QB PDF100% (1)ET7102-Microcontroller Based System Design QB PDF10 pages