0% found this document useful (0 votes)

46 views9 pagesCode Generation in Compilation

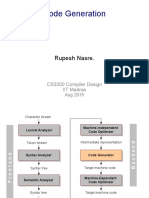

The document discusses the code generation phase of compilation, detailing the transformation of intermediate code into machine or assembly code. It outlines the characteristics and requirements of the target program, tasks of the code generator, and issues related to correctness and efficiency. Additionally, it covers instruction selection, register allocation, evaluation order, and the cost associated with instructions in various addressing modes.

Uploaded by

codehacker026Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

46 views9 pagesCode Generation in Compilation

The document discusses the code generation phase of compilation, detailing the transformation of intermediate code into machine or assembly code. It outlines the characteristics and requirements of the target program, tasks of the code generator, and issues related to correctness and efficiency. Additionally, it covers instruction selection, register allocation, evaluation order, and the cost associated with instructions in various addressing modes.

Uploaded by

codehacker026Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

/ 9