0% found this document useful (0 votes)

19 views5 pagesExam Microprocessor

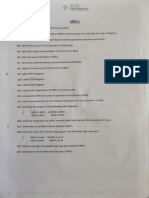

The document is an examination paper for the Microprocessor course at the Dar es Salaam Institute of Technology for the academic year 2013/2014. It includes instructions for the exam, two sections with various questions related to microprocessor systems, interfacing, memory, and programming. Students are required to answer all questions in Section A and any three from Section B, with specific guidelines on the use of materials during the exam.

Uploaded by

docxdocx72Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

19 views5 pagesExam Microprocessor

The document is an examination paper for the Microprocessor course at the Dar es Salaam Institute of Technology for the academic year 2013/2014. It includes instructions for the exam, two sections with various questions related to microprocessor systems, interfacing, memory, and programming. Students are required to answer all questions in Section A and any three from Section B, with specific guidelines on the use of materials during the exam.

Uploaded by

docxdocx72Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 5