Department of Electronics and Communication Engineering

B.M.S. College of Engineering, Bengaluru – 19

(Autonomous College under VTU)

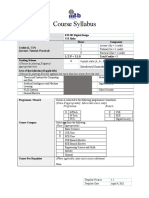

Course Title HDL PROGRAMMING LAB

Course Code 23EC3AEHPL Credits 1 L–T–P 0:0:1

CIE 25 Marks (100% weightage) SEE 50 Marks (50% weightage)

Course Outcomes:

At the end of the course, students will have the ability to:

Sl. No. Course Outcomes PO PSO

CO1 Apply the knowledge of HDL programming for modeling and functional 1, 5 3

verification of Digital circuits using EDA tools.

CO2 Analyse digital circuits using suitable Verilog HDL modeling using 2, 5 3

EDA tools.

CO3 Design and synthesize a digital circuit for complex systems using EDA 3, 5 3

tools.

CO4 Involve in independent / team learning, communicate effectively and 9, 10, 12 3

engage in life long learning

List of Experiments

1. Introduction to Vivado FPGA Tool Suite

2. Gate-level modelling: Half adder, Full adder

3. Gate-level modelling: Multiplexers and demultiplexers

4. Gate-level/Dataflow modelling: Decoders

5. Dataflow modelling for 2-bit magnitude comparator

6. Data flow modelling: Ripple Carry adder

7. Dataflow modelling: Carry Look-ahead Adder

8. Structural Modelling: Multibit Subtractor (using Adder)

9. Behavioural modelling for multibit magnitude comparator

10. Behavioural modelling for Encoder with and without priority

11. Behavioural modelling: SR latch, JK and D flip-flops

12. Behavioural modelling: Universal Shift Register

20

� Department of Electronics and Communication Engineering

13. Behavioural modelling: Synchronous Counters

14. Structural Modelling: Asynchronous counters

15. Behavioural modelling: Sequence detection

Text Books:

1. “Verilog HDL: A Guide to Digital Design and Synthesis”, Sameer Palnitkar, 2nd Edition, 2003,

Pearson.

Reference Books:

1. “Fundamentals of Digital Logic with Verilog Design”, Stephan Brown and Zvonk Vranesic, 2nd

Edition, 2008, McGraw-Hill.

21