0% found this document useful (0 votes)

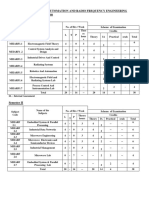

16 views29 pagesMicro Processor Architecture & Assembly Language (CS-323) : BS CS, SE, Telecom, Electronics & CET

The document outlines the course details for Micro Processor Architecture and Assembly Language (CS-323) at Sarhad University, focusing on basic logic instructions and their applications in low-level software. It covers various logic operations such as AND, OR, Exclusive-OR, NOT, and shift/rotate instructions, along with string comparison techniques. The course is designed for students in the 4th semester of BS programs in Computer Science, Software Engineering, Telecom, Electronics, and CET.

Uploaded by

masabk141Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

16 views29 pagesMicro Processor Architecture & Assembly Language (CS-323) : BS CS, SE, Telecom, Electronics & CET

The document outlines the course details for Micro Processor Architecture and Assembly Language (CS-323) at Sarhad University, focusing on basic logic instructions and their applications in low-level software. It covers various logic operations such as AND, OR, Exclusive-OR, NOT, and shift/rotate instructions, along with string comparison techniques. The course is designed for students in the 4th semester of BS programs in Computer Science, Software Engineering, Telecom, Electronics, and CET.

Uploaded by

masabk141Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 29