0% found this document useful (0 votes)

38 views38 pagesSynthesis Constraints

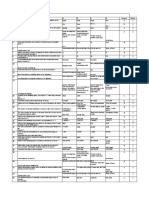

The document outlines synthesis constraints and logic cell selection, emphasizing the importance of timing analysis for circuit design. It details the significance of defining constraints such as maximum area, power, and timing paths to ensure designs meet operational requirements. Additionally, it discusses the modeling of clock parameters, including latency, uncertainty, and transition time, to optimize circuit performance.

Uploaded by

behenkalaudahaituCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

38 views38 pagesSynthesis Constraints

The document outlines synthesis constraints and logic cell selection, emphasizing the importance of timing analysis for circuit design. It details the significance of defining constraints such as maximum area, power, and timing paths to ensure designs meet operational requirements. Additionally, it discusses the modeling of clock parameters, including latency, uncertainty, and transition time, to optimize circuit performance.

Uploaded by

behenkalaudahaituCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 38