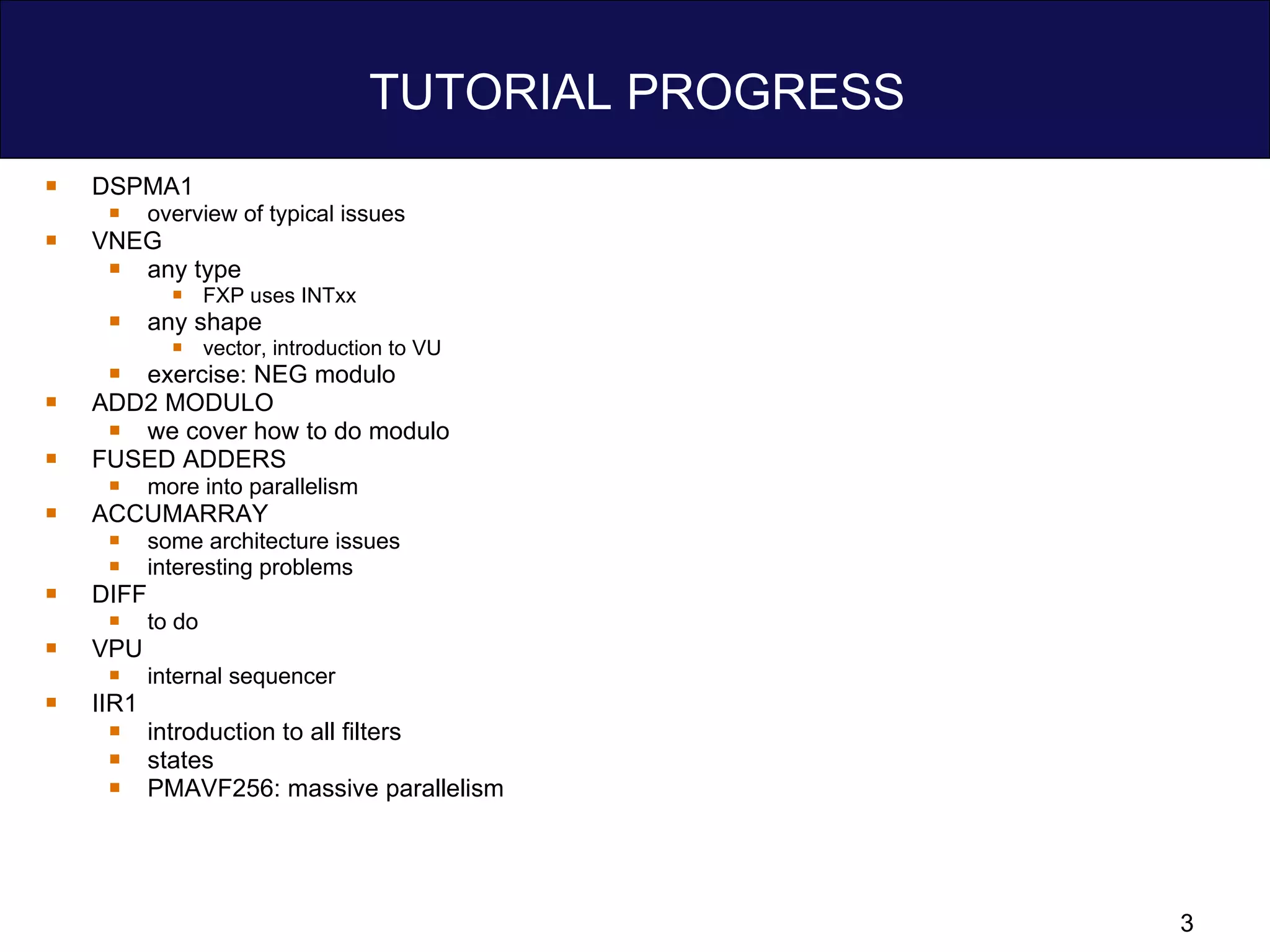

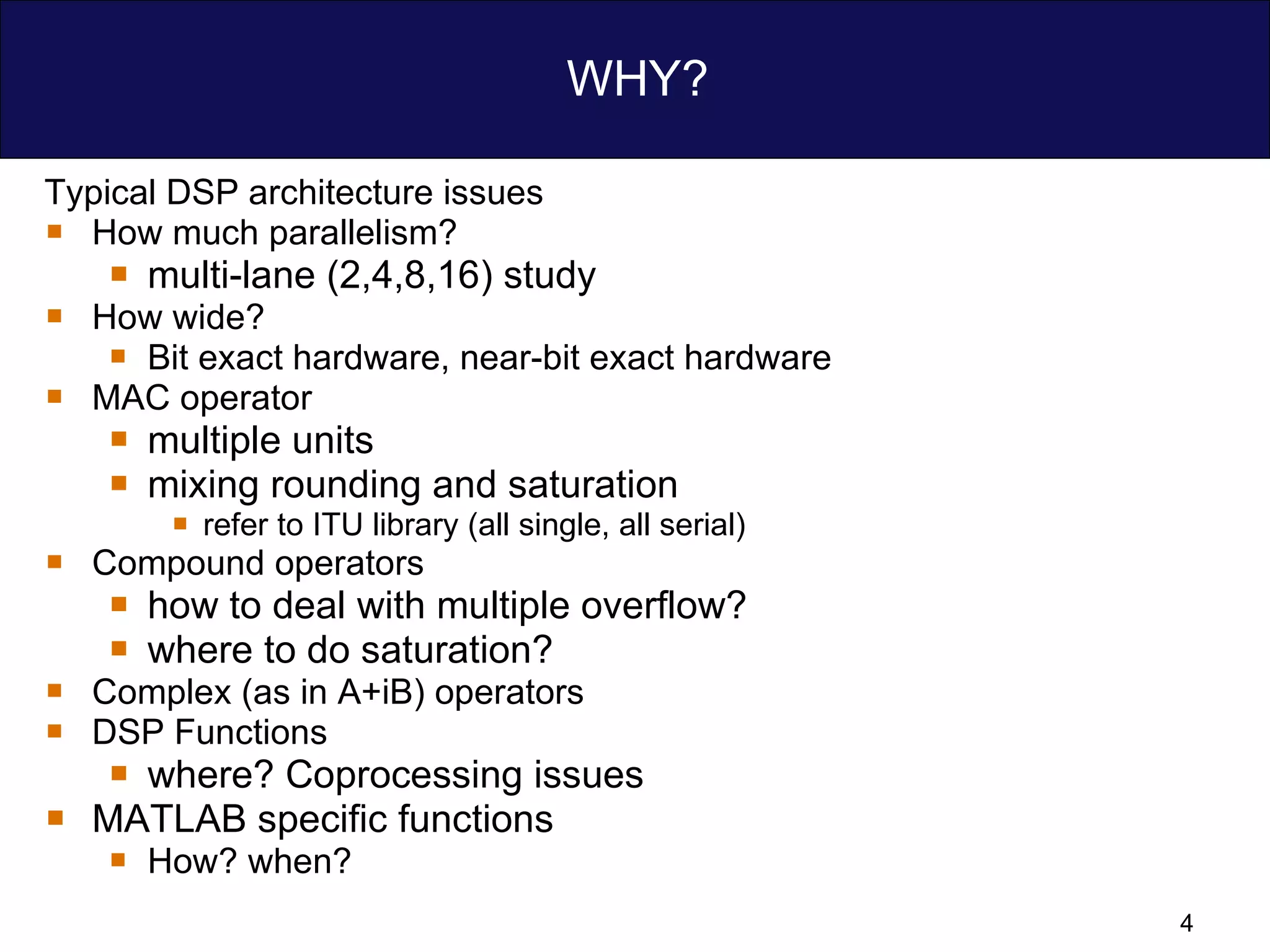

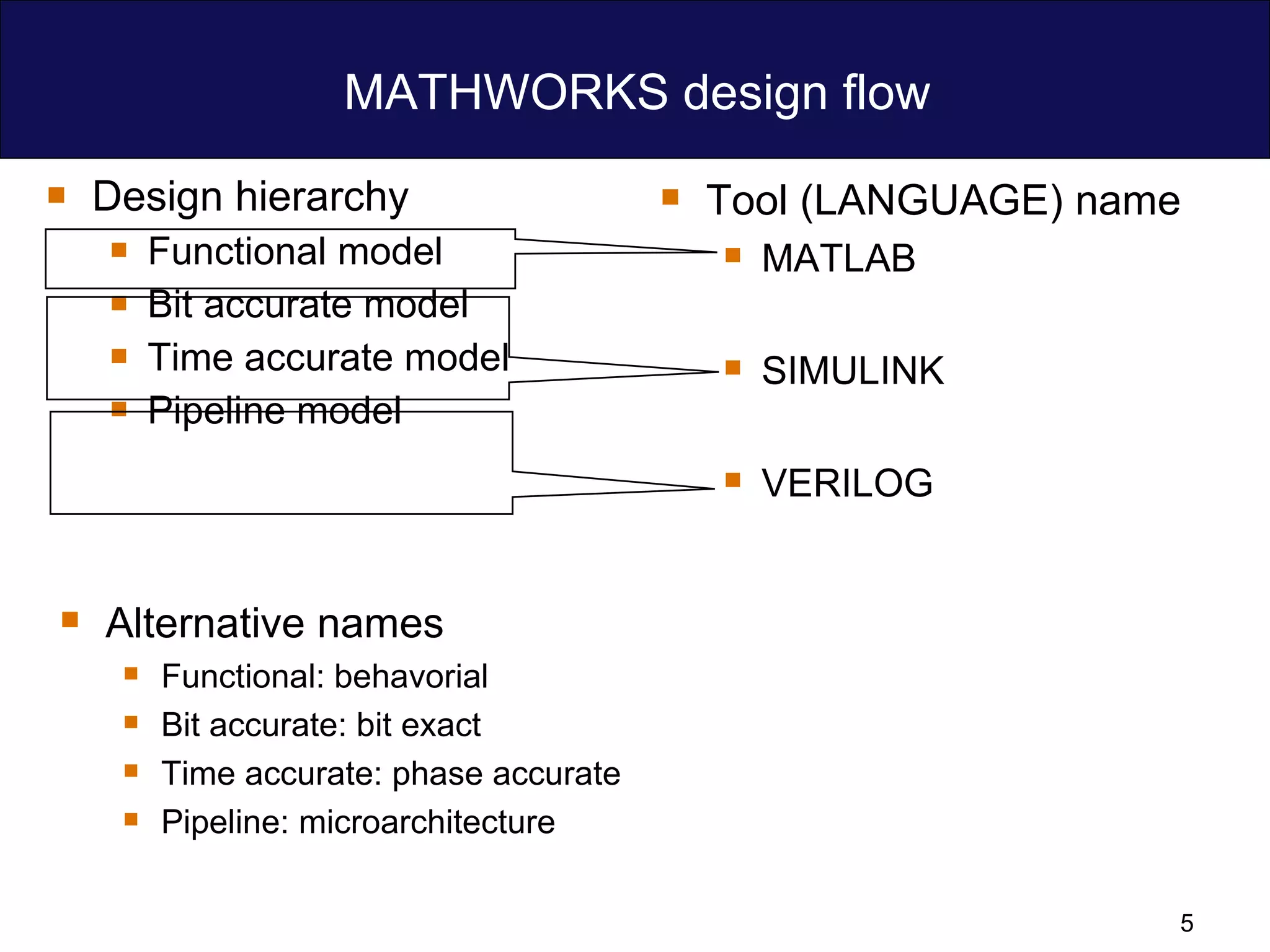

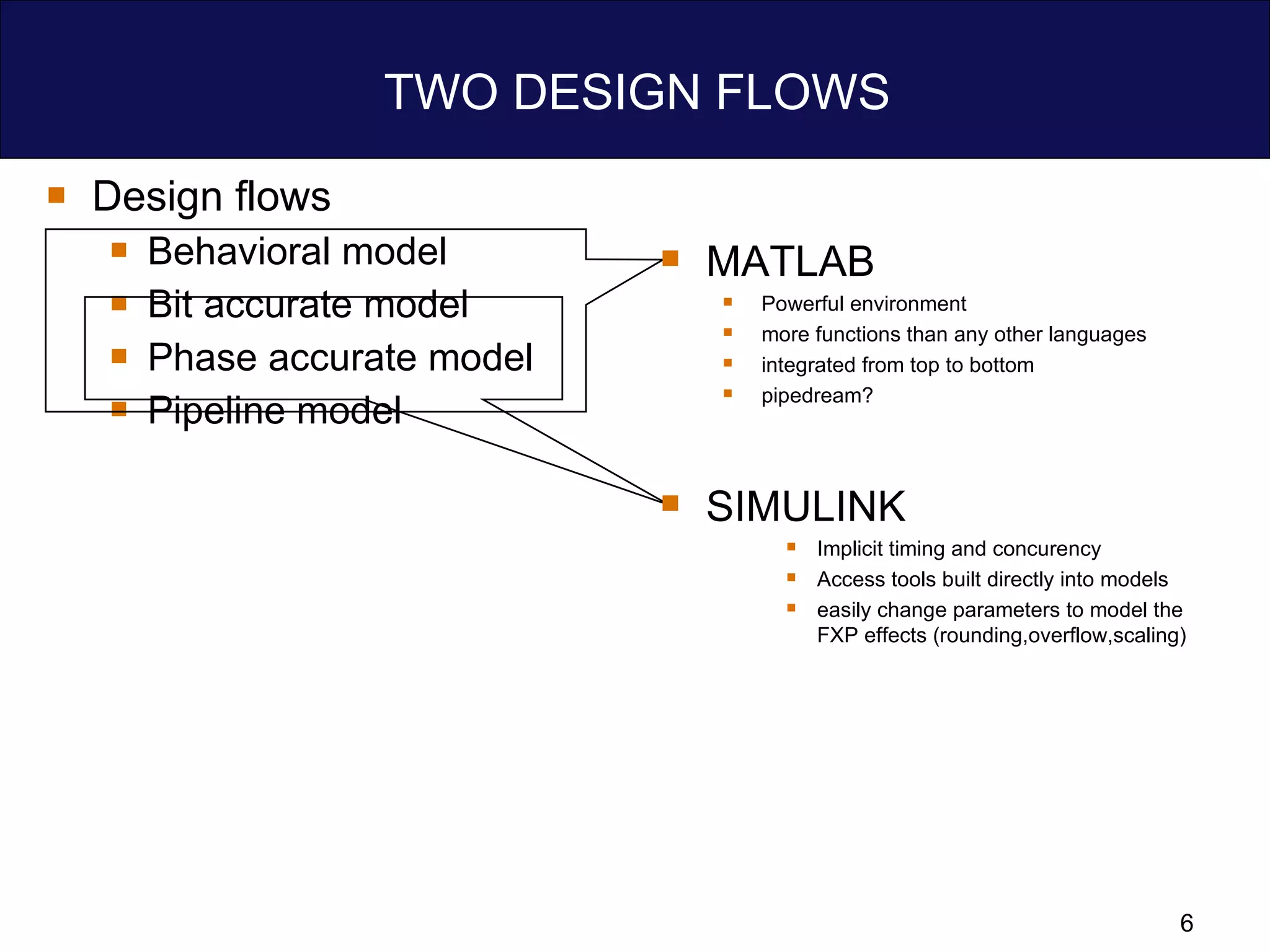

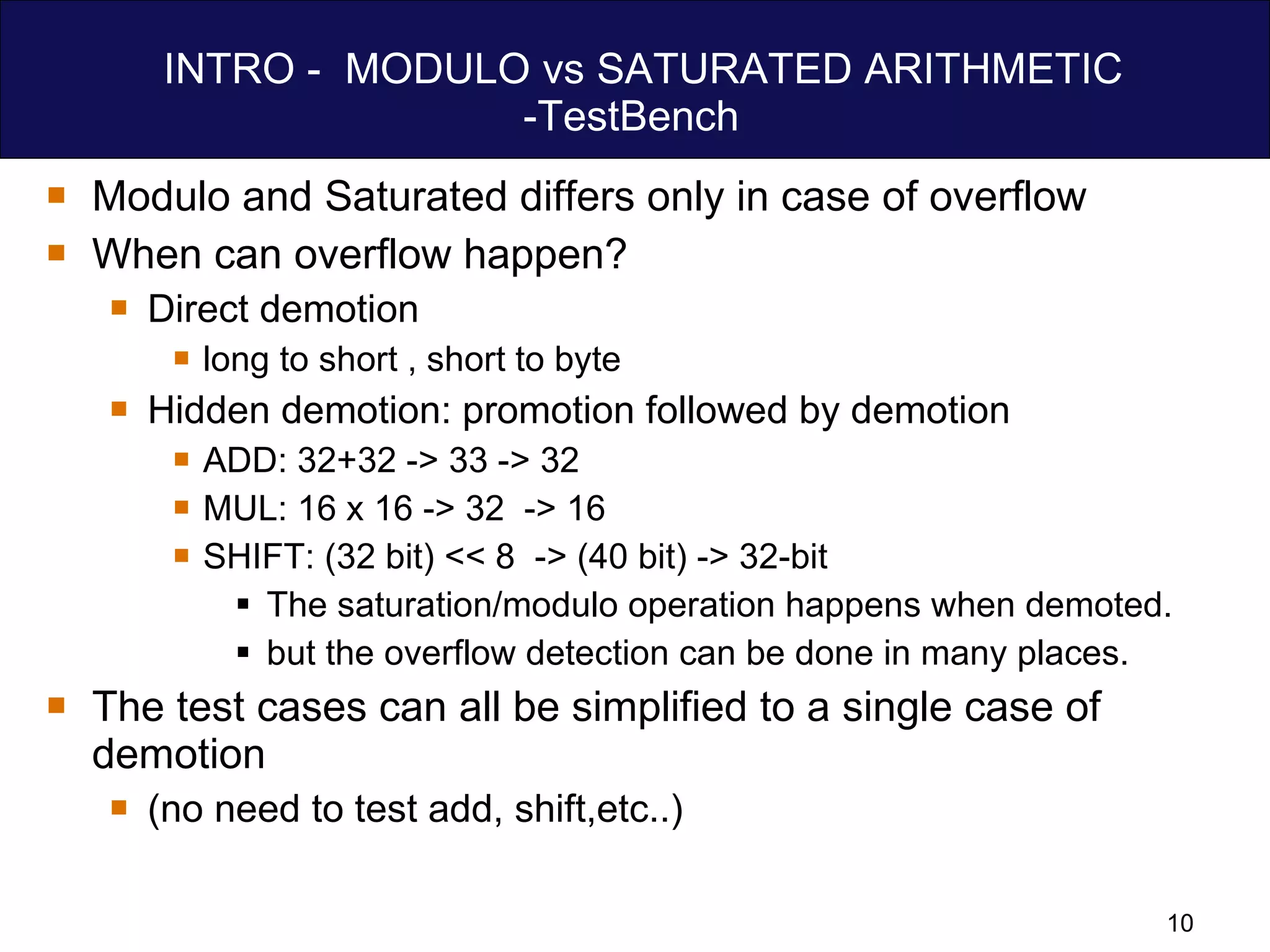

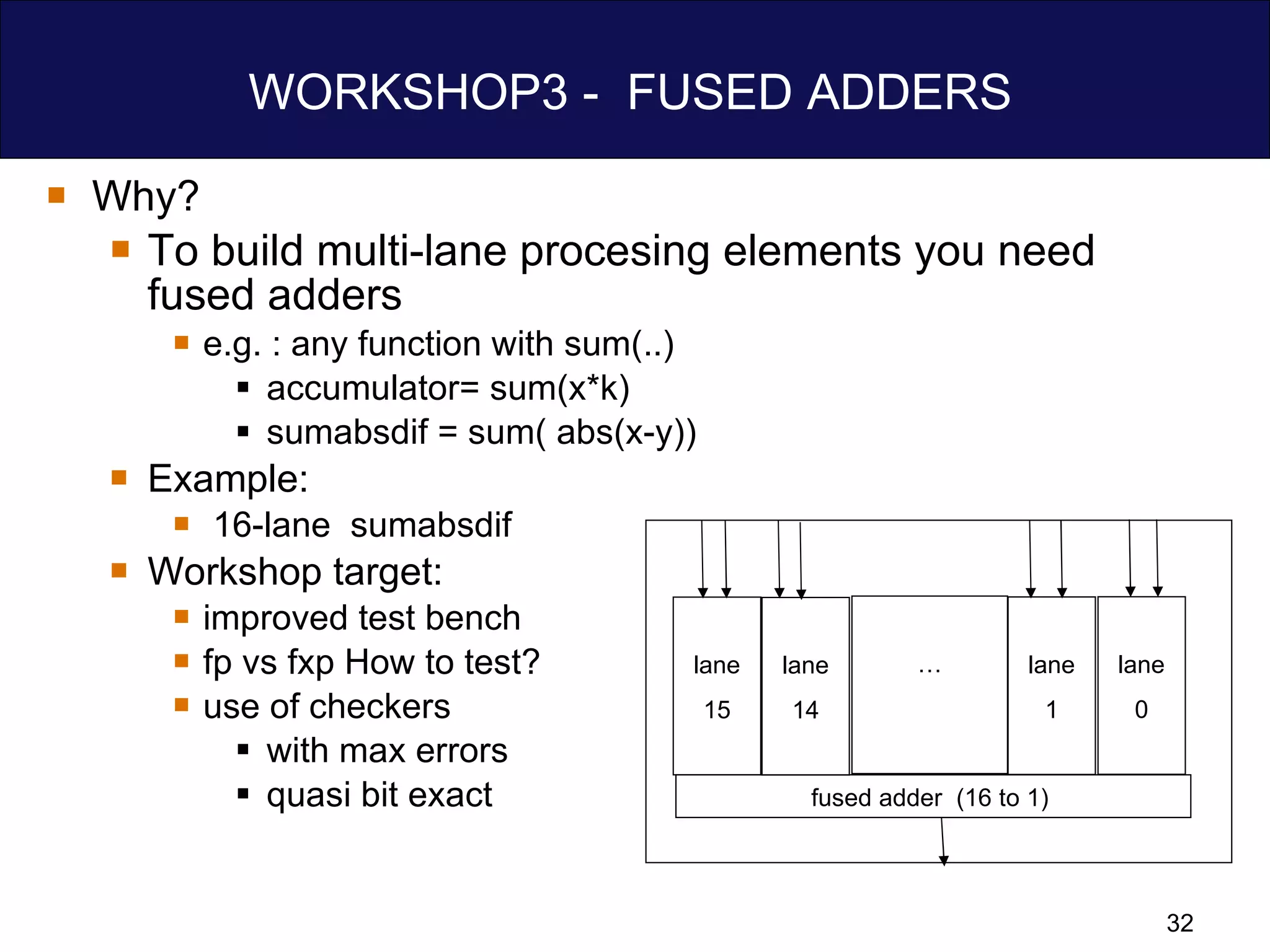

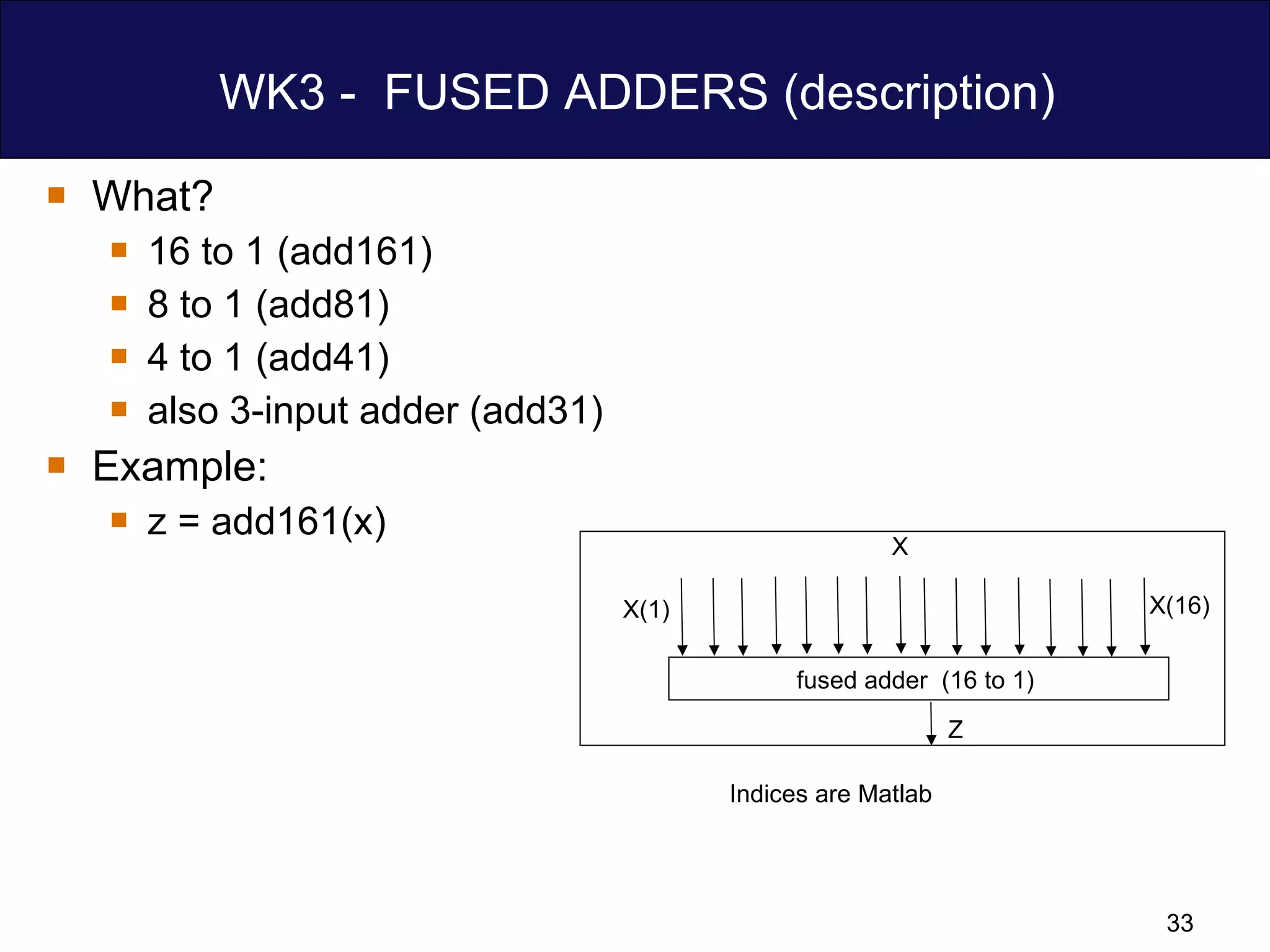

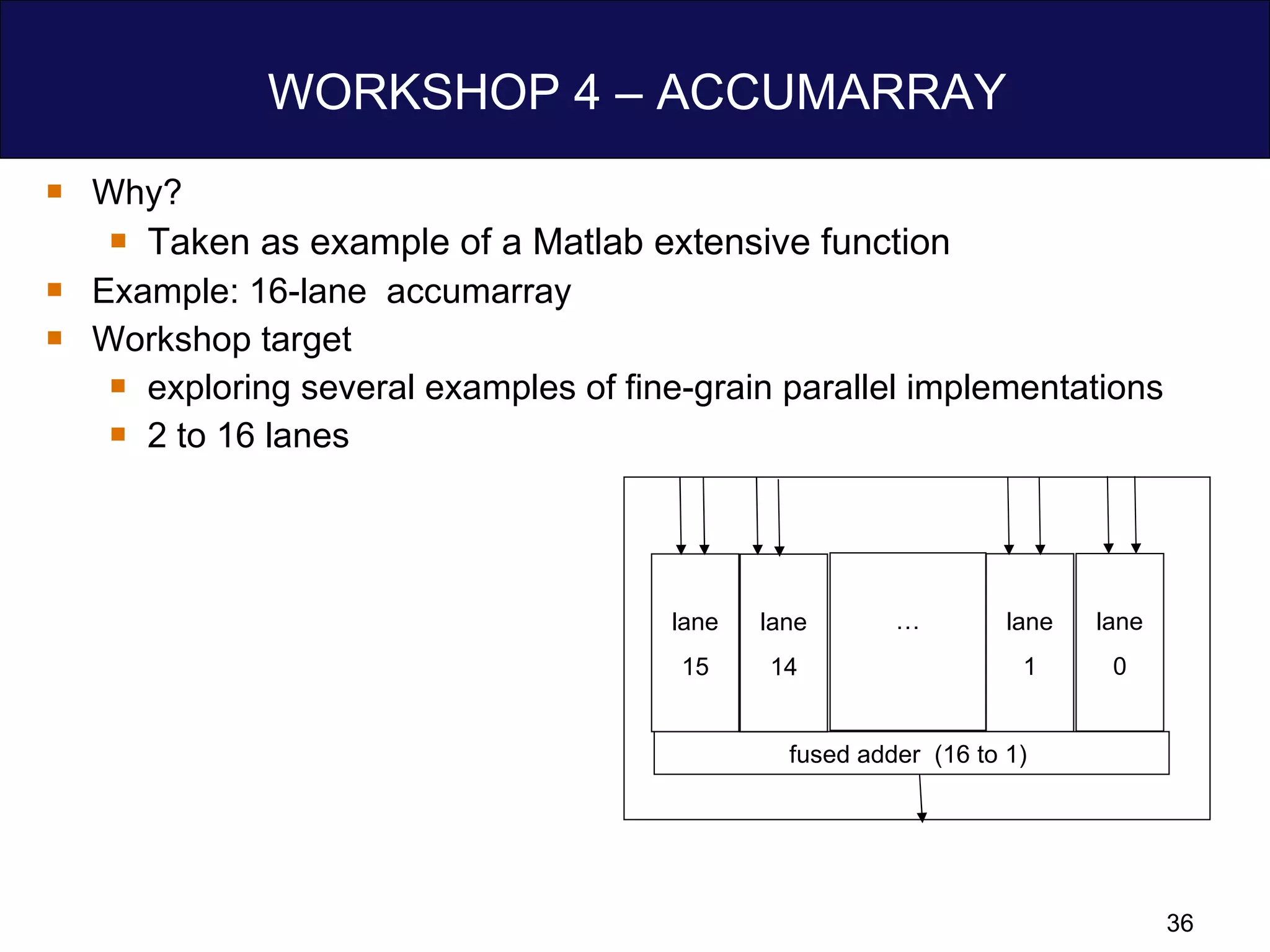

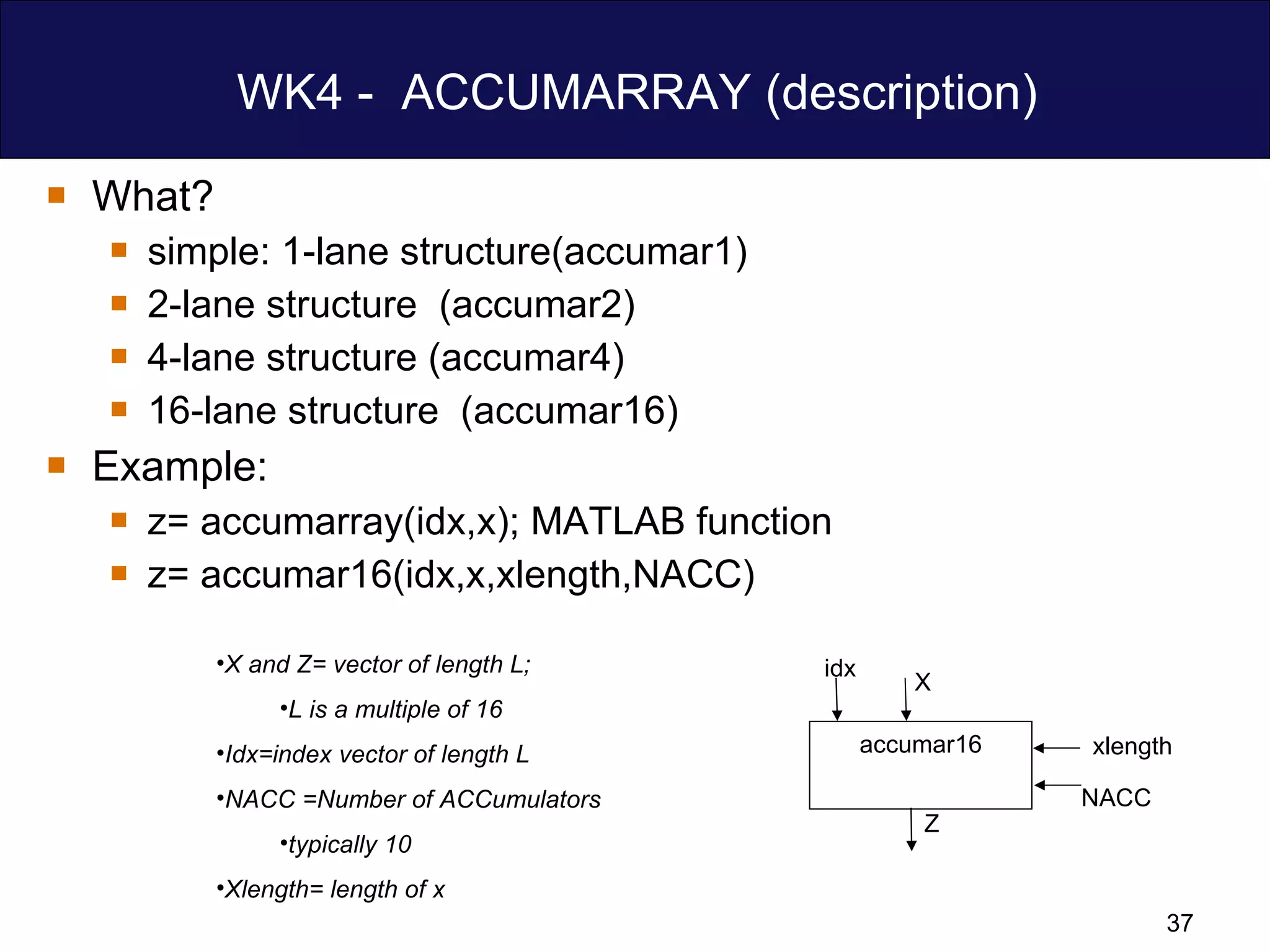

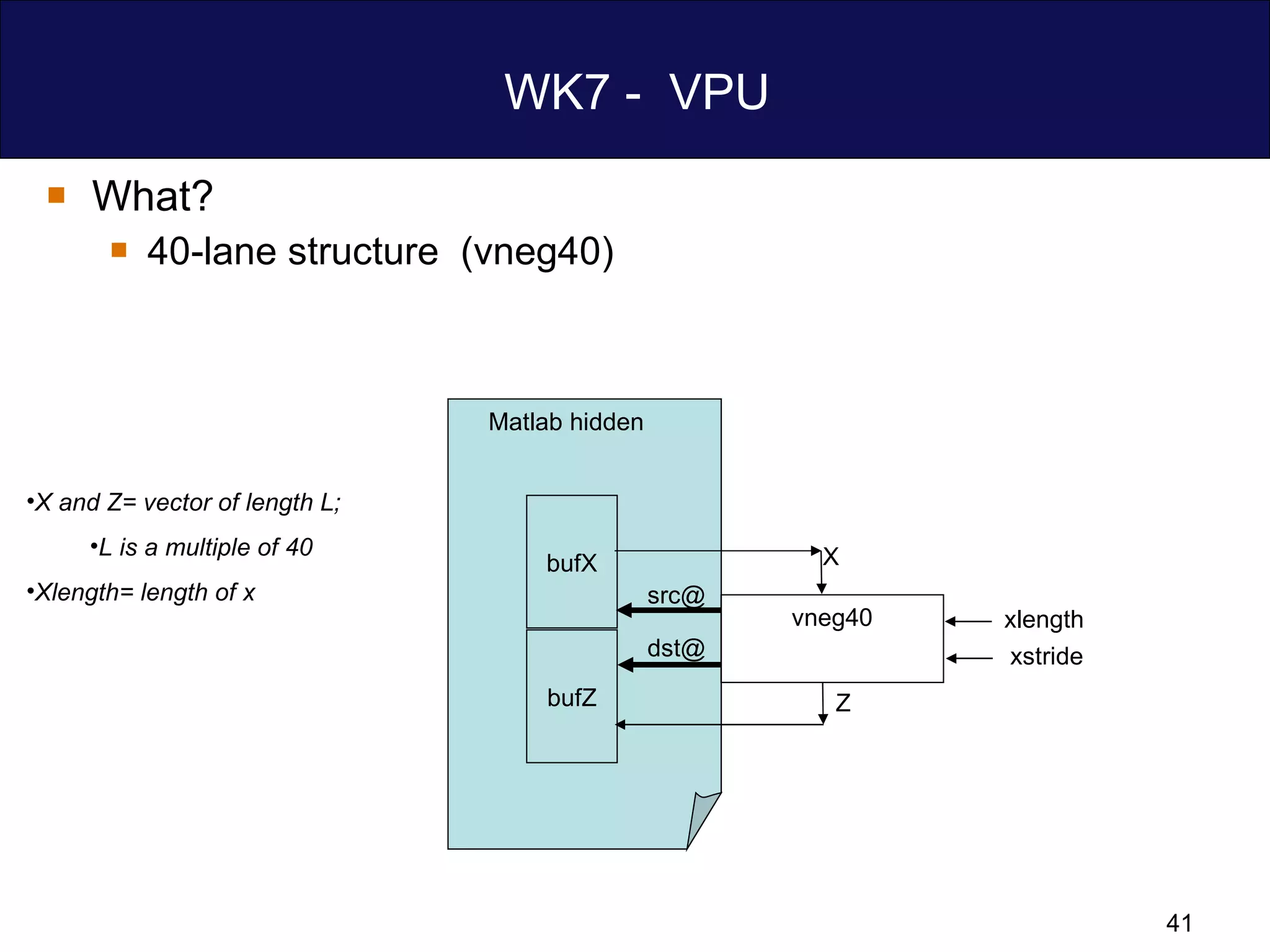

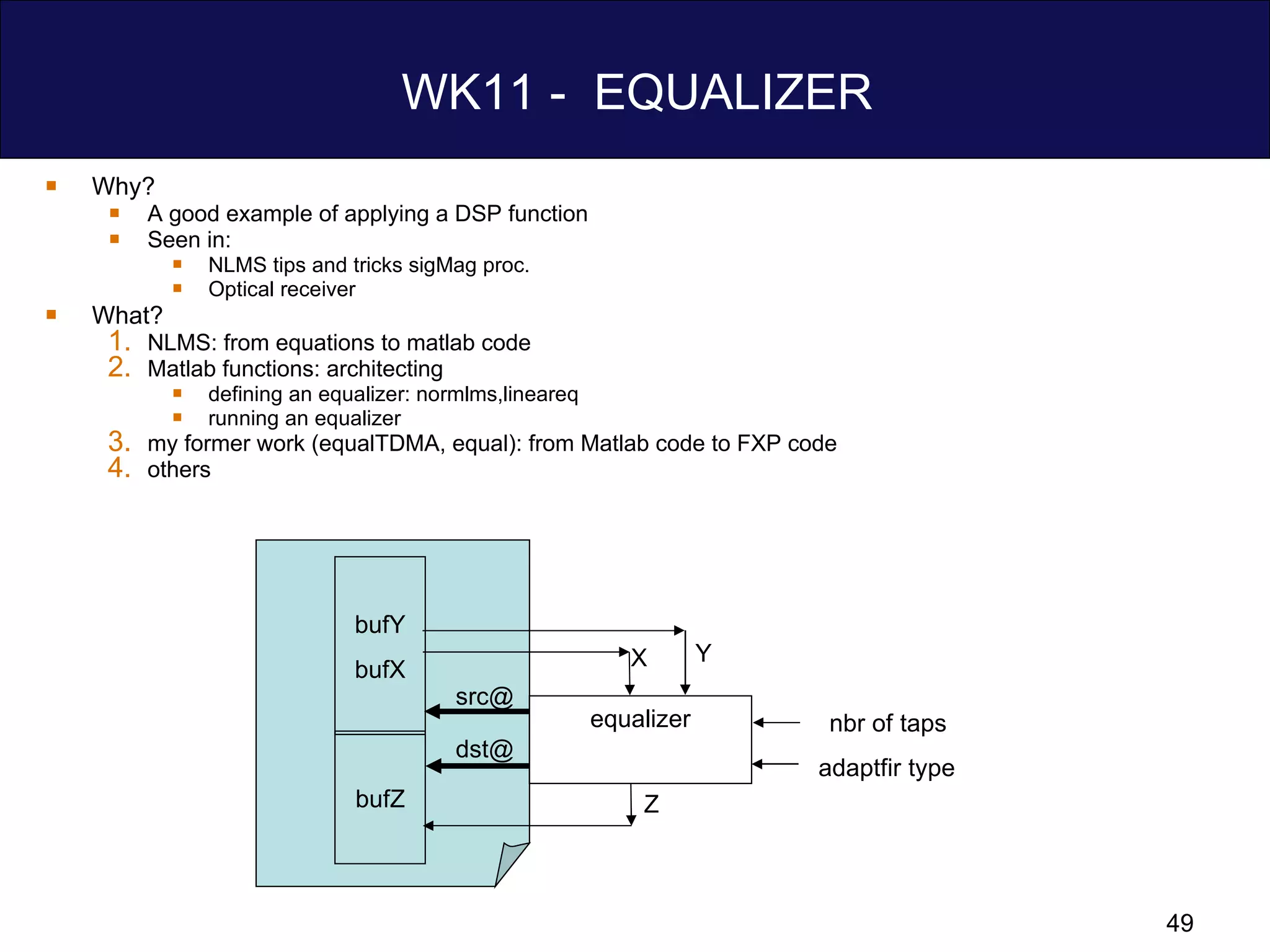

This document discusses modeling digital signal processing (DSP) CPU architectures using MATLAB. It provides an overview of typical DSP design flows and modeling approaches, including behavioral, bit-accurate, time-accurate and pipeline models. It also discusses fixed-point number representation issues in MATLAB and outlines several tutorials that demonstrate modeling DSP units like adders, accumulators and filters using MATLAB.