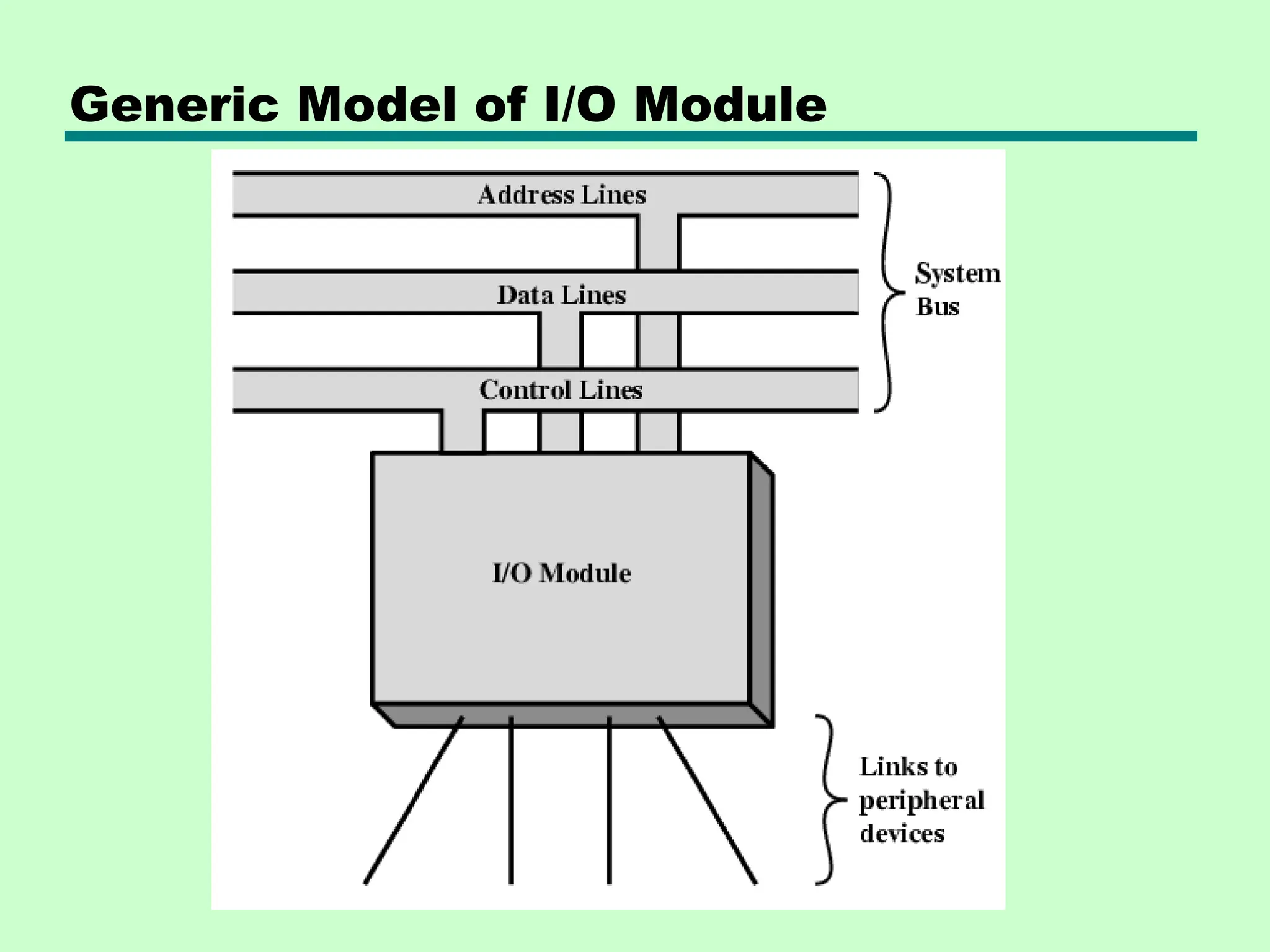

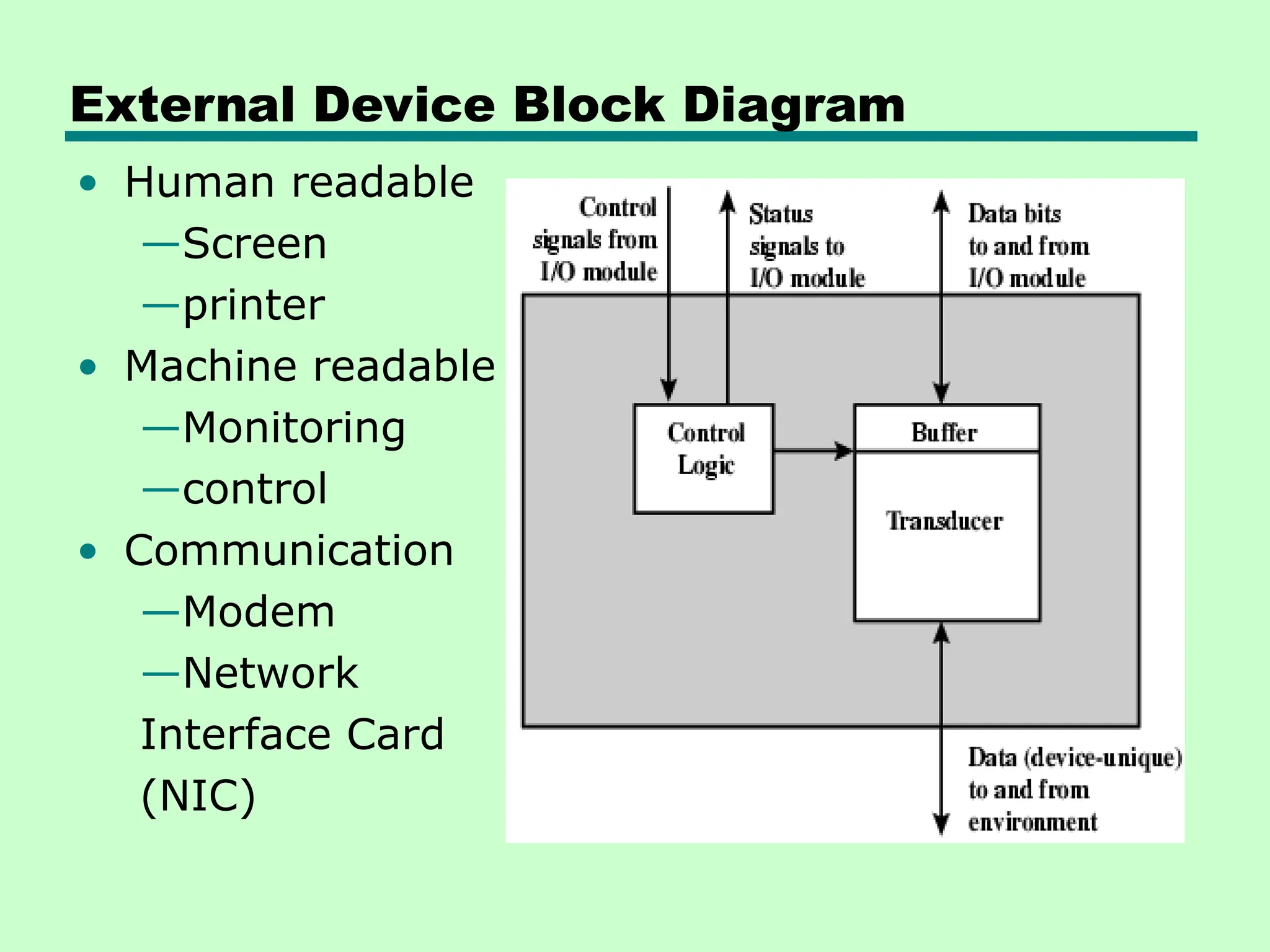

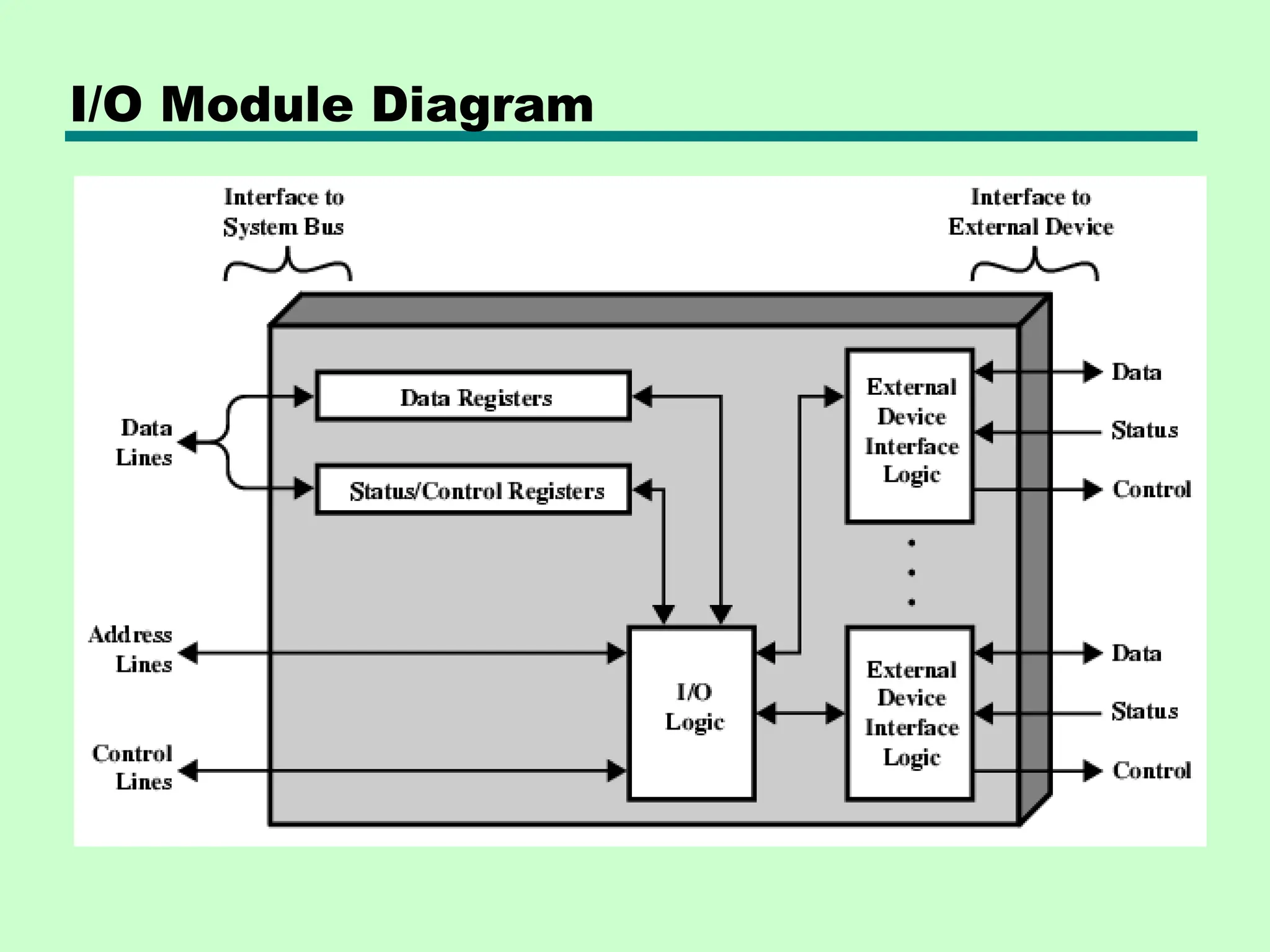

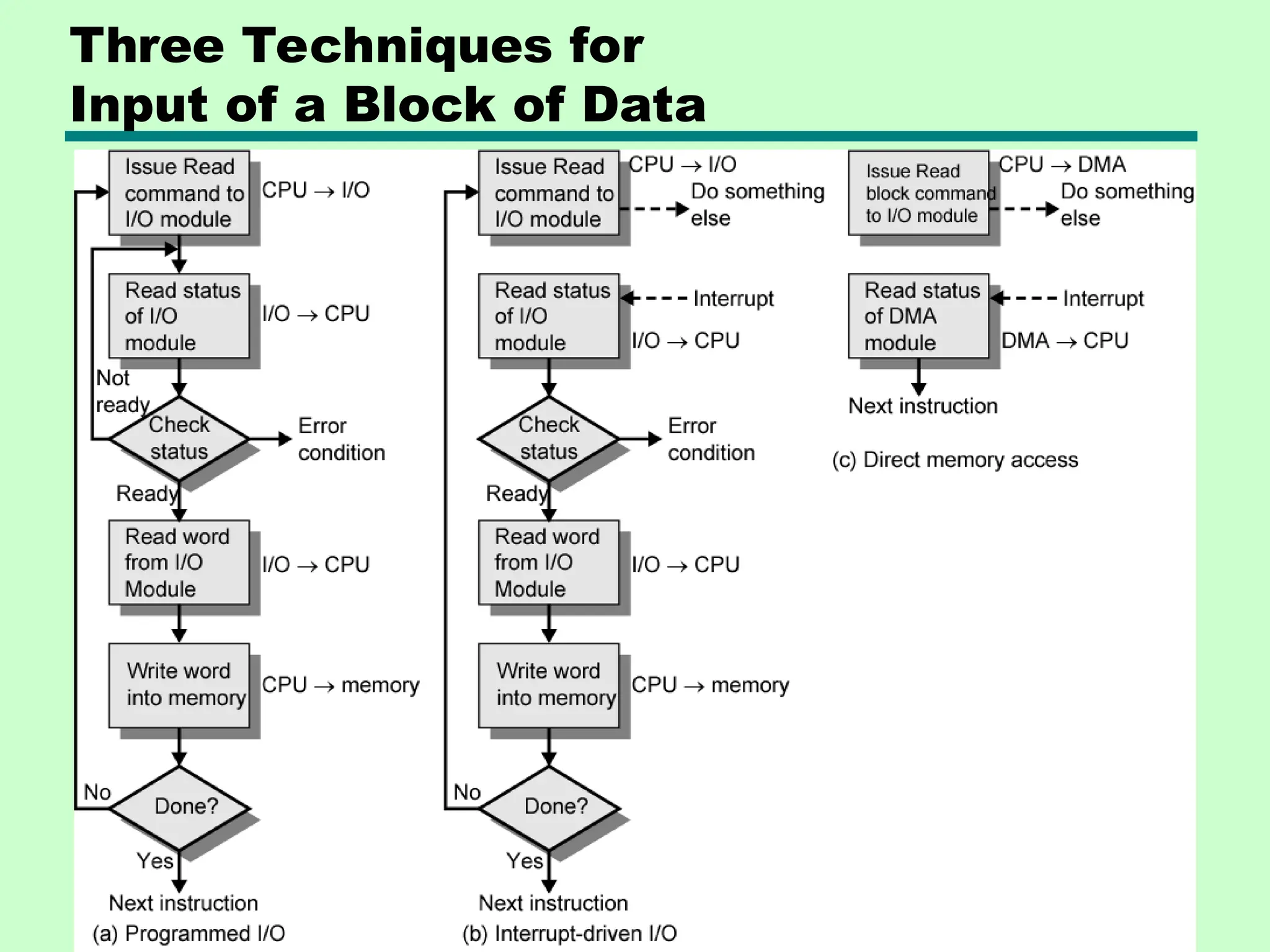

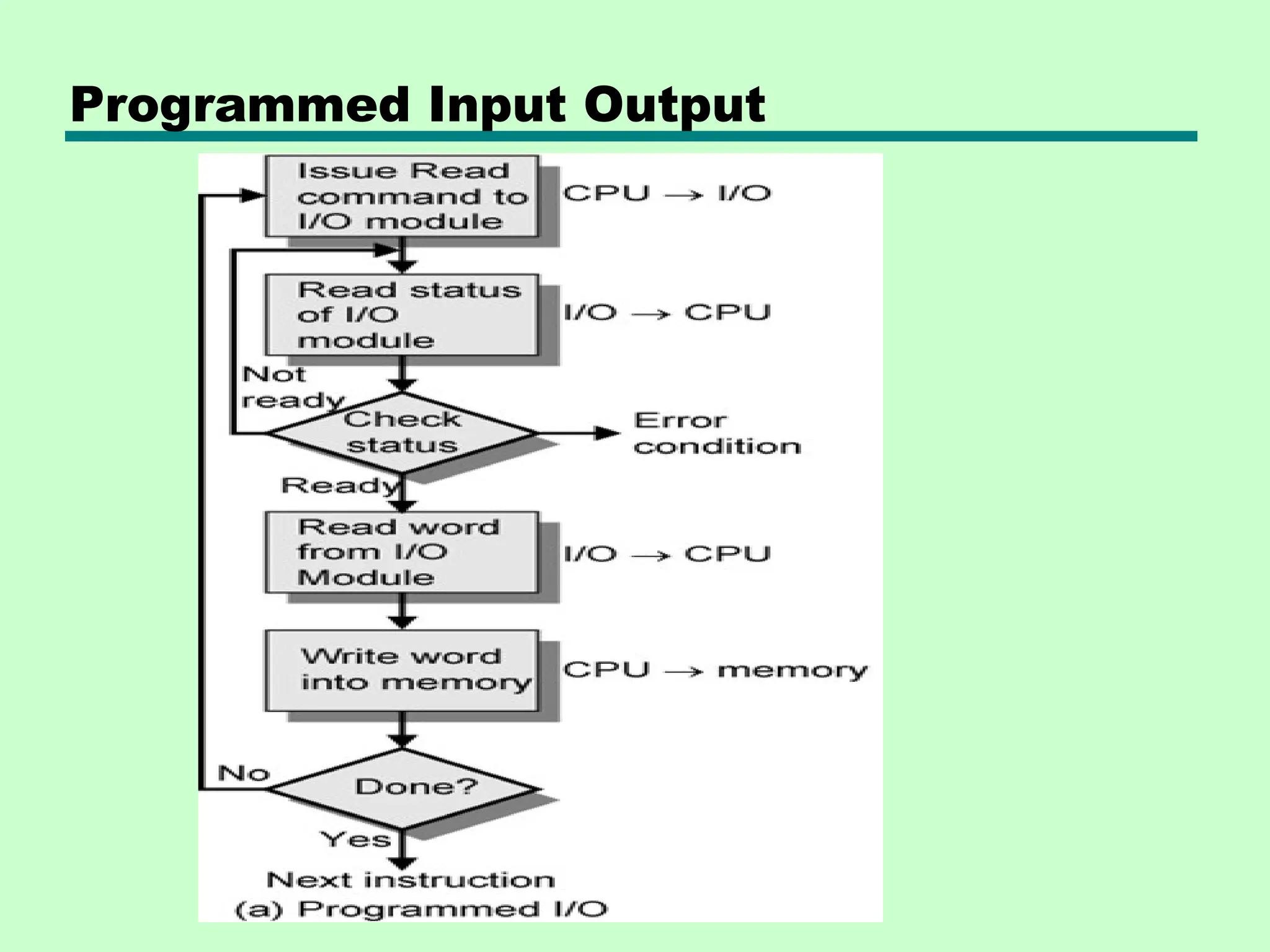

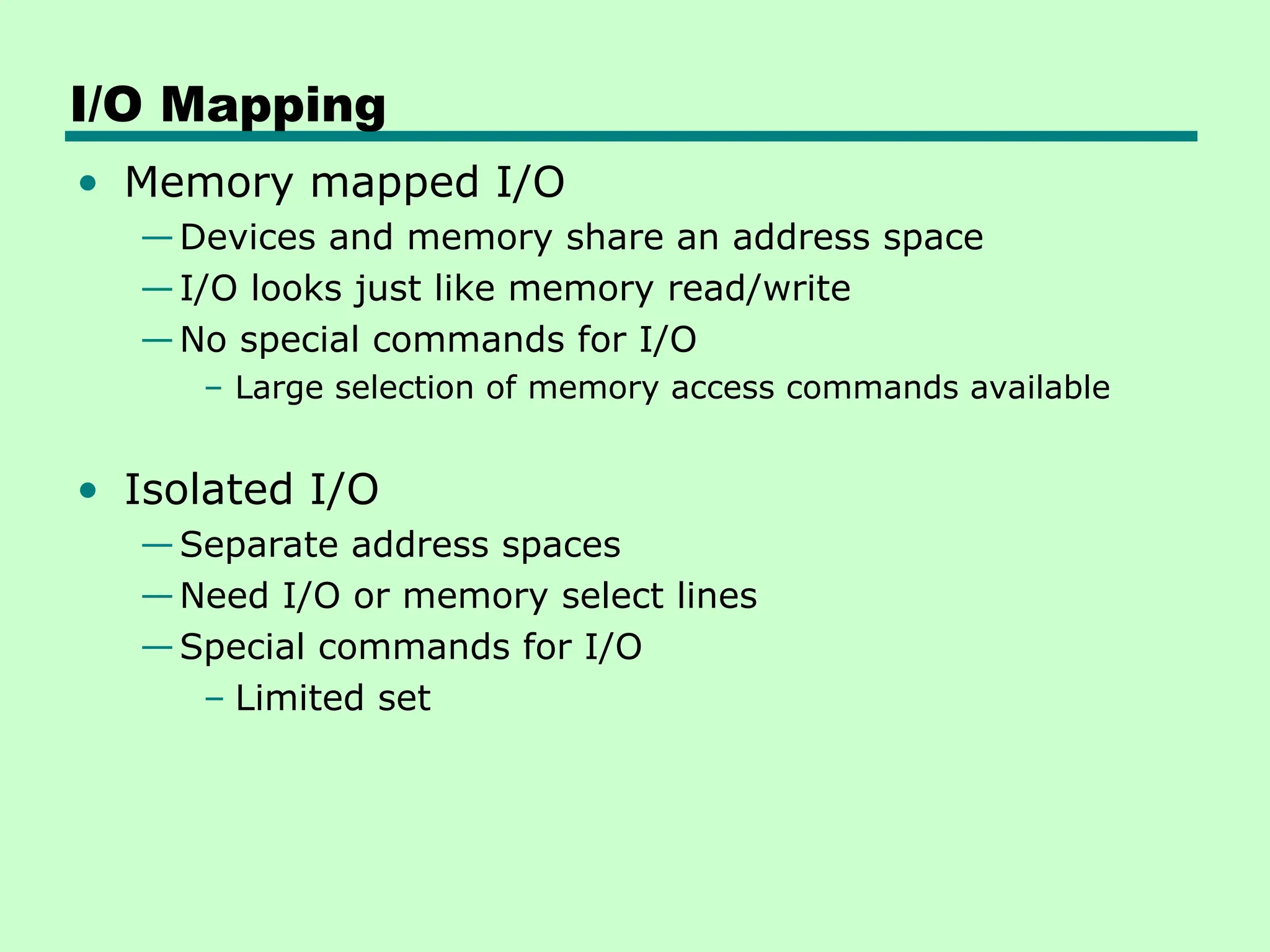

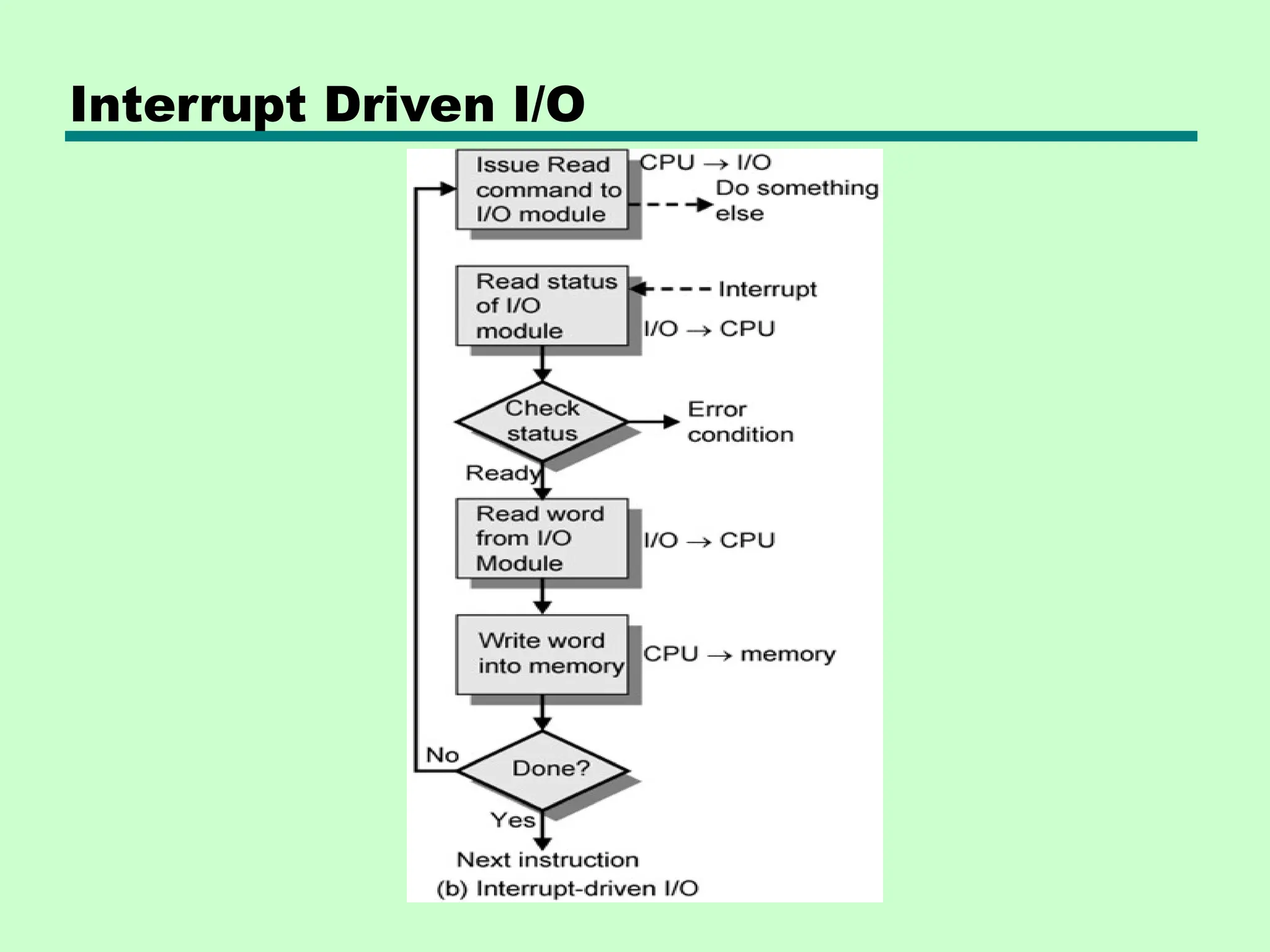

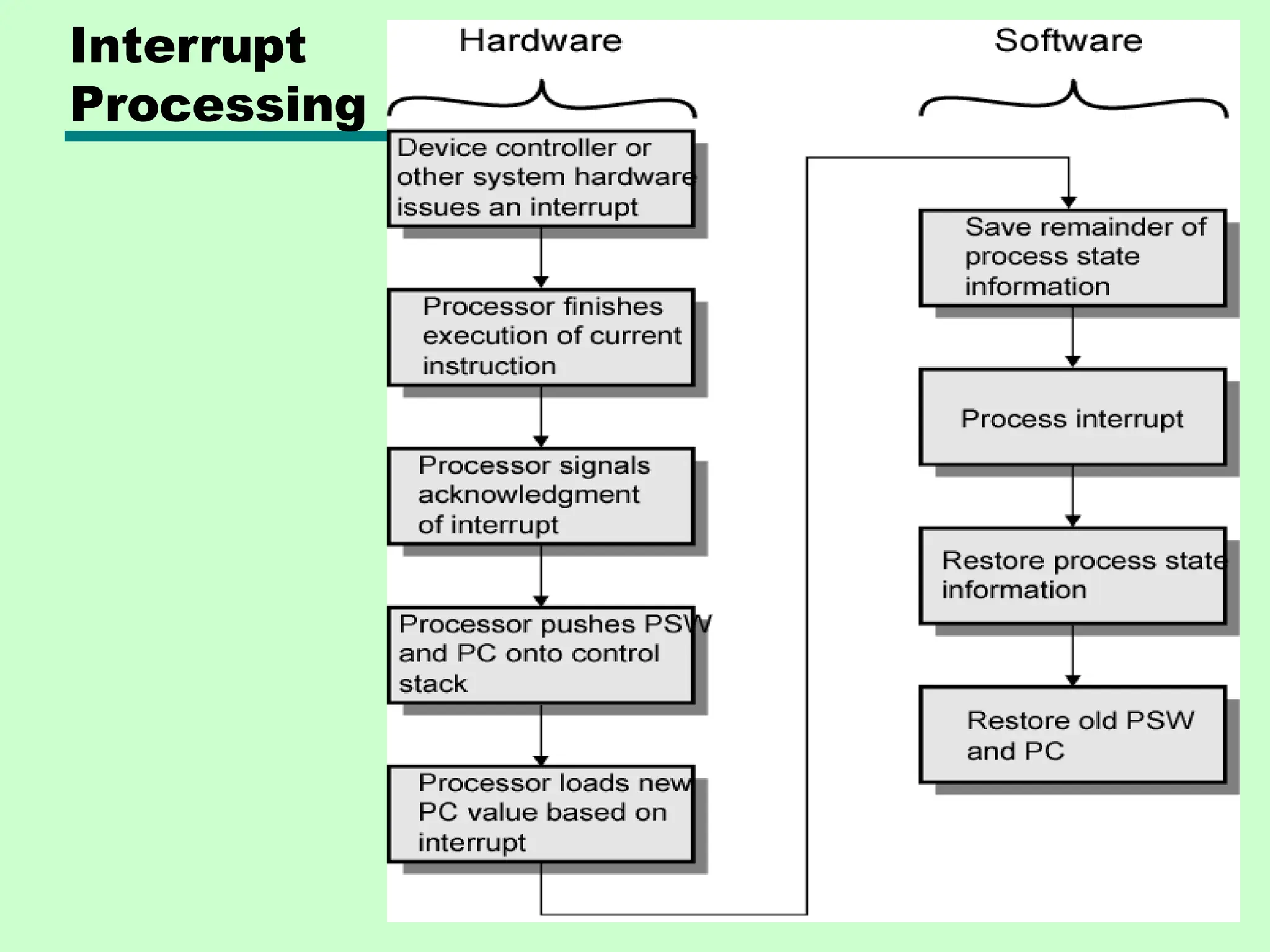

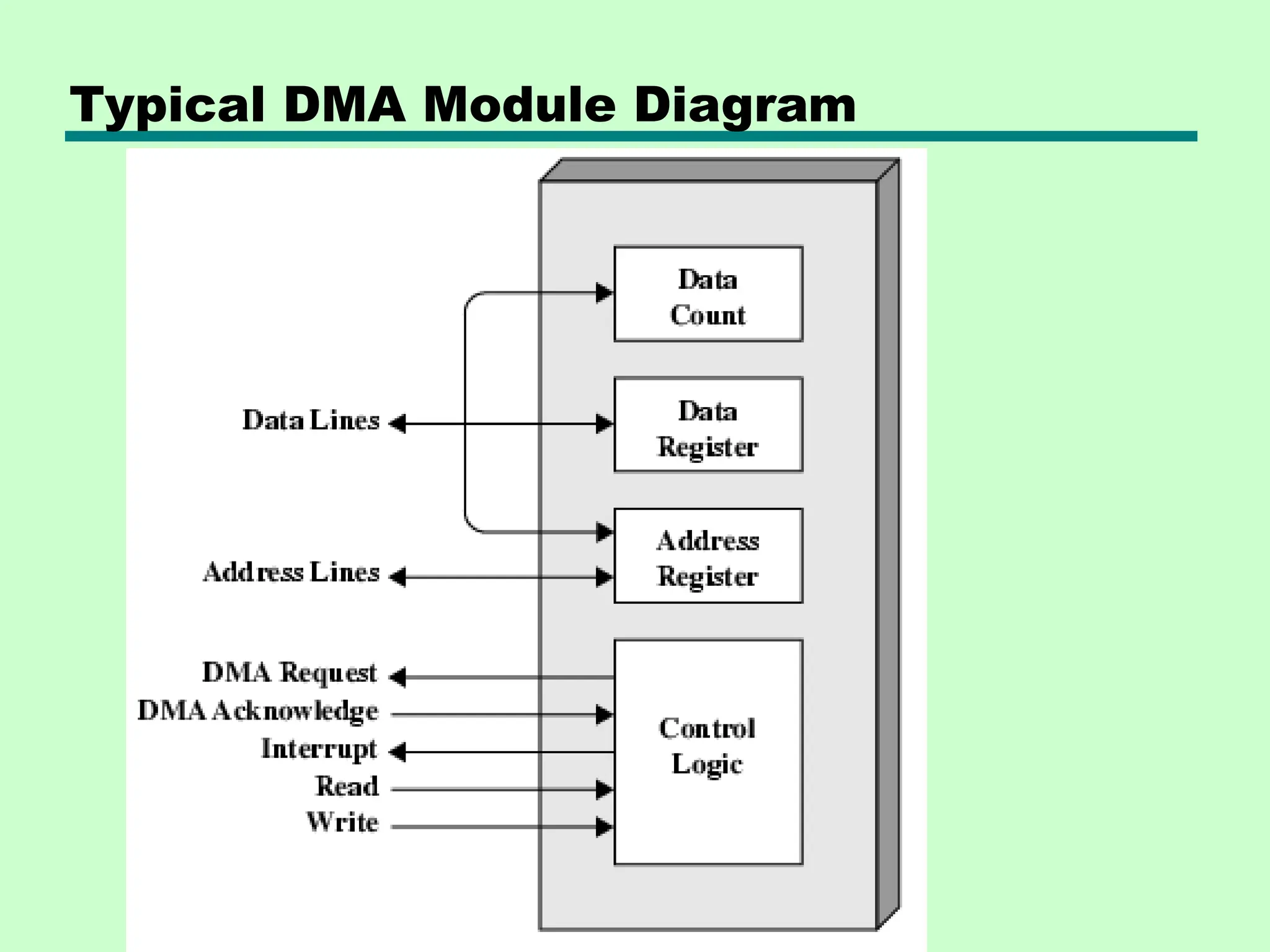

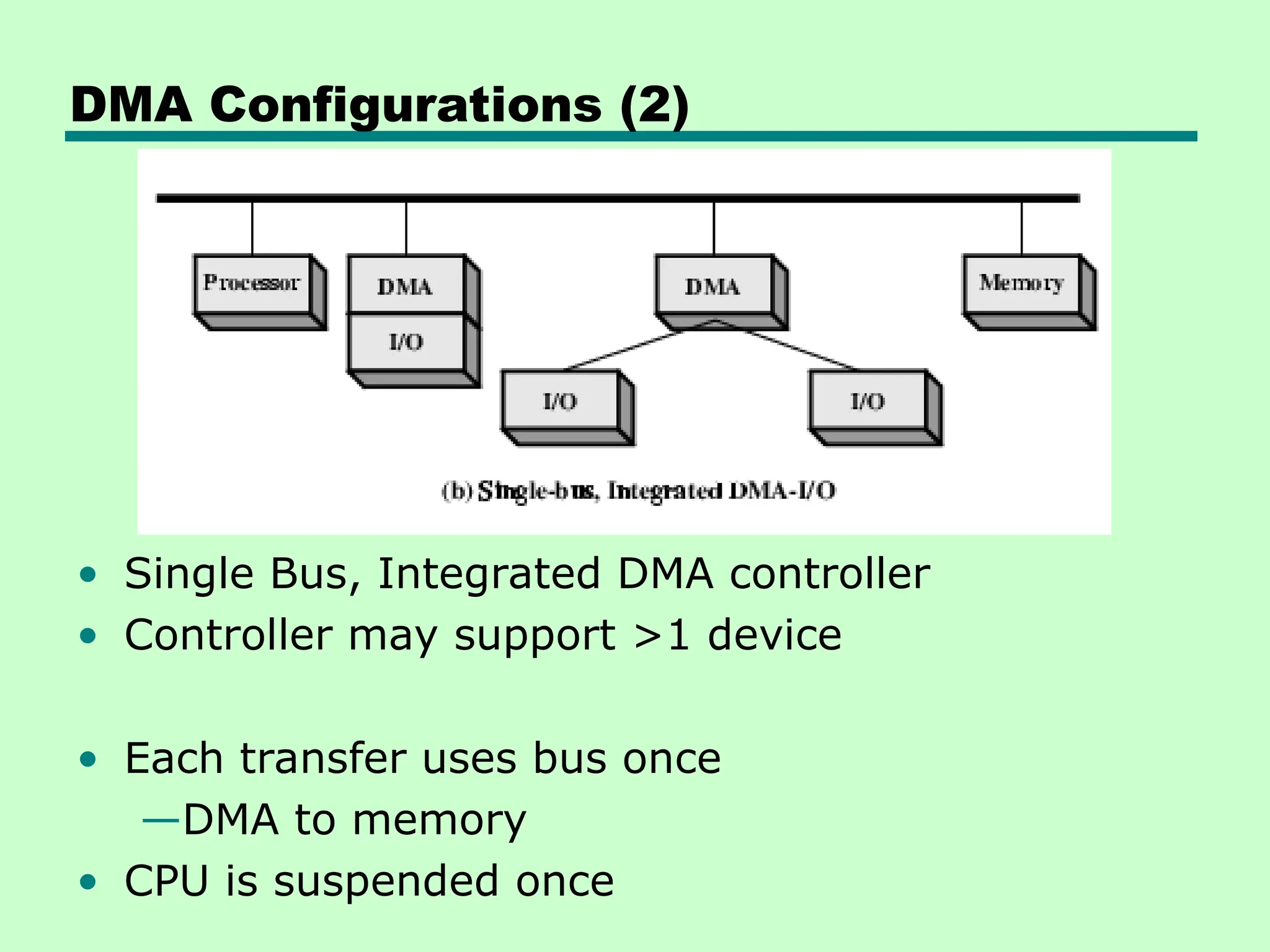

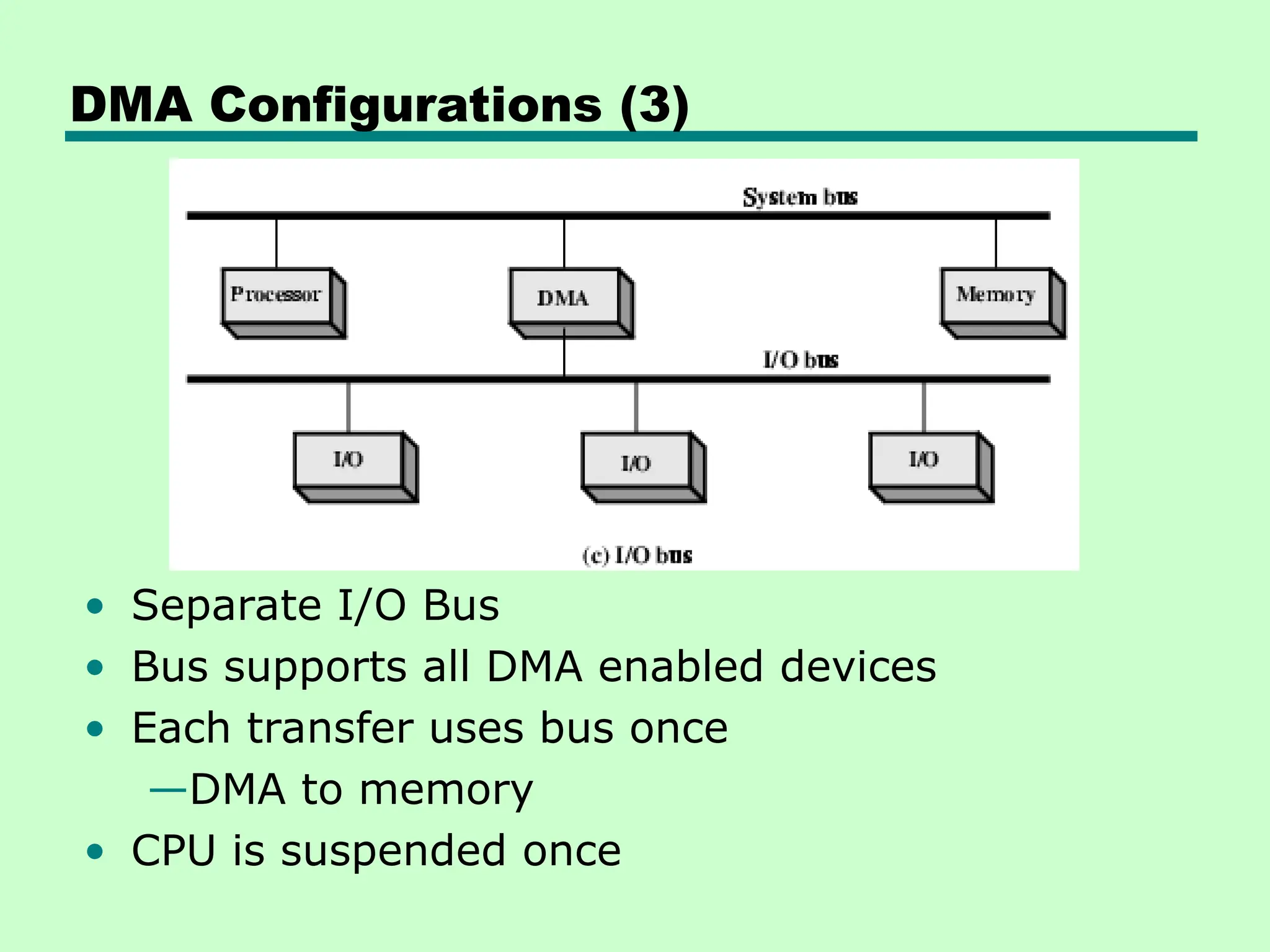

The document covers input/output (I/O) organization and various techniques for handling I/O operations in computer systems. It explains the functions of I/O modules, including control, communication, and error detection, as well as different I/O techniques such as programmed, interrupt-driven, and direct memory access (DMA). Additionally, it discusses the challenges of interrupt handling, device identification, and various DMA configurations to optimize data transfer without extensive CPU intervention.