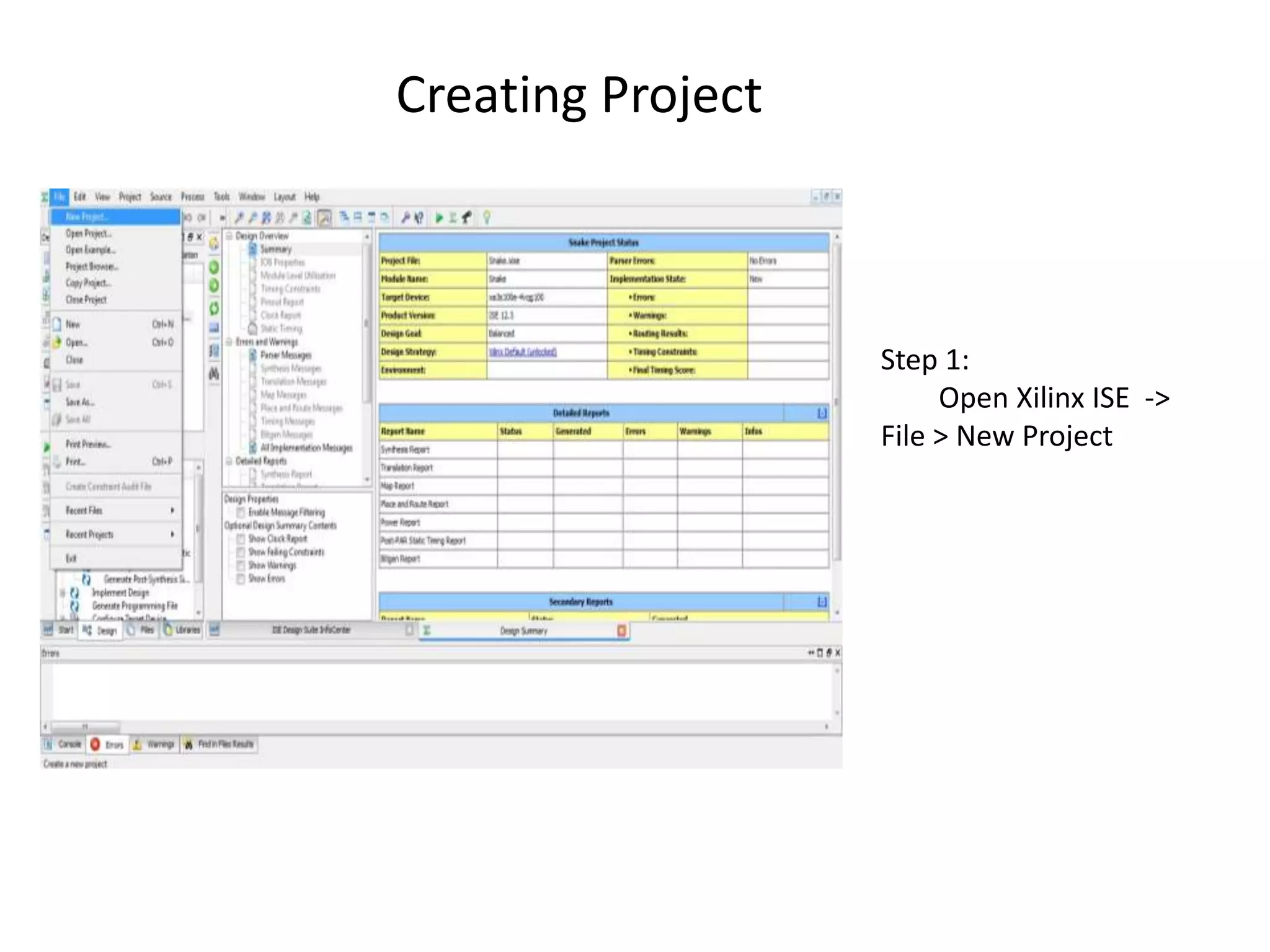

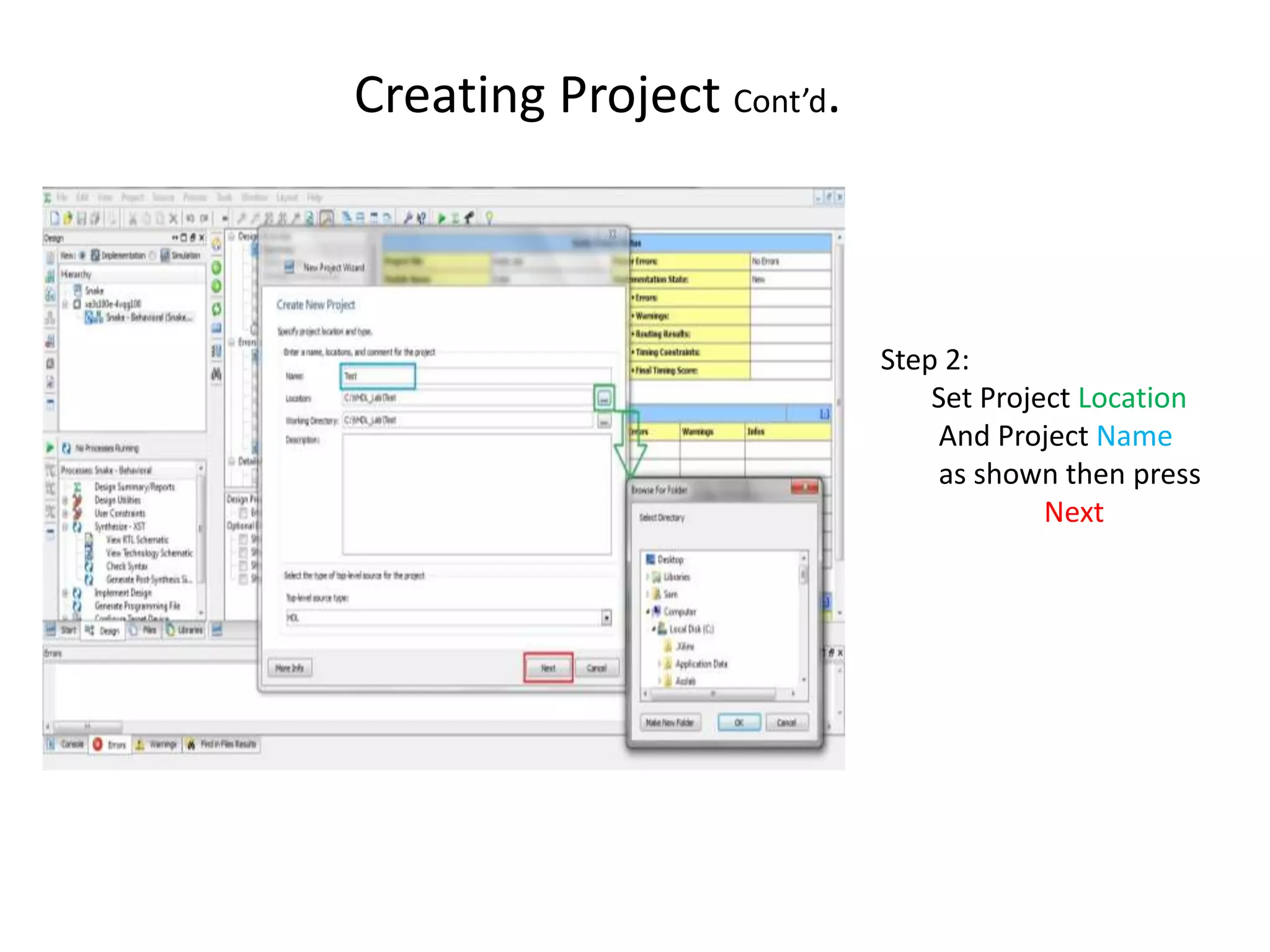

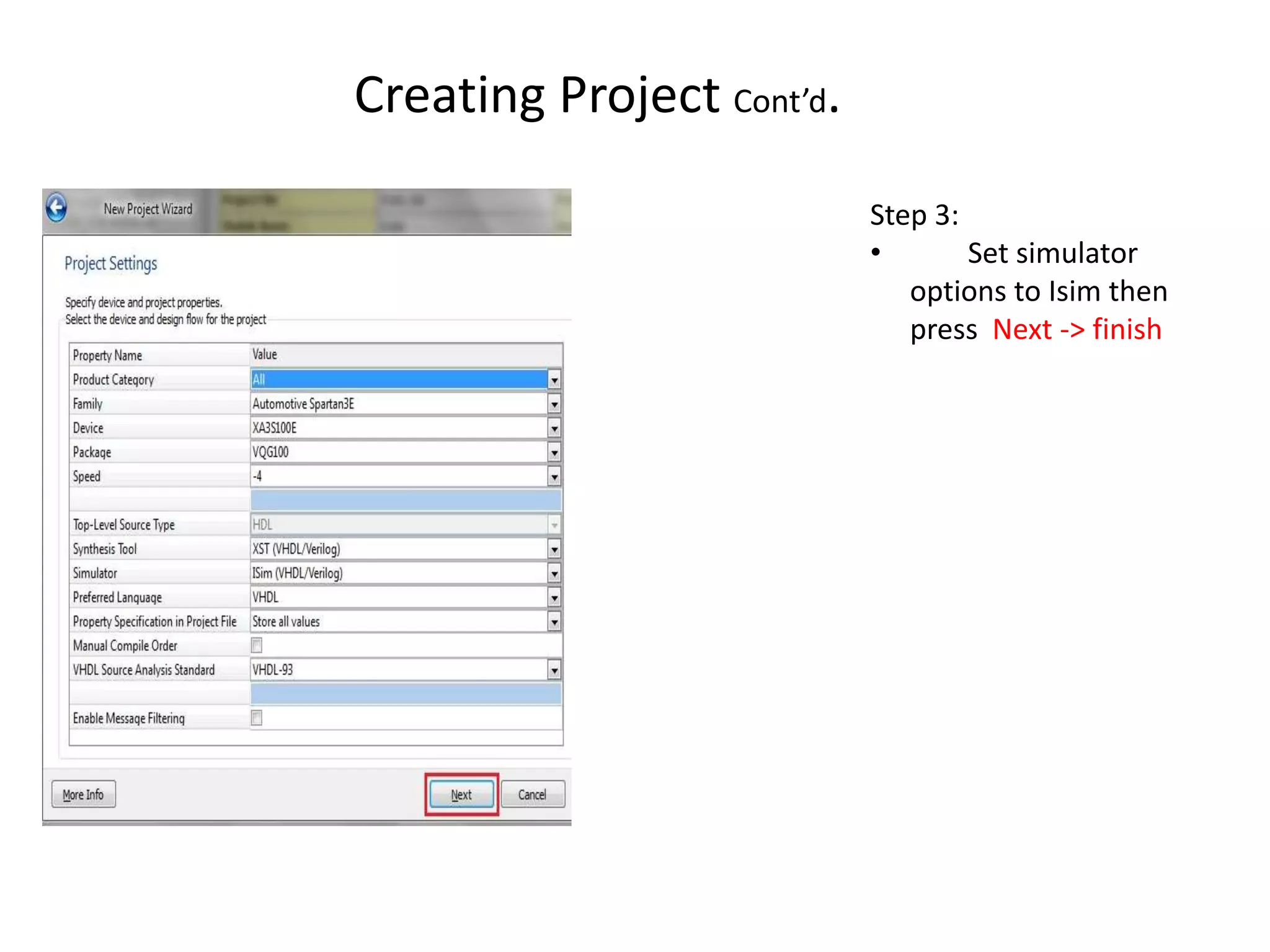

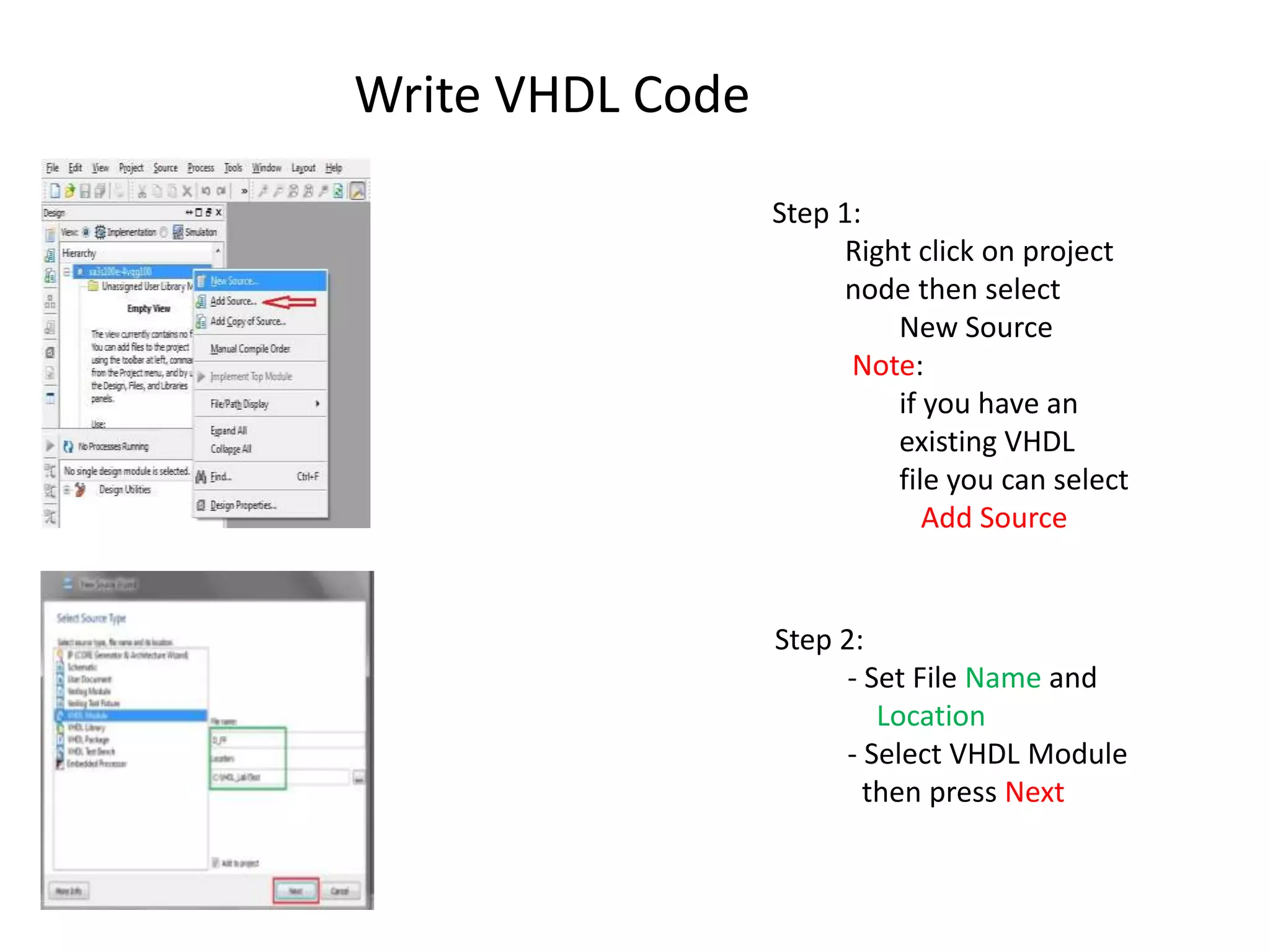

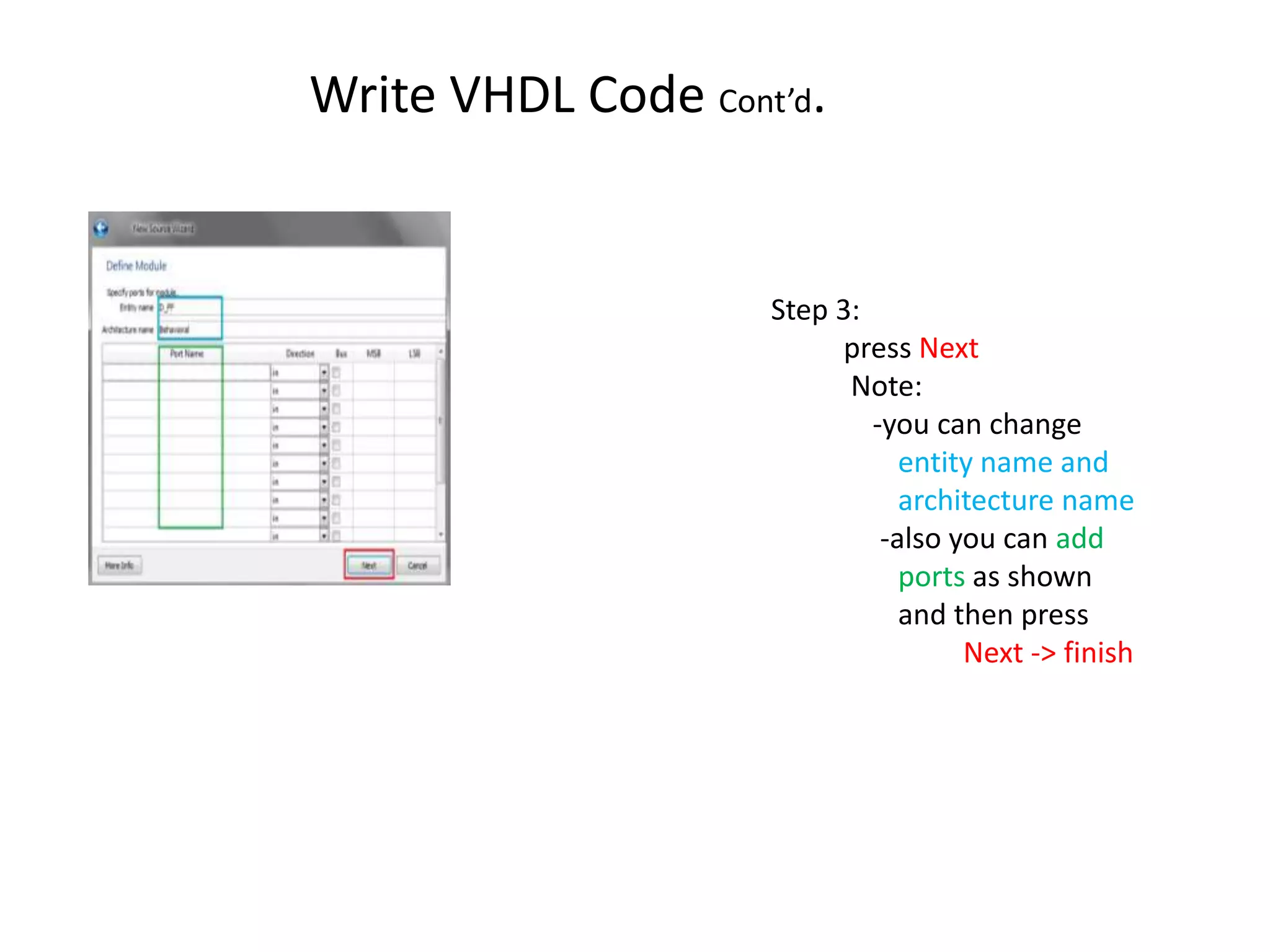

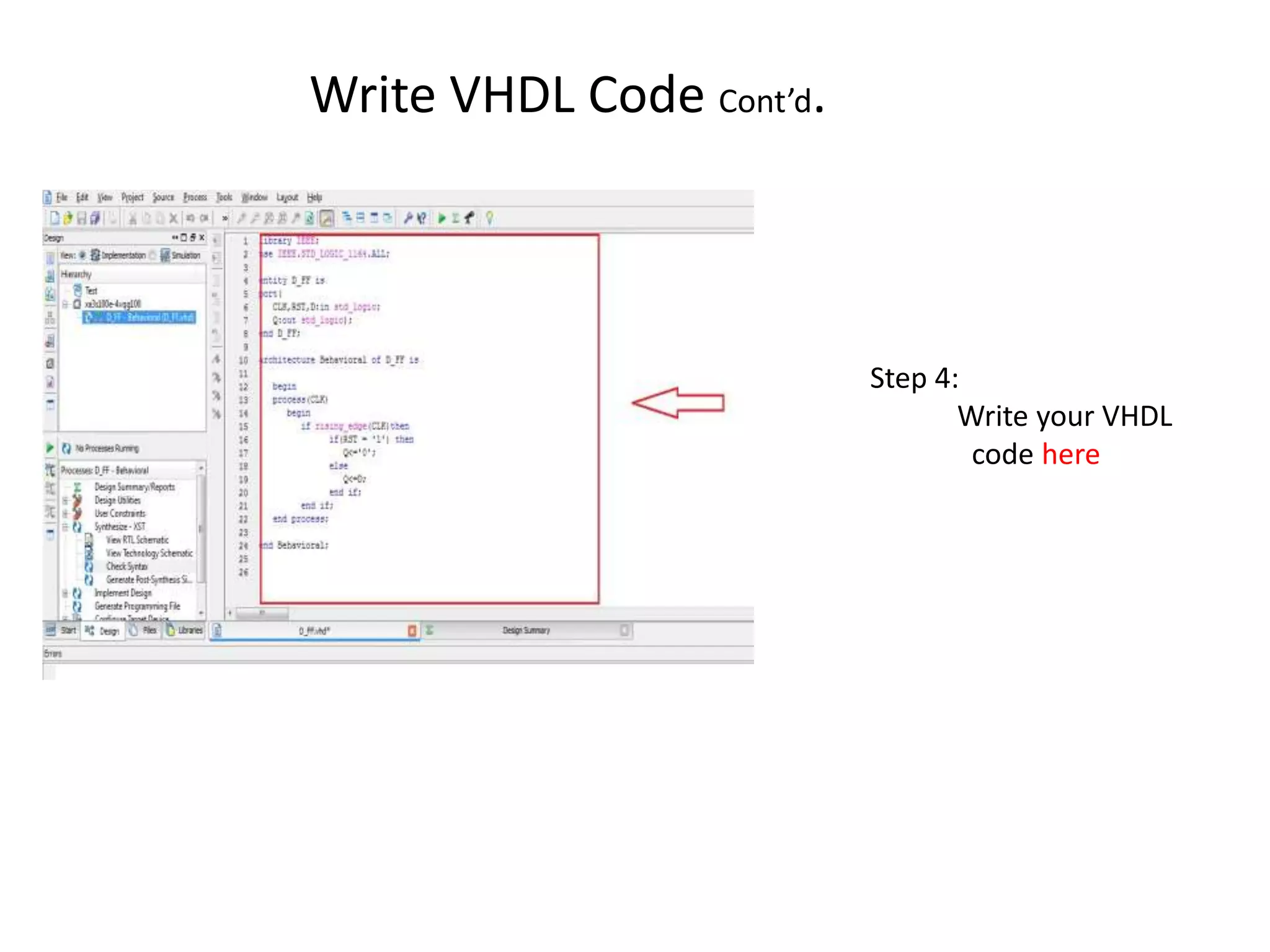

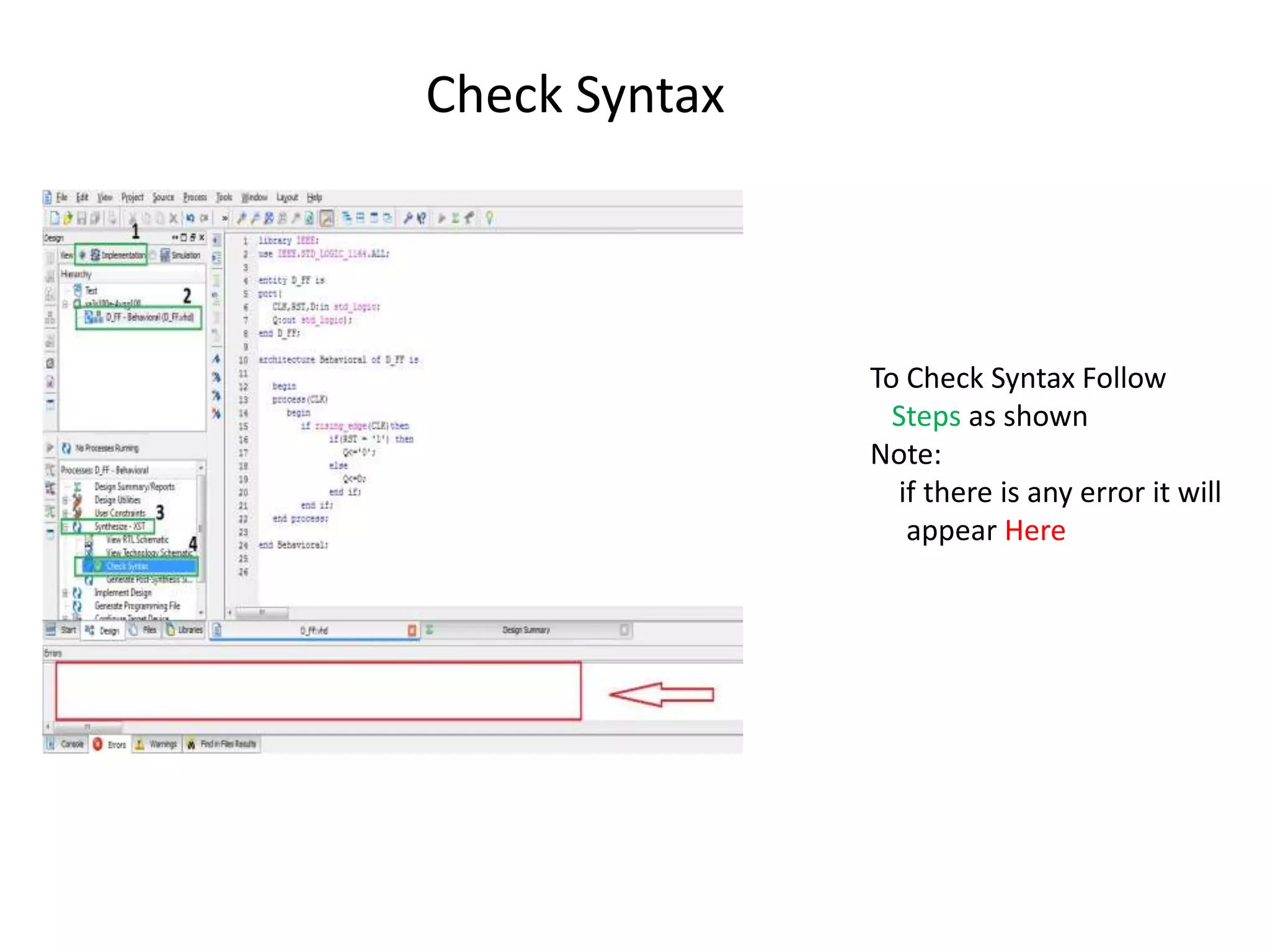

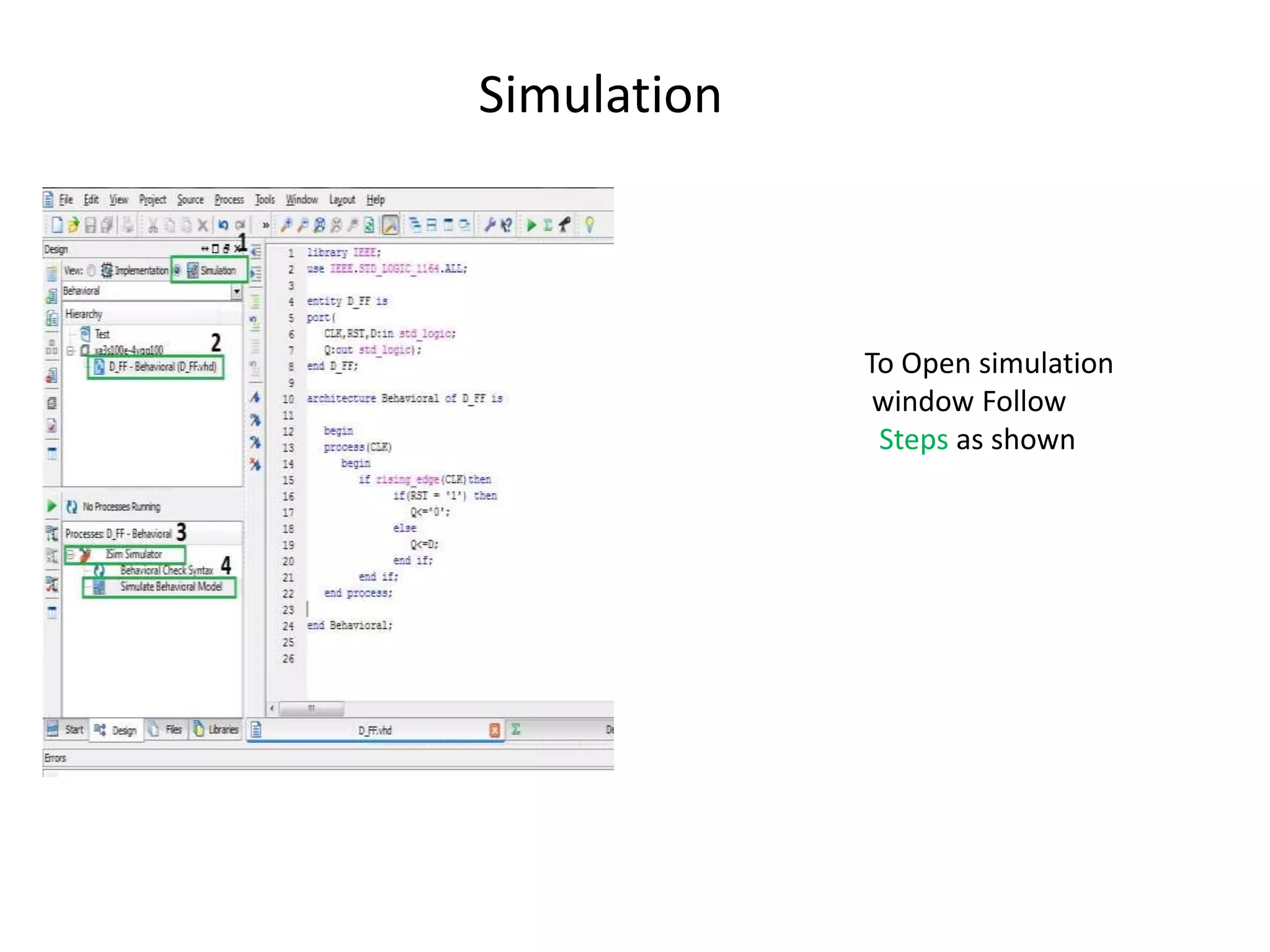

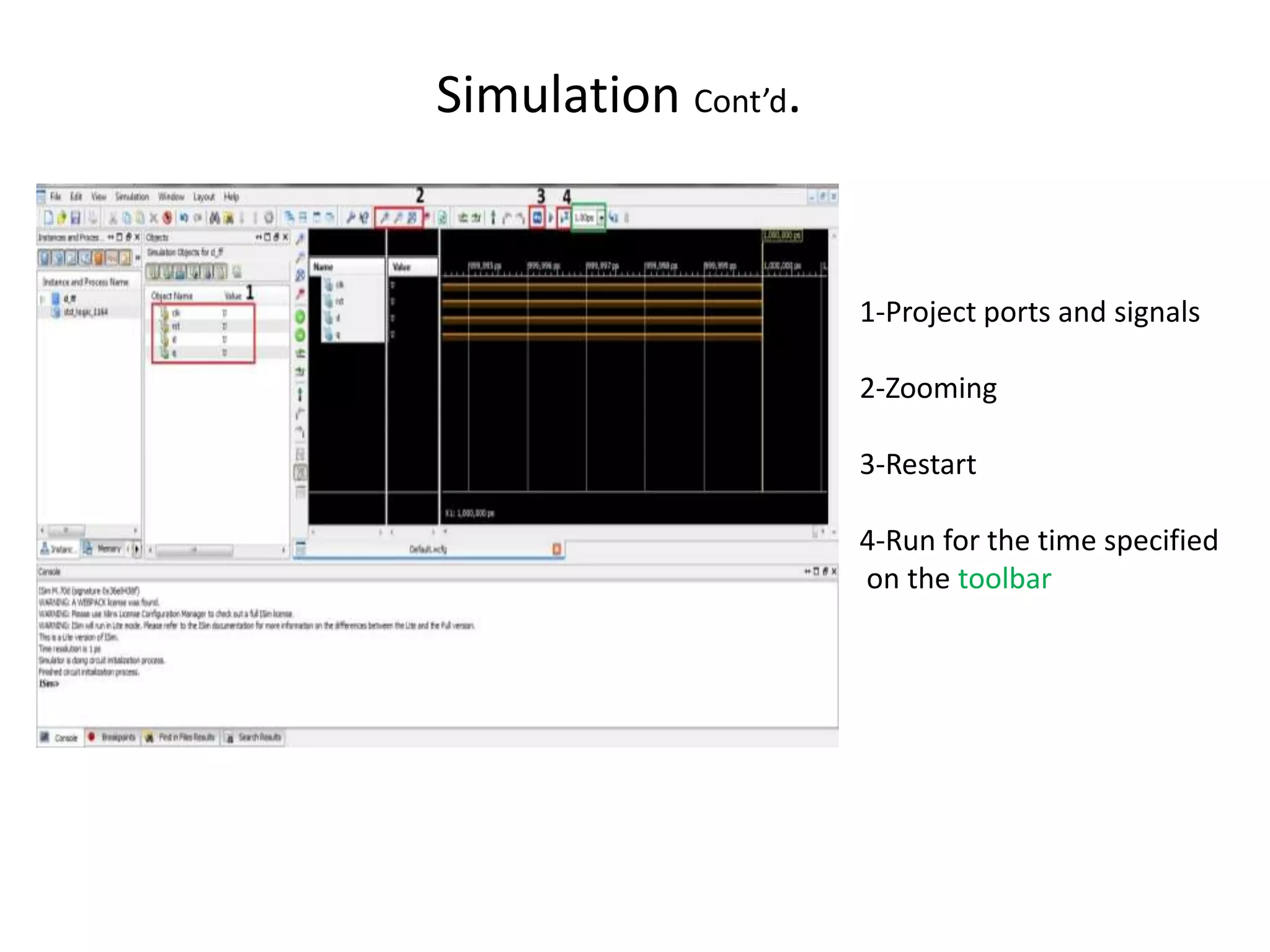

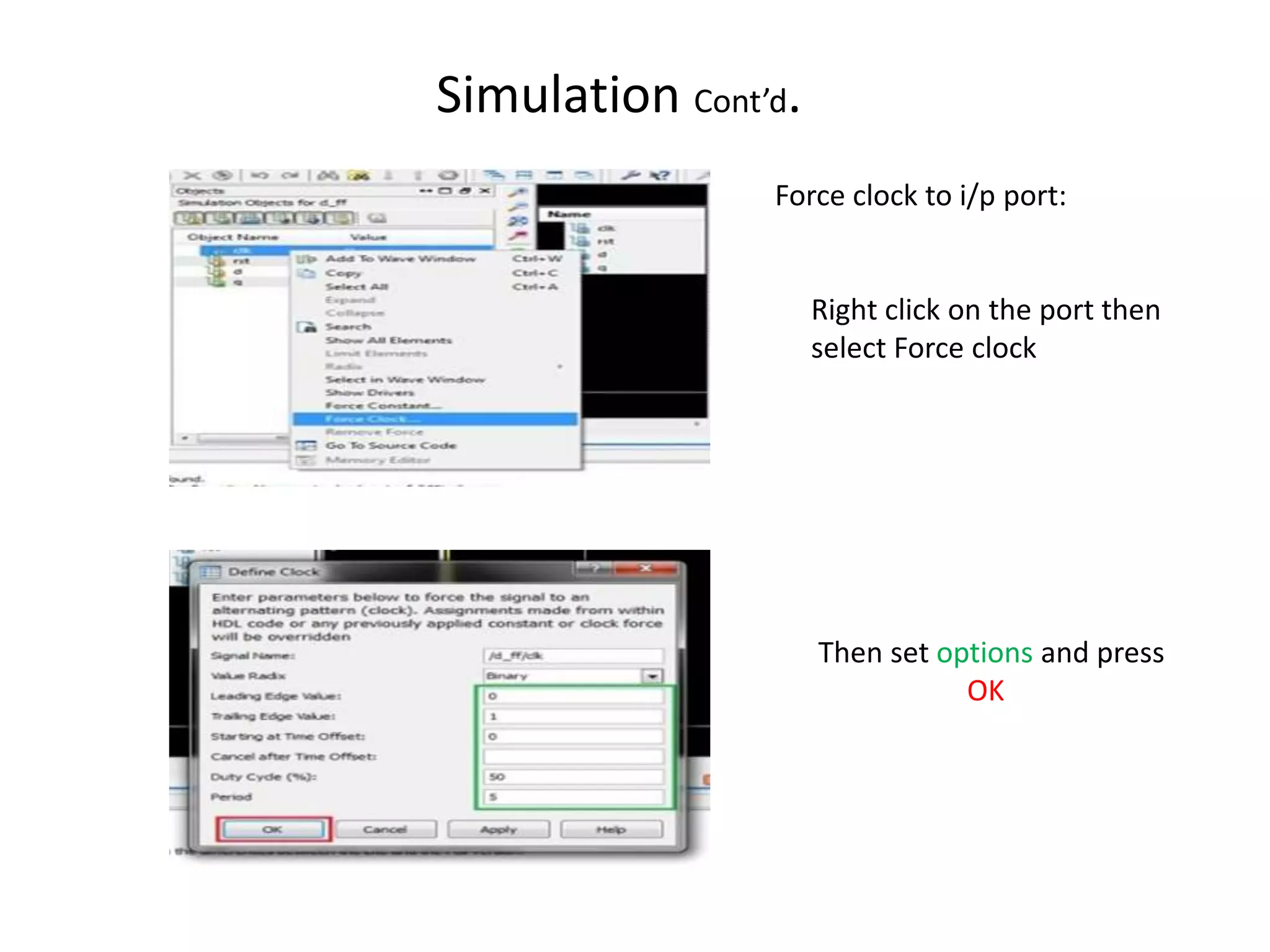

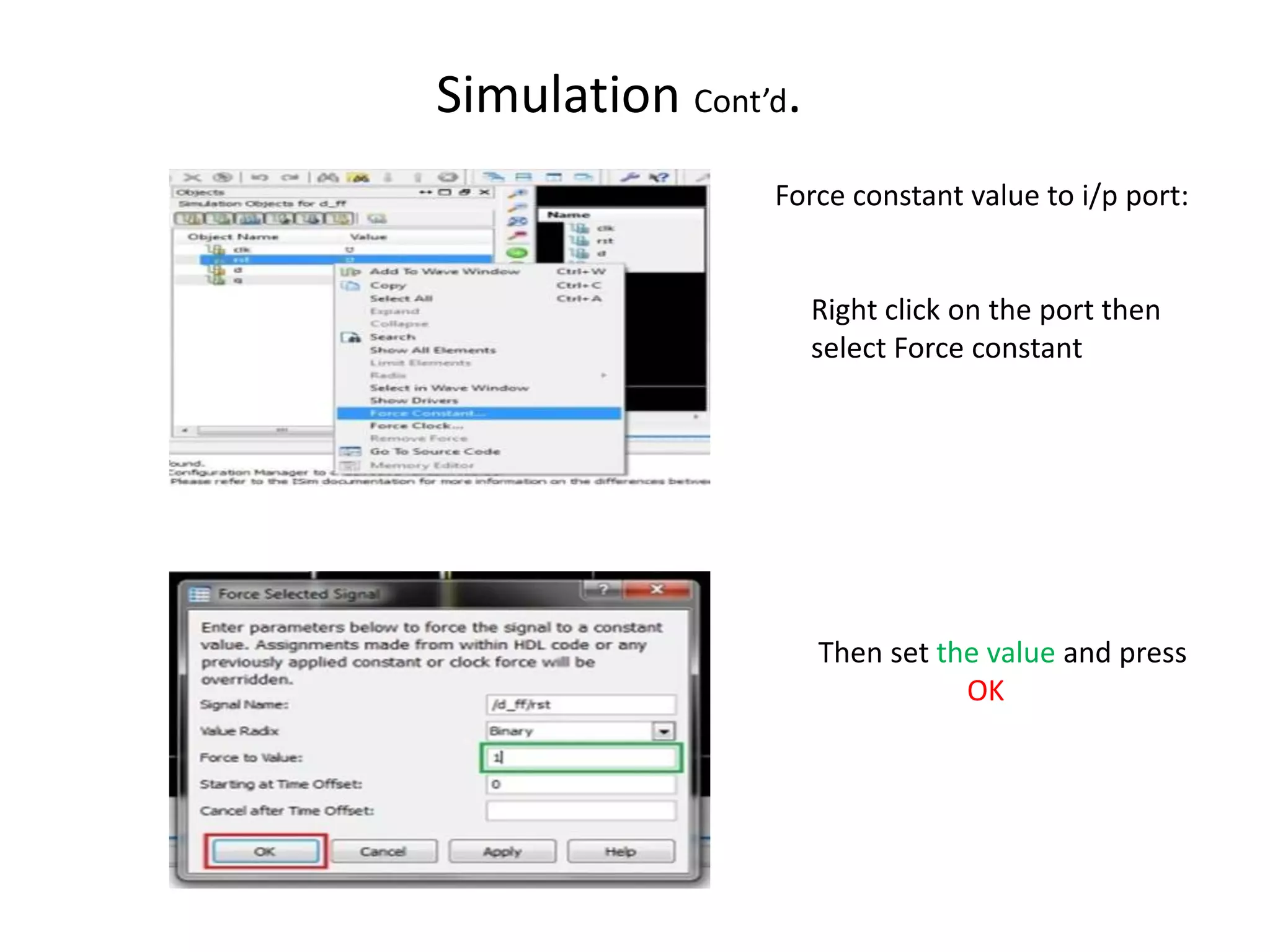

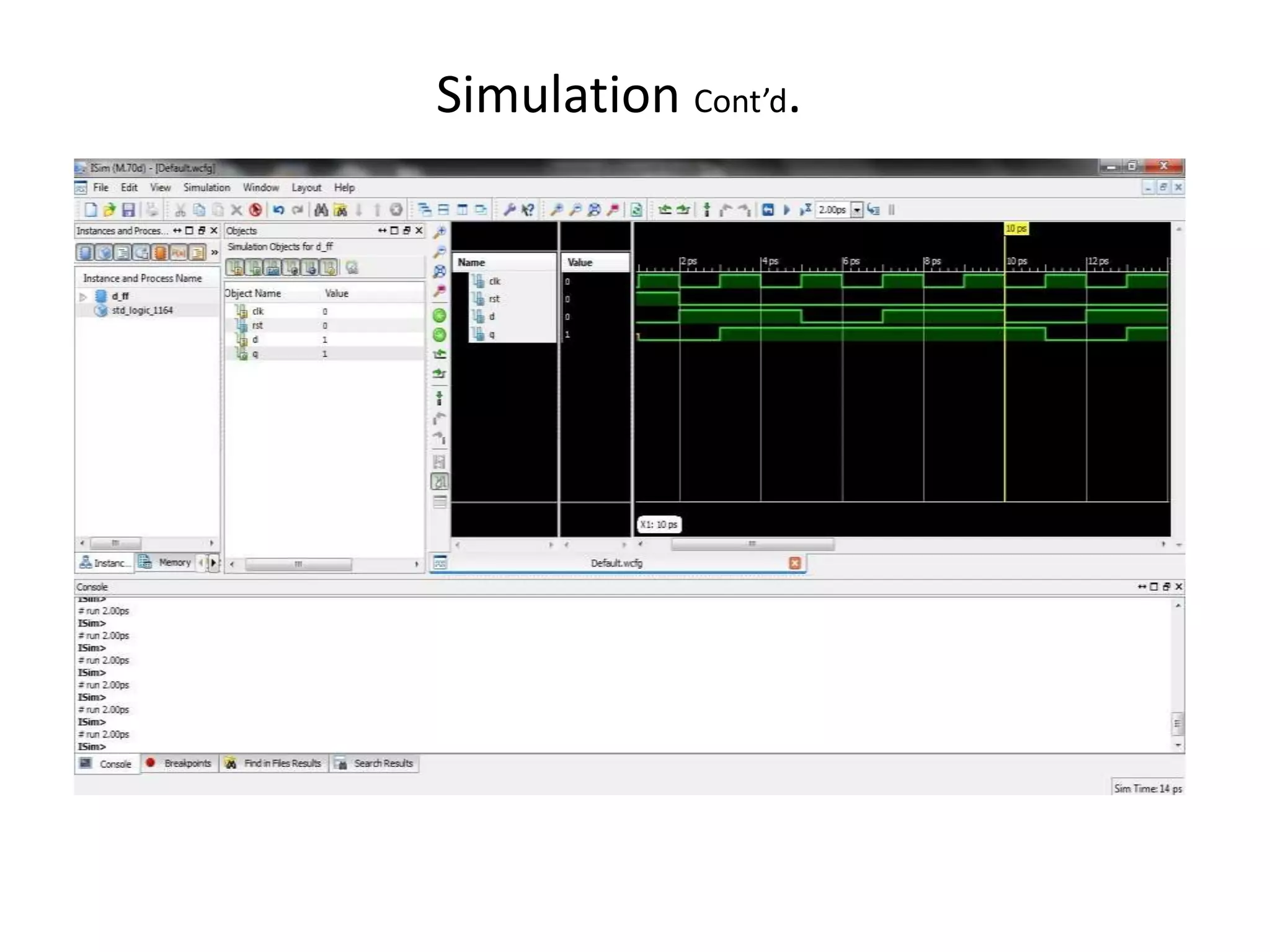

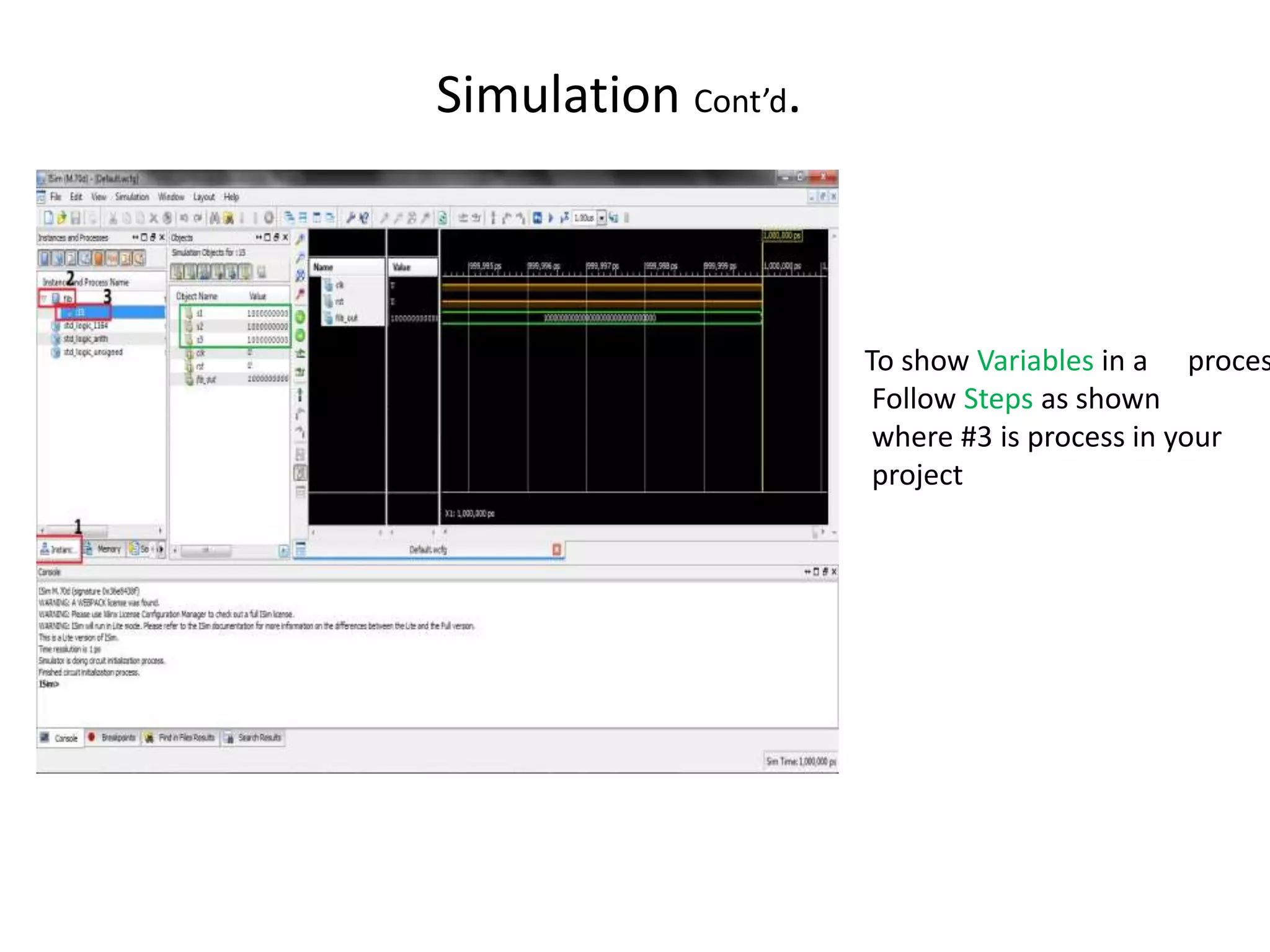

This document provides an overview of using the Isim simulator to simulate VHDL designs. It describes creating a new project in Xilinx ISE, writing VHDL code, checking for syntax errors, and performing an interactive simulation. The simulation involves forcing clock and constant inputs, zooming the waveform display, and viewing variables within processes. The overall objective is to learn the basic flow for using the Isim simulator to compile and simulate a VHDL design.