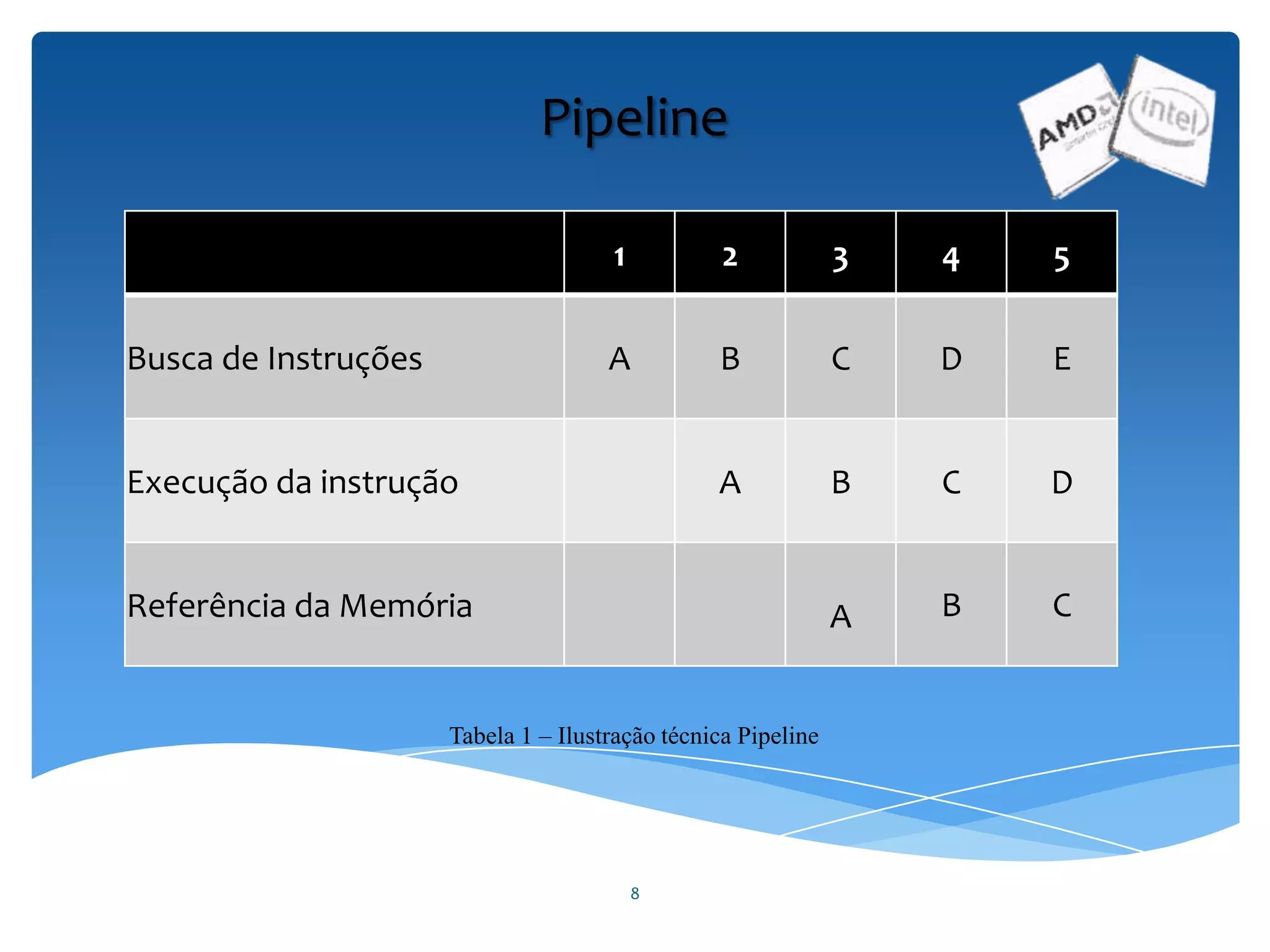

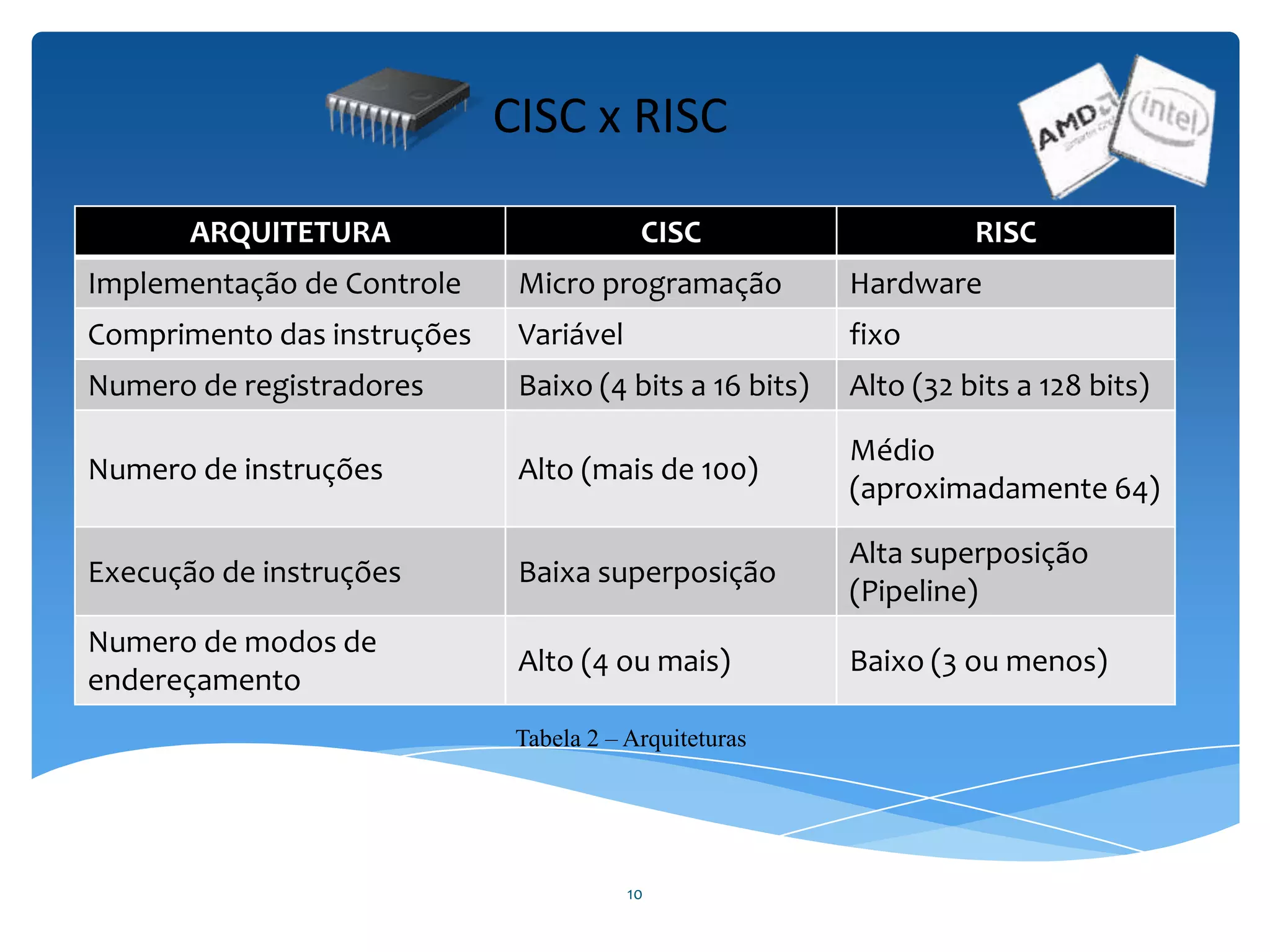

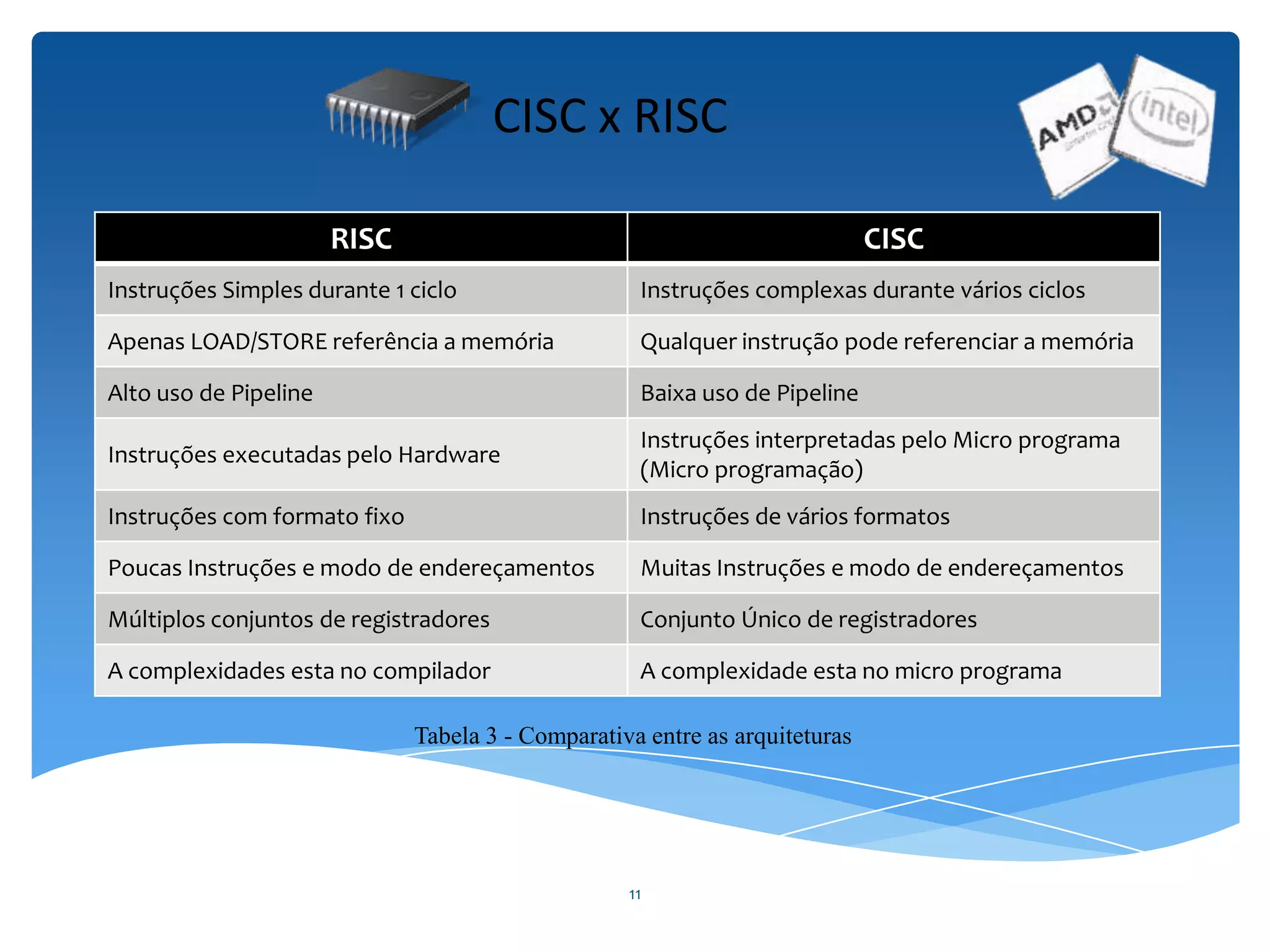

O documento discute as arquiteturas de processadores CISC (Complex Instruction Set Computer) e RISC (Reduced Instruction Set Computer), detalhando suas características, vantagens e desvantagens. Enquanto os processadores CISC são conhecidos por suas instruções complexas e maior compatibilidade, os RISC utilizam um conjunto simplificado de instruções para executar tarefas mais rapidamente através da técnica de pipelining. A comparação entre ambas as arquiteturas revela diferenças significativas em termos de execução de instruções, uso de registradores e complexidade de compiladores.