8/5/2015

The salient features of 8085 p

UNIT I

THE 8085 MICROPROCESSOR

It is a 8 bit microprocessor.

It is manufactured with N-MOS technology.

It has 16 bit address bus

Can address upto 216 = 65536 bytes (64KB) memory locations through A0A15

The first 8 lines of address bus and 8 lines of data bus are multiplexed AD0

AD7

Data bus is a group of 8 lines D0 D7

It supports external interrupt request.

D.Shiloah Elizabeth, DCSE/AU

The salient features of 8085 p

The salient features of 8085 p

It has the following registers

Memory:

Program, data and stack memories occupy the same memory space. The total

addressable memory size is 64 KB.

A 16 bit program counter (PC)

A 16 bit stack pointer (SP)

Six 8-bit general purpose register arranged in pairs: BC, DE, HL.

Program memory - program can be located anywhere in memory.

Jump, branch and call instructions use 16-bit addresses, i.e. they can be used to

jump/branch anywhere within 64 KB.

All jump/branch instructions use absolute addressing.

It requires a signal +5V power supply and operates at 6.144 MHZ

single phase clock.

It is enclosed with 40 pins Dual in line package (DIP).

Data memory - the processor always uses 16-bit addresses so that data can

be placed anywhere.

Stack memory is limited only by the size of memory.

Stack grows downward.

First 64 bytes in a zero memory page should be reserved for vectors used

by RST instructions.

D.Shiloah Elizabeth, DCSE/AU

D.Shiloah Elizabeth, DCSE/AU

�8/5/2015

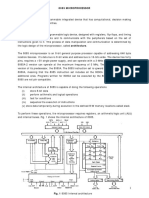

Signal Groups:

8085 Pin diagram

Address bus

A15-A8, AD7-AD0

Multiplexed address/data bus:

AD7-AD0

Control and status signals

ALE, RD, WR, IO/M, S1, S0

Power supply and clock frequency

VCC, VSS, X1, X2, CLK (OUT)

Externally initiated signals:

Input: TRAP, RST 7.5, RST 6.5, RST 5.5,

INTR, READY, HOLD

Output: INTA, HLDA

Reset: RESET IN, RESET OUT

Serial I/O ports:

SID, SOD

D.Shiloah Elizabeth, DCSE/AU

Data flow from

memory to the

MPU

MOV C,A

Opcode: 4FH

D.Shiloah Elizabeth, DCSE/AU

D.Shiloah Elizabeth, DCSE/AU

Steps For Fetching an Instruction

Instruction at memory location 2005. i.e., program counter: 2005H.

The following is the sequence of operations:

The program counter places the address value on the address

bus.

The control unit issues a RD signal.

The byte in the memory location is placed on the data bus.

The value on the data bus is read into the instruction decoder

inside the microprocessor.

After decoding the instruction, the control unit issues the

proper control signals to perform the operation.

D.Shiloah Elizabeth, DCSE/AU

�8/5/2015

Timing Signals For Fetching an Instruction

Timing:

Transfer of byte

from memory to

MPU

MOV C,A

Opcode: 4FH

D.Shiloah Elizabeth, DCSE/AU

At T1 ,

The high order 8 address bits (20H) are placed on the address lines

A8 A15 and the low order bits are placed on AD7AD0

The ALE signal goes high to indicate that AD0 AD8 are carrying

an address

The IO/M signal goes low to indicate a memory operation

At the beginning of the T2 cycle,

The low order 8 address bits are removed from AD7 AD0

The control unit sends the Read (RD) signal to the memory. The

signal remains low (active) for two clock periods to allow for slow

devices

D.Shiloah Elizabeth, DCSE/AU

10

Timing Signals For Fetching an Instruction (Contd.)

Demultiplexing

the bus AD7AD0

During T2 ,

Memory places the data from the memory location on the lines

AD7 AD0

During T3,

The RD signal is Disabled (goes high). This turns off the output Tristate buffers in the memory. That makes the AD7 AD0 lines go to

high impedence mode

During T4

The machine code or the byte is decoded by the instruction

decoder and the task is carried out based on the bit pattern

D.Shiloah Elizabeth, DCSE/AU

Schematic of

latching loworder address

bus

11

D.Shiloah Elizabeth, DCSE/AU

12

�8/5/2015

Cycles and States

From the above discussion, we can define terms that will become handy

later on:

T- State: One subdivision of an operation. A T-state lasts for one clock

period.

An instructions execution length is usually measured in a number of

T-states. (clock periods).

Machine Cycle: The time required to complete one operation of

accessing memory, I/O, or acknowledging an external request.

This cycle may consist of 3 to 6 T-states.

Instruction Cycle: The time required to complete the execution of an

instruction.

In the 8085, an instruction cycle may consist of 1 to 6 machine

cycles.

D.Shiloah Elizabeth, DCSE/AU

Schematic to generate Read/ write

control signals for M and I/O

13

Demultiplexed address and data bus

with control signals

D.Shiloah Elizabeth, DCSE/AU

14

8085A Microprocessor: Functional Block diagram

D7

D6

D5

D4

D3

D2

Ac

D1

D0

CY

Flag Register

D.Shiloah Elizabeth, DCSE/AU

15

D.Shiloah Elizabeth, DCSE/AU

16

�8/5/2015

Hardware Model

Instruction decoding and Execution

D.Shiloah Elizabeth, DCSE/AU

17

Programming Model

D.Shiloah Elizabeth, DCSE/AU

Instruction classification

Instruction word size

Data transfer operations

Arithmetic operations

Logical operations

Branching operations

Machine control operations

One-byte instructions

Two-byte instructions

Three-byte instructions

D.Shiloah Elizabeth, DCSE/AU

19

D.Shiloah Elizabeth, DCSE/AU

18

20

�8/5/2015

Data transfer instructions

Data transfer instructions

Copy from source to destination

Load accumulator

Move immediate 8-bit

MOV Rd, Rs

MOV M, Rs

MOV Rd, M

MVI Rd, data

MVI M, data

MOV B,C

MOV B,M

MVI B, 57

MVI M, 57

Load accumulator indirect

LDA 16-bit address

LDAX B/D register pair

LDA 4200H

LDAX B

Load register pair immediate

D.Shiloah Elizabeth, DCSE/AU

21

Load H and L registers direct

LXI Reg. pair, 16-bit data

LHLD 16-bit address

LXI H, 2034

LHLD 2040

D.Shiloah Elizabeth, DCSE/AU

Data transfer instructions

Data transfer instructions

Store accumulator direct

STA 16-bit address

STA 4350

STA XYZ

Store accumulator indirect

STAX Reg. pair

STAX B

Copy H and L registers to the

stack pointer

SPHL none

SPHL

Exchange H and L with top of

stack

XTHL none

XTHL

Store H and L registers direct

SHLD 16-bit address

SHLD 2470

Exchange H and L with D and E

XCHG none

XCHG

Push register pair onto stack

PUSH Reg. pair

PUSH B

PUSH A

Exchange H and L with D and E

POP Reg. pair

POP H

POP A

D.Shiloah Elizabeth, DCSE/AU

23

D.Shiloah Elizabeth, DCSE/AU

22

24

�8/5/2015

Data transfer instructions

Arithmetic instructions

Output data from accumulator

to a port with 8-bit address

Add register or memory to

accumulator

ADD R

ADD M

ADD B

ADD M

Add register to accumulator with

carry

ADC R

ADC M

ADC B

ADC M

Add immediate to accumulator

ADI 8-bit data

Add immediate to accumulator

with carry

ACI 8-bit data

Input data to accumulator from

a port with 8-bit address

OUT 8-bit port address

IN 8-bit port address

OUT 87

IN 82

ADI 45

D.Shiloah Elizabeth, DCSE/AU

25

Arithmetic instructions

Add register pair to H and L

registers

DAD Reg. pair

DAD H

ACI 45

D.Shiloah Elizabeth, DCSE/AU

26

Arithmetic instructions

Decimal adjust accumulator

DAA none

DAA

If the result is larger than 16 bits,

the CY flag is set.

No other flags are affected.

Subtract register or memory

from accumulator

SUB R

SUB M

SUB B

SUB M

Subtract source and borrow

from accumulator

SBB R

SBB M

SBB B

SBB M

Subtract immediate from

accumulator

SUI 8-bit data

Subtract immediate from

accumulator with borrow

SBI 8-bit data

SBI 45

SUI 45

D.Shiloah Elizabeth, DCSE/AU

27

D.Shiloah Elizabeth, DCSE/AU

28

�8/5/2015

Arithmetic instructions

Branching instructions

Increment register or memory

by 1

INR R

INR M

INR B

INR M

Increment register pair by 1

INX R

INX H

Decrement register or memory

by 1

DCR R

DCR M

DCR B

DCR M

Decrement register pair by 1

DCX R

DCX H

D.Shiloah Elizabeth, DCSE/AU

JMP 16-bit address

JMP 2034

JMP label

29

Branching instructions

Unconditional subroutine call

CALL 16-bit address

CALL 2034

CALL label

Jump conditionally

Operand: 16-bit address

Opcode Description

Flag Status

JC

Jump on Carry

CY = 1

JNC

Jump on no Carry CY = 0

JP

Jump on positive

S=0

JM

Jump on minus

S=1

JZ

Jump on zero

Z=1

JNZ

Jump on no zero

Z=0

JPE

Jump on parity even P = 1

JPO

Jump on parity odd P = 0

Jump unconditionally

D.Shiloah Elizabeth, DCSE/AU

30

Branching instructions

Call conditionally

Operand: 16-bit address

Opcode Description

Flag Status

CC

Call on Carry

CY = 1

CNC

Call on no Carry

CY = 0

CP

Call on positive

S=0

CM

Call on minus

S=1

CZ

Call on zero

Z=1

CNZ

Call on no zero

Z=0

CPE

Call on parity even P = 1

CPO

Call on parity odd P = 0

D.Shiloah Elizabeth, DCSE/AU

31

Return from subroutine

unconditionally

RET none

RET

Return from subroutine conditionally

Operand: none

Opcode Description

Flag Status

RC

Return on Carry

CY = 1

RNC Return on no Carry CY = 0

RP

Return on positive S = 0

RM

Return on minus

S=1

RZ

Return on zero

Z=1

RNZ Return on no zero Z = 0

RPE Return on parity even P = 1

RPO Return on parity odd P = 0

D.Shiloah Elizabeth, DCSE/AU

32

�8/5/2015

Branching instructions

Load program counter with HL

contents

PCHL none

PCHL

Restart

Interrupt Rst Addr

TRAP

0024H

these interrupts generate RST

RST 5.5 002CH instructions internally and

RST 6.5 0034H thus do not require any

RST 7.5 003CH external hardware.

Logical instructions

Restart

generally used in

conjunction

with

interrupts

and

inserted

using

external hardware.

can be used as

software instructions

in a program to

transfer

program

execution to one of

the eight locations.

Instr Restart Addr

RST 0 0000H

RST 1 0008H

RST 2 0010H

RST 3 0018H

RST 4 0020H

RST 5 0028H

RST 6 0030H

RST 7 0038H

D.Shiloah Elizabeth, DCSE/AU

Compare register or memory

with accumulator

CMP R

CMP M

CMP B

CMP M

Compare immediate with

accumulator

CPI 8-bit data

CPI 45

Logical AND register or memory

are modified.

with accumulator S,CYZ,isPreset.

AC is set.

ANA R

ANA M

ANA B

ANA M

Logical AND immediate with

are modified.

accumulator S,CYZ,isPreset.

AC is set.

ANI 8-bit data

ANI 07

33

Logical instructions

D.Shiloah Elizabeth, DCSE/AU

34

Logical instructions

Exclusive OR register or memory

with accumulator S, Z, P are modified.

CY and AC are reset.

XRA R

XRA M

XRA B

XRA M

Exclusive OR immediate with

S, Z, P are modified.

accumulator

CY and AC are reset.

XRI 8-bit data

XRI 86

Rotate accumulator left

RLC none

RLC

Rotate accumulator right

RRC none

RRC

Logical OR register or memory

P are modified.

with accumulator S,CYZ,and

AC are reset.

ORA R

ORA M

ORA B

ORA M

Logical OR immediate with

S, Z, P are modified.

accumulator

CY and AC are reset.

ORI 8-bit data

ORI 07

Rotate accumulator left through

carry

RAL none

RAL

Rotate accumulator right

through carry

RAR none

RAR

D.Shiloah Elizabeth, DCSE/AU

35

D.Shiloah Elizabeth, DCSE/AU

36

�8/5/2015

Logical instructions

CONTROL INSTRUCTIONS

Complement accumulator

CMA none

CMA

Complement carry

CMC none

CMC

No operation

NOP none

Halt and enter wait state

HLT none

Disable interrupts

DI none

Enable interrupts

EI none

Set Carry

STC none

STC

D.Shiloah Elizabeth, DCSE/AU

Rotate accumulator left

37

RLC

D.Shiloah Elizabeth, DCSE/AU

Rotate accumulator right

Before execution of RLC

CY

D7

D6

D5

D4

D3

D2

D1

D0

CY

B7

B6

B5

B4

B3

B2

B1

B0

CY

D7

D6

D5

D4

D3

D2

D1

D0

B7

B6

B5

B4

B3

B2

B1

B0

B7

38

RRC

Before execution of RRC

After execution of RLC

D7

D6

D5

D4

D3

D2

D1

D0

CY

B7

B6

B5

B4

B3

B2

B1

B0

CY

After execution of RRC

Each binary bit of the accumulator is rotated left by one position.

D7 is placed in the position of D0 as well as in CY.

CY is modified according to D7.

D.Shiloah Elizabeth, DCSE/AU

Read interrupt mask

RIM none

Set interrupt mask

SIM none

D7

D6

D5

D4

D3

D2

D1

D0

CY

B0

B7

B6

B5

B4

B3

B2

B1

B0

Each binary bit of the accumulator is rotated right by one position.

D0 is placed in the position of D7 as well as in CY.

CY is modified according to bit D0.

39

D.Shiloah Elizabeth, DCSE/AU

40

�8/5/2015

Rotate accumulator left through carry

Rotate accumulator right through carry

RAL

Before execution of RAL

RAR

Before execution of RAR

CY

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

CY

CY

B7

B6

B5

B4

B3

B2

B1

B0

B7

B6

B5

B4

B3

B2

B1

B0

CY

After execution of RAL

After execution of RAR

CY

D7

D6

D5

D4

D3

D2

D1

D0

D7

D6

D5

D4

D3

D2

D1

D0

CY

B7

B6

B5

B4

B3

B2

B1

B0

CY

CY

B7

B6

B5

B4

B3

B2

B1

B0

Each binary bit of the accumulator is rotated left by one position through

the Carry flag.

D7 is placed in CY, and CY is placed in D0.

CY is modified according to D7.

D.Shiloah Elizabeth, DCSE/AU

41

Each binary bit of the accumulator is rotated right by one position

through the Carry flag.

D0 is placed in CY, and CY is placed in D7.

CY is modified according to D0.

D.Shiloah Elizabeth, DCSE/AU

42

Addressing Modes of 8085

To perform any operation, we have to give the corresponding

instructions to the microprocessor.

In each instruction, programmer has to specify 3 things:

Operation to be performed

Address of source of data

Address of destination of result

ADDRESSING MODES

D.Shiloah Elizabeth, DCSE/AU

43

D.Shiloah Elizabeth, DCSE/AU

44

�8/5/2015

Addressing Modes of 8085

Addressing Modes of 8085

The method by which the address of source of data or the address of

destination of result is given in the instruction is called Addressing

Modes of 8085.

Intel 8085 uses the following addressing modes:

1. Direct Addressing Mode

2. Register Addressing Mode

3. Register Indirect Addressing Mode

4. Immediate Addressing Mode

5. Implicit Addressing Mode

The term addressing mode refers to the way in which the operand of

the instruction is specified.

D.Shiloah Elizabeth, DCSE/AU

45

D.Shiloah Elizabeth, DCSE/AU

Addressing Modes of 8085

Addressing Modes of 8085

Direct Addressing Mode

In this mode, the address of the operand is given in the instruction

itself.

LDA 4500H

LDA is the operation.

4500 H is the address of source.

Accumulator is the destination.

Register Addressing Mode

In this mode, the operand is in general purpose register.

MOV A,B

MOV is the operation.

B is the source of data.

A is the destination.

D.Shiloah Elizabeth, DCSE/AU

47

D.Shiloah Elizabeth, DCSE/AU

46

48

�8/5/2015

Addressing Modes of 8085

Addressing Modes of 8085

Register Indirect Addressing Mode

In this mode, the address of operand is specified by a register pair.

MOV A,M

MOV is the operation.

M is the memory location specified by H-L register pair.

A is the destination.

Immediate Addressing Mode

In this mode, the operand is specified within the instruction itself.

MVI A,05H

MVI is the operation.

05 H is the immediate data (source).

A is the destination.

D.Shiloah Elizabeth, DCSE/AU

49

D.Shiloah Elizabeth, DCSE/AU

50

Addressing Modes of 8085

Implicit/Implied Addressing Mode

If address of source of data as well as address of destination of result

is fixed, then there is no need to give any operand along with the

instruction.

CMA

CMA is the operation.

A is the source.

A is the destination.

D.Shiloah Elizabeth, DCSE/AU

Timing Diagram

Timing diagram is the display of initiation of read/write and transfer of data

operations under the control of 3-status signals IO / M , S1, and S0.

51

D.Shiloah Elizabeth, DCSE/AU

52

�8/5/2015

Cycles and States

T- State: One subdivision of an operation. A T-state lasts for one clock

period.

An instructions execution length is usually measured in a number of T-states.

(clock periods).

Machine Cycle: The time required to complete one operation of

accessing memory, I/O, or acknowledging an external request.

This cycle may consist of 3 to 6 T-states.

Instruction Cycle: The time required to complete the execution of an

instruction.

Operations

Opcode Fetch

Memory Read

Memory Write

I/O Read

I/O Write

In the 8085, an instruction cycle may consist of 1 to 6 machine cycles.

D.Shiloah Elizabeth, DCSE/AU

53

D.Shiloah Elizabeth, DCSE/AU

54

Opcode Fetch Machine Cycle

D.Shiloah Elizabeth, DCSE/AU

55

D.Shiloah Elizabeth, DCSE/AU

56

�8/5/2015

Memory Read Machine Cycle

D.Shiloah Elizabeth, DCSE/AU

Memory Write Machine Cycle

57

I/O Read Machine Cycle

D.Shiloah Elizabeth, DCSE/AU

D.Shiloah Elizabeth, DCSE/AU

58

I/O Write Machine Cycle

59

D.Shiloah Elizabeth, DCSE/AU

60

�8/5/2015

MVI A, 45H

M1: opcode fetch

M2: memory read

2 MCs

4+3 = 7 T-states

STA 5000H

LHLD

SHLD

STA

STAX

LDA

LDAX

LXI

M1: opcode fetch

M2: memory read

M3: memory read

M4: memory write

4 MCs

4+3+3+3 = 13 T-states

D.Shiloah Elizabeth, DCSE/AU

61

D.Shiloah Elizabeth, DCSE/AU

62

Counters - Using a Register as a Loop Counter

A loop counter is set up by loading a register with a certain value

Then using the DCR (to decrement) or INR (to increment) the

contents of the register are updated.

A loop is set up with a conditional jump instruction that loops

back or not depending on whether the count has reached the

termination count.

Counters & Time Delays

D.Shiloah Elizabeth, DCSE/AU

63

D.Shiloah Elizabeth, DCSE/AU

64

�8/5/2015

Counters

Counters

Operation of a loop counter

Sample ALP for implementing a loop

using DCR instruction

MVI C, 15H

LOOP

DCR C

JNZ LOOP

Using a single register, one can repeat a loop for a maximum

count of 255 times.

D.Shiloah Elizabeth, DCSE/AU

65

D.Shiloah Elizabeth, DCSE/AU

Counters - Using a Register Pair as a Loop Counter

Counters

It is possible to increase the count by using a register pair for the

loop counter instead of the single register.

Problem: how to test for the final count since DCX and INX do not

modify the flags?

However, if the loop is looking for when the count becomes

zero, we can apply OR between the two registers in the pair

and then check the zero flag.

The following is an example of a loop set up with a register pair

as the loop counter.

D.Shiloah Elizabeth, DCSE/AU

67

LOOP

66

LXI B, 1000H

DCX B

MOV A, C

ORA B

JNZ LOOP

D.Shiloah Elizabeth, DCSE/AU

68

�8/5/2015

Delays

Delays

Each instruction passes through different combinations of Fetch,

Memory Read, and Memory Write cycles.

Knowing the combinations of cycles, one can calculate how long such

an instruction would require to complete.

Let

Knowing how many T-States an instruction requires, and keeping in

mind that a T-State is one clock cycle long, we can calculate the time

using the following formula:

Delay = No. of T-States / Frequency

For example

B be Number of Bytes

M be Number of Machine Cycles

T be Number of T-State.

D.Shiloah Elizabeth, DCSE/AU

MVI instruction uses 7 T-States.

Therefore, if the Microprocessor is running at 2 MHz, the instruction would

require 3.5 Seconds to complete.

69

Delays Using a register

D.Shiloah Elizabeth, DCSE/AU

70

Delays Using a register

Delay loops

We can use a loop to produce a certain amount of time delay

in a program.

The following is an example of a delay loop:

MVI C, FFH

LOOP DCR C

JNZ LOOP

D.Shiloah Elizabeth, DCSE/AU

71

MVI C, FFH 7 T-States

LOOP DCR C

4 T-States

JNZ LOOP 10 T-States

The first instruction initializes the loop counter and is

executed only once requiring only 7 T-States.

The following two instructions form a loop that requires 14 TStates to execute and is repeated 255 times until C becomes 0.

D.Shiloah Elizabeth, DCSE/AU

72

�8/5/2015

Delays Using a register

Delays Using a register

In the last iteration of the loop, the JNZ instruction will fail and require only 7

T-States rather than the 10.

Therefore, we must deduct 3 T-States from the total delay to get an accurate

delay calculation.

To calculate the delay, we use the following formula:

Using these formulas, we can calculate the time delay for the previous

example:

TO= 7 T-States

Delay of the MVI instruction

Tdelay= TO+ TL

Tdelay= total delay

TO= delay outside the loop

TL= delay of the loop

TOis the sum of all delays outside the loop

D.Shiloah Elizabeth, DCSE/AU

TL= (14 X 255) -3 = 3567 T-States

14 T-States for the 2 instructions repeated 255 times (FF16= 25510) reduced by the 3 TStates for the final JNZ.

73

D.Shiloah Elizabeth, DCSE/AU

Delays Using a register pair

Delays Using a register pair

Using a Register Pair as a Loop Counter

Using the same formula from before, we can calculate:

The following is an example of a delay loop set up with a register pair as the

loop counter.

LXI B, 1000H ;10 T-States

LOOP DCX B6

;T-States

MOV A, C

;4 T-States

ORA B ;4 T-States

JNZ LOOP

;10 T-States

D.Shiloah Elizabeth, DCSE/AU

74

TO= 10 T-States

The delay for the LXI instruction

TL= (24 X 4096) -3 = 98301 T-States

24 T-States for the 4 instructions in the loop repeated 4096 times (100016= 409610)

reduced by the 3 T-States for the JNZ in the last iteration.

75

D.Shiloah Elizabeth, DCSE/AU

76

�8/5/2015

Delays Using nested loops

Delays Using nested loops

Nested Loops for Delay

The calculation remains the same except that it the formula must be

applied recursively to each loop.

Instead (or in conjunction with) Register Pairs, a nested loop structure can be

used to increase the total delay produced.

MVI B, 10H ;7 T-States

LOOP2 MVI C, FFH ;7 T-States

LOOP1 DCR C

;4 T-States

JNZ LOOP1

;10 T-States

DCR B

;4 T-States

JNZ LOOP2

;10 T-States

D.Shiloah Elizabeth, DCSE/AU

Start with the inner loop, then plug that delay in the calculation of the outer

loop.

Delay of inner loop

TO1= 7 T-States

MVI C, FFH instruction

TL1= (255 X 14) -3 = 3567 T-States

14 T-States for the DCR C and JNZ instructions repeated 255 times (FF16= 25510) minus 3

for the final JNZ

77

D.Shiloah Elizabeth, DCSE/AU

Delays Using nested loops

Delays Larger delays

Delay of outer loop

Increasing the delay

78

The delay can be further increased by using register pairs for each of the loop

counters in the nested loops setup.

It can also be increased by adding dummy instructions (like NOP) in the body

of the loop.

TO2= 7 T-States

MVI B, 10H instruction

TL1= (16 X (14 + 3574)) -3 = 57405 T-States

14 T-States for the DCR B and JNZ instructions and 3574 T-States for loop1 repeated 16 times

(1016= 1610) minus 3 for the final JNZ.

TDelay= 7 + 57405 = 57412 T-States

Total Delay TDelay= 57412 X 0.5 Sec = 28.706 mSec

D.Shiloah Elizabeth, DCSE/AU

79

D.Shiloah Elizabeth, DCSE/AU

80

�8/5/2015

Delay Subroutine

Delay Subroutine

The delay time is given by the total time taken to execute the delay

routine.

Eg. If the 8085 microprocessor has 5 MHz quartz crystal then, the

internal clock frequency = 5 /2 = 2.5 MHz

Disadvantage in delay routines:

processor time is wasted

Time for one T-state= 1 / 2.5 x 106= 0.4sec

For small time delays (< 0.5 ms) an 8- bit register can be used.

For large time delays (< 0.5 s) l6-bit register should be used.

For very large time delays (> 0.5 s), a delay routine can be repeatedly called in

the main program.

D.Shiloah Elizabeth, DCSE/AU

Solution:

use dedicated timer like 8253/8254 to produce time delays or

to maintain timings of various operations.

81

Delay Subroutine - Example

D.Shiloah Elizabeth, DCSE/AU

82

Delay Subroutine - Example

A delay routine to produce a time delay of 0.5 ms in 8085

processor-based system whose clock source is 6 MHz quartz

crystal.

The delay required is 0.5 ms, hence an 8-bit register of 8085 can

be used to store a Count value and then decrement to zero.

Delay routine

MVI D, N

; N: count

Loop: DCR D

JNZ Loop

RET

Instruction

T-State required

for execution of

an instruction

Number of

times the

instruction is

executed

Total T-States

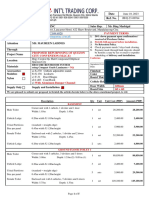

CALL addr16

18

18 x 1 = 18

MVI D, N

7x1=7

DCR D

4 x N = 4N

JNZ LOOP

10

N-1

10 x (N-1) = 10N

10

7x1=7

10

10 x 1 = 10

RET

TOTAL T-STATES FOR DELAY SUBROUTINE

D.Shiloah Elizabeth, DCSE/AU

83

D.Shiloah Elizabeth, DCSE/AU

14N + 32

84

�8/5/2015

Delay Subroutine - Calculation to find the count value, N

Counters

External clock frequency = 6 MHz

Internal clock frequency

ALP for 8085 to count from AAH to 00H, with a time delay of 2ms for

each count. Assume the external frequency given to the processor is

2MHz.

= External Frequency / 2= 6 / 2= 3 MHz

Time period for 1 T-State

= 1 / Internal clock frequency= 1 / 3x106= 0.333s

Internal Frequency in 8085 = External frequency/2

= 2MHz / 2= 1MHz

T-State= 1 / f (internal frequency)= 1s

No. of T-states required for delay of 0.5ms

= Required time delay / Time for one T-state

= 0.5ms / 0.333s= 1500.10 1500 = 150010

From above table,

14N + 32 = 1500

N = (1500 32) / 14 = 104.85710 10510= 69H

Therefore by replacing the count value, N by 69H in the above program , a delay of

0.5ms can be produced

D.Shiloah Elizabeth, DCSE/AU

85

D.Shiloah Elizabeth, DCSE/AU

Counters

Counters

Main program for counting from

AA to 00

MVI C, AAH

Loop: CALL Delay

DCR C

JNZ Loop

HLT

Hexadecimal counter to count from FFH to 00H

MVI B, 00H

NEXT: DCR B

MVI C, 05

DELAY:

DCR C

JNZ DELAY

MOV A, B

OUT PORT1

JMP NEXT

Delay subroutine for delay of 2ms

Delay: MVI D, 4AH

Next: NOP

NOP

NOP

NOP

DCR D

JNZ Next

RET

D.Shiloah Elizabeth, DCSE/AU

87

D.Shiloah Elizabeth, DCSE/AU

86

88

�8/5/2015

Counters

Delay Calculation

T D time delay in ms

Modulo-10 counter

START:

DISPLAY:

LOOP:

MOV A, B

T O time delay outside the loop

T l time delay inside the loop

LXI H, 16 BIT

Count

MVI B, 00H

OUT PORT1

DCX H

MOV A, L

ORA H

count

stored

in register

or register

pair

T D T O T L Count

JNZ LOOP

INR B

MOV A, B

T D T O T L Count

CPI 0AH

JNZ DISPLAY

JZ START

Count

D.Shiloah Elizabeth, DCSE/AU

89

TD TO

TL

D.Shiloah Elizabeth, DCSE/AU

90

Stack

The stack is an area of memory identified by the programmer for

temporary storage of information.

The stack is a Last In First Out (LIFO) structure.

The stack normally grows backwards into memory.

the programmer defines the bottom of the stack and the stack grows up into

reducing address range.

STACK & SUBROUTINEs

D.Shiloah Elizabeth, DCSE/AU

91

D.Shiloah Elizabeth, DCSE/AU

92

�8/5/2015

Stack

Stack

It is customary to place the bottom of the stack at the end of memory

to keep it as far away from user programs as possible.

In the 8085, the stack is defined by setting the SP (Stack Pointer)

register.

LXI SP, 6000H

This sets the Stack Pointer to location 6000H (end of memory for the 8085).

The Size of the stack is limited only by the available memory

Memory

Bottom of stack

D.Shiloah Elizabeth, DCSE/AU

93

D.Shiloah Elizabeth, DCSE/AU

Stack - Operations

Stack Operations - PUSH

Information is saved on the stack by PUSHing it on.

It is retrieved from the stack by POPing it off.

The 8085 provides two instructions:

PUSH B

(1 Byte Instruction)

12

34

Decrement SP

Copy the contents of register B to

the memory location pointed to by

SP

Decrement SP

Copy the contents of register C to

the memory location pointed to by

SP

PUSH and POP for storing information on the stack and retrieving it back.

Both PUSH and POP work with register pairs only.

D.Shiloah Elizabeth, DCSE/AU

95

D.Shiloah Elizabeth, DCSE/AU

94

5FFC

5FFD

5FFE

34

5FFF

12

6000

SP (after Push)

SP (initially)

96

�8/5/2015

Stack Operations - POP

POP D

(1 Byte Instruction)

Stack - Operations

12

34

Copy the contents of the memory

location pointed to by the SP to

register E

Increment SP

Copy the contents of the memory

location pointed to by the SP to

register D

Increment SP

D.Shiloah Elizabeth, DCSE/AU

During pushing, the stack operates in a decrement then store style.

The stack pointer is decremented first, then the information is placed on the

stack.

During poping, the stack operates in a use then increment style.

5FFC

5FFD

5FFE

34

5FFF

12

6000

SP (initially)

The information is retrieved from the top of the stack and then the pointer is

incremented.

The SP pointer always points to the top of the stack.

SP (after Pop)

97

D.Shiloah Elizabeth, DCSE/AU

98

Stack - Operations

Stack - Operations

The order of PUSHs and POPs must be opposite of each other in order

to retrieve information back into its original location.

The 8085 recognizes one additional register pair called the PSW

(Program Status Word).

PUSH B

PUSH D

...

POP D

POP B

This register pair is made up of the Accumulator and the Flags registers.

It is possible to push the PSW onto the stack, do whatever operations

are needed, then POP it off of the stack.

Reversing the order of the POP instructions will result in the exchange

of the contents of BC and DE.

D.Shiloah Elizabeth, DCSE/AU

99

The result is that the contents of the Accumulator and the status of the Flags

are returned to what they were before the operations were executed.

D.Shiloah Elizabeth, DCSE/AU

100

�8/5/2015

Stack - Operations

Stack - Operations

PUSH PSW (1 Byte Instruction)

POP PSW (1 Byte Instruction)

Decrement SP

Copy the contents of register A to the memory location pointed to by SP

Decrement SP

Copy the contents of Flag register to the memory location pointed to by SP

Copy the contents of the memory location pointed to by the SP to Flag

register

Increment SP

Copy the contents of the memory location pointed to by the SP to register A

Increment SP

D.Shiloah Elizabeth, DCSE/AU

101

Modify Flag Content using PUSH/POP

If we want to Reset the Zero Flag

7

6

5

8085 Flag :

S

Z

X

Program:

102

Subroutines

AC

CY

LXI SP 5FFF

PUSH PSW

POP H

MOV A,L

ANI BFH (BFH= 1011 1111) ;Masking

MOV L,A

PUSH H

POP PSW

D.Shiloah Elizabeth, DCSE/AU

D.Shiloah Elizabeth, DCSE/AU

A subroutine is a group of instructions that will be used repeatedly in

different locations of the program.

Rather than repeat the same instructions several times, they can be grouped

into a subroutine that is called from the different locations.

In Assembly language, a subroutine can exist anywhere in the code.

However, it is customary to place subroutines separately from the main

program.

103

D.Shiloah Elizabeth, DCSE/AU

104

�8/5/2015

Subroutines - Instructions

Subroutines Instructions - CALL

The 8085 has two instructions for dealing with subroutines.

CALL 4000H (3 byte instruction)

The CALL instruction is used to redirect program execution to the subroutine.

The RET instruction is used to return the execution to the calling routine.

D.Shiloah Elizabeth, DCSE/AU

105

D.Shiloah Elizabeth, DCSE/AU

Subroutines Instructions - CALL

Subroutines Instructions - RET

Microprocessor

RET (1 byte instruction)

106

Reads the subroutine address from the next two memory location and stores

the higher order 8bit of the address in the W register and stores the lower

order 8bit of the address in the Z register

Pushes the address of the instruction immediately following the CALL onto

the stack [Return address]

Loads the program counter with the 16-bit address supplied with the CALL

instruction from WZ register.

D.Shiloah Elizabeth, DCSE/AU

107

D.Shiloah Elizabeth, DCSE/AU

108

�8/5/2015

Subroutines Instructions - RET

Passing Data to a Subroutine

The CALL instruction places the return address at the two memory

locations immediately before where the Stack Pointer is pointing.

In Assembly Language data is passed to a subroutine through

registers.

You must set the SP correctly BEFORE using the CALL instruction.

The RET instruction takes the contents of the two memory locations

at the top of the stack and uses these as the return address.

The data is stored in one of the registers by the calling program and the

subroutine uses the value from the register.

Do not modify the stack pointer in a subroutine. You will lose the return

address.

The other possibility is to use agreed upon memory locations.

The calling program stores the data in the memory location and the

subroutine retrieves the data from the location and uses it.

D.Shiloah Elizabeth, DCSE/AU

109

D.Shiloah Elizabeth, DCSE/AU

Call by Reference and Call by Value

Cautions with PUSH and POP

If the subroutine performs operations on the contents of the

registers, then these modifications will be transferred back to the

calling program upon returning from a subroutine.

PUSH and POP should be used in opposite order.

There has to be as many POPs as there are PUSHs.

Call by reference

110

If not, the RET statement will pick up the wrong information from the top of

the stack and the program will fail.

It is not advisable to place PUSH or POP inside a loop.

If this is not desired, the subroutine should PUSH all the registers it

needs on the stack on entry and POP them on return.

The original values are restored before execution returns to the calling

program.

D.Shiloah Elizabeth, DCSE/AU

111

D.Shiloah Elizabeth, DCSE/AU

112