ASM Chart: Multiplier Control

COE608: Computer Organization

and Architecture

Dr. Gul N. Khan

http://www.ee.ryerson.ca/~gnkhan

Electrical and Computer Engineering

Ryerson University

Overview

Types of Sequential Circuits

Mealy and Moore Machine Models

Sequence Detector Implementations

Algorithmic State Machines: Introduction

Realization of ASM

Control Unit Design of the Multiplier

Hardwired Control

Sequence Register and Decoder Method

One Flip-Flop per State Method

Part of Chapter 8, section 8.3 - 8.5 of Text by Mano and Kime

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 1

�Sequential Logic Circuits

Primary input

variables

(x1 ..... xn )

Present state

variables

(y1 ..... yr)

Combinational

Logic

Output

variables

(z1 ..... zm)

}

}Nvext-state

ariables

Clock

(Y1 ..... Yr)

Memory

Devices

Inputs

Primary Inputs

State variables

Outputs

Output variables

Next state variables.

Synchronous Sequential Circuits

Clock is used to ensure occurrence of event (change

of state) at a specified instant of time.

Asynchronous Sequential Circuits

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 2

�Sequential Machine Models

Main Models of Sequential Circuits or

Machines are: Mealy and Moore Model

Mealy Machines: Their outputs depend on both

the present state and the present inputs.

Inputs

(x)

Comb.

Logic

Network

Outputs

(Z)

Next State

State Present

Reg. State

Clock

Moore Machines: The outputs depend on the

present state only.

Inputs

(x)

Comb.

Logic

Network

Outputs

(Z)

Next State

State Present

Reg. State

Clock

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 3

�Sequential Machine Models

Mealy Model

Moore Model

AB/S

AB

00/0

11/0

10/0

00/0

11/1

01/0

00

11

NS

Mealy State Table

Z/0

01

10

01/0

10/0

PS

AB

00

x x

y x

z x

01

00

11

Y/1

AB

00 01 11 10

x x/0 z/0 x/0 y/0

y x/0 y/0 x/1 y/0

z x/1 z/0 x/0 z/0

G.Khan

X/0

10

00/1

11/0

01/0

10/0

PS

00

11

01

10

NS

01

z

y

z

11

x

x

x

10

y

y

z

Output

S

0

1

0

Moore State Table

Computer Organization & Architecture-COE608: ASM and Control

Page: 4

�Sequential Machine Models

Mealy Model Timing Diagram

CLK

Present

State

Input A

Input B

Output S

Moore Model Timing Diagram

CLK

Present

State

Input A

Input B

Output S

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 5

�Sequential Machine Models

Main Features:

Moore machine realization is more complex

than Mealy due to additional state requirements

to derive the required outputs.

Outputs of a Moore machine are generally

robust and independent of external (primary)

inputs.

Mealy model is useful for applications where

faster respond is needed.

In the case of Mealy machines, all unspecified

states must end up in a specified state after the

next or consecutive clock cycle.

Otherwise, oscillation/hang-up may occur for

certain input combinations.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 6

�Finite State Machine Example

Problem Statement:

The occurrence of sequence of pairs of inputs

00001110 is to be detected.

The machine will output logic 1 after detecting

the sequence successfully.

The Mealy Model:

State transitions are labeled with inputs and the

output values.

10/1

11/0

01/0

1

10/0

01/0

11/0

01/0

10/0

00/0

01/0

10/0

11/0

00/0

00/0

00/0

3

11/0

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 7

�State Assignment

The occurrence of sequence of pairs of inputs

00001110 is to be detected.

Mealy Machine Design Approach

State-Transition Table

Present

Inputs X1, X2

state

Next state

Output z

00 01 11 10 00 01 11 10

2 1 1 1 0 0 0 0

1

3 1 1 1 0 0 0 0

2

3 1 4 1 0 0 0 0

3

2 1 1 1 0 0 0 1

4

State Assignment: Assign binary codes to the

states. 1 = 00, 2 = 01, 3 = 11 and 4 = 10

Present

State

y1y2

00

01

11

10

G.Khan

Inputs x1x2

Next State, w1w2

Output z

00 01 11 10 00 01 11 10

01 00 00 00 0 0 0 0

11 00 00 00 0 0 0 0

11 00 10 00 0 0 0 0

01 00 00 00 0 0 0 1

Computer Organization & Architecture-COE608: ASM and Control

Page: 8

�State Assignment

Any state assignment is satisfactory as long

as each state is assigned a unique binary

code.

However, one particular assignment may be

optimal that requires least number of gates.

Guidelines for State Assignment

States having the same NEXT STATES for a

given input condition should be given adjacent

assignments.

States, which are NEXT STATES of a singlestate, should be given adjacent assignments.

States, which have identical output specification,

should be given adjacent assignments.

Overall

Minimize the number of Sate Variable changes as

you move through the state diagram.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 9

�Mealy Machine Design

Using D-type FFs

x1x2

00

y1y2

01

11

x1x2

00

y1y2

10

00

01

11

10

00

01

11

10

w1 = x1 x 2 y 2 + x1x 2 y1y 2

x1x2

00

y1y2

01

01

11

10

w 2 = x1 x 2

11

10

00

01

11

10

BY INSPECTION OUTPUT z = x1 x2 y1 y2

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 10

�Mealy Machine Design

Sequential Circuit

x1

x2

x1

W2 Q

y2

W1 Q

y1

x2

Q

Clock

Timing Diagram

CLK

Present

State

Input x1

Input x2

Output z

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 11

�Moore Machine Implementation

The Moore Model:

Suitable for asynchronous sequential systems.

Transitions are labeled with the inputs only.

State Diagram

10

01

11

01,10,11

1/0

01

11

01

10

11

10

01

5/1

00

2/0

00

00

00

3/0

11

00

10

4/0

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 12

�Moore Machine Example

State-transition Table

Present State

1

2

3

4

5

Output

z

Next State

xy

00 01 11

2 1 1

3 1 1

3 1 4

2 1 1

2 1 1

10

1

1

1

5

1

0

0

0

0

1

State Assignment

Present State Next state (A+B+C+) Output

ABC

XY

z

00 01 11 10

000

001 000 000 000

0

001

011 000 000 000

0

011

011 000 010 000

0

010

001 000 000 110

0

110

001 000 000 000

1

Using D-type FFs

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 13

�Moore Machine Design

+

A=0

A=1

X

XY

00

BC

01

11

X

10

00

00

01

x

1

11

B

01

10

11

10

B = Cx y + BCxy + ABC xy

+

A=0

XY

00

BC

A=1

X

01

11

X

10

00

01

11

10

00

01

11

10

1

Y

x

C

C + = xy

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 14

�Moore Machine Design

Sequential Circuit

DA QA

QA

DB QB

QB

X

Y

DC QC

QC

clock

Timing Diagram

CLK

Present

State

ABC

1(000)

1(000)

2(001)

3(011)

4(010)

5(110)

1(000)

Input x

Input y

Output z

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 15

�Algorithmic State Machine

(ASM)

Flow Charts are mostly used for software

design. They are also useful for digital

system design.

The ASM or State Machine charts offer

several advantages over state diagrams.

Main Features of ASM Charts

Operation of a digital system represented by an

ASM chart is easier to understand.

An ASM chart can be converted into several

equivalent forms and each form leads directly

to a hardware realization.

The conditions for a proper state diagram are

completely satisfied by the ASM chart.

ASM chart based digital system design is

equivalent to software design.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 16

�ASM Charts

A Typical ASM Chart

S0/Za

S1/Zb

S2/Zc

Z1

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Z2

Page: 17

�ASM Charts

The state diagram/table based design approach

becomes impractical for systems with large

number of inputs.

The number of columns for the state table

doubles with every additional input.

All the inputs are not relevant at each clock

pulse/transition (don't care conditions).

On the other hand, ASM approach only shows

the active inputs on the chart.

State diagrams are not suitable for gradual

refinement of FSM.

Typical State Table

Present State Next state (A+B+C+) Output

ABC

XY

z

00 01 11 10

000

001 000 000 000

0

001

011 000 000 000

0

011

011 000 010 000

0

010

001 000 000 110

0

110

001 000 000 000

1

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 18

�ASM Charts

Basic Elements of an ASM chart are:

State Box

It represents one state of the ASM.

The sequential machine resides in a state box

for one state time (one clock cycle).

It consists of a state name, state assignment

code and state output (Moore).

State box has a single exit/entry point unlike to

a state node in state diagram.

Entry

Exit Path

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 19

�ASM Charts

Decision Box

The decision box takes machine inputs.

It contains Boolean variables to be tested and

gives conditions that control or qualify

conditional state transition and outputs.

Single entry path and two exit paths define the

condition for true or false exit.

input

Conditional Output Box

It describes those outputs that only become

active on true conditions.

It is always connected to the exit-path of a

decision box.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 20

�ASM Charts

ASM charts are equivalent to state diagrams:

Sate Box State diagram node

Decision Box Input values on the state

transition lines.

Outputs in the State Box Output values in the

state nodes. (Moore Machine)

Outputs in Conditional Output Box Output

values on the state transition lines. (Mealy

Machine)

ASM Block

ASM charts are constructed from ASM Blocks

An ASM block consists of:

Exactly one state box.

Decision and conditional output boxes

associated with the state.

One entry path and one or more exit paths.

A pure combinational circuit can be described by

one ASM block.

An ASM block describes the machine operation

during the time that the machine is in that state.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 21

�ASM Block

When a digital system enters the state associated

with an ASM block:

Outputs on the output list of the state box become true.

The conditions in the decision boxes are evaluated to

determine which path(s) are to be followed.

When a conditional output box is encountered along

such a path, the corresponding conditional outputs

become true.

If an output is not encountered along a path that output

is assigned a FALSE (by default).

Each exit path of an ASM block must lead to another

state.

Each possible path through an ASM block from

entrance to exit is termed as link path.

Entry path

S1

x1

x2

Z2

Z1

S2

G.Khan

many

exit

paths

S3

S4

Computer Organization & Architecture-COE608: ASM and Control

Page: 22

�ASM Block

An ASM Block can be drawn in several ways.

S1/Z1

X1

Z2

X2

S2

S3

S1/Z1

X2

1

1

X1

0

Z2

S2

G.Khan

X1

0

Z2

S3

Computer Organization & Architecture-COE608: ASM and Control

Page: 23

�ASM Block

Rules to Construct an ASM Block

For every valid combination of input variables, there

must be one exit path.

No internal feedback within an ASM block is allowed.

S0/

S0/

X1

X1

An ASM block can have several parallel paths that

lead to the same exit path and more than one of these

paths can be active at the same time.

S0/Z0

X1

0

Z1

G.Khan

X2

X3

0

Z2

Z3

Computer Organization & Architecture-COE608: ASM and Control

Page: 24

�ASM Chart

An ASM chart consists of one or more ASM

blocks connected in a consistent manner.

In the case of autonomous sequential circuits

ASM chart will consist of state boxes connected

by direct transition link paths.

The ASM chart of a JK Flip-Flop

Q

0

out 0

zero

1

1

out 1

one

0

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 25

�ASM Chart

From State Diagram to ASM Chart

X is an input

Za, Zb & Zc are Moore Outputs

Z1 & Z2 are Mealy Outputs

0/0

S0/Za

0/0

00

1/0

1/0

S1/Zb

S2/Zc

1/Z2

G.Khan

0/Z1

Computer Organization & Architecture-COE608: ASM and Control

Page: 26

�Realization of ASM Chart

Main Steps

For each state variable (e.g. Qa, Qb, etc.),

identify all states in which Q = 1

For each of these states, find all the linkpaths that lead into the state.

For each of these link paths, find a

product-term that is logic-1 when the

link-path is followed.

e.g. For a link path from state Si to Sj,

the product term will be 1 if the machine

is in state Si and the conditions for Sj

entry are satisfied.

The expression for Q+ is formed by

ORing all the product-terms found for a

particular state variable as above.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 27

�Realization from ASM Chart

Example

00

S0/Za

0

01

S1/Zb

11

S2/Zc

Z1

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Z2

Page: 28

�Realization from ASM Chart

Working Example

For Next State: Consider Variable B Link-paths for

States that has B = 1 are S1 and S2 states.

Link-Path-1

Starting with a present state AB = 00, takes the X=1

branch and terminates at state S1 during which B = 1.

Link-Path-2

Starting state 01, takes X=1 branch & ends at state 11.

Link-Path-3

Starting at state 11, takes X=1 branch and ends in

state 11.

Overall B+ = A'B'X + A'BX + ABX

For Next State: Consider State Variable A.

Two link paths terminate at S2 state

Moore Outputs

Za = A'B';

Zb = A'B;

Zc = AB

Conditional Output

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 29

�Binary Multipliers

Hand Multiplication:

11

* 13

143

1101

1011

1101

1101

0000

1101

10001111

Multiplicand

Multiplier

Modified (serial) Multiplication

11 0 0 0 0 0 1 0 1 1

* 13 1 1 0 1

011011011

001101101

1101

100111101

010011110

001001111

1101

100011111

010001111

Initial contents of product register

M bit=1, add multiplicand

Partial product before shift

Partial product after shift

Multiplier bit=1, add multiplicand

Partial product before shift

Partial product after shift

Multiplier bit=0 skip addition

Partial product after shift

Multiplier bit=1, add multiplicand

Partial product before shift

After shift (Final answer)

Final Result = 0 1 0 0 0 1 1 1 1

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 30

�Multiplier

Block Diagram

IN

n-1

Counter-P

log2n

G(Go)

Multiplicand

Register-B

n

Zero Detect

Cout

Control

Unit Q0

Parallel

Adder

n

Shift

Register-A

Multiplier

Shift

Register-Q

n

ACC: Product Out

Control signals

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 31

�Binary Multipliers

The multiplication of two binary numbers is performed

by successive additions and shifting.

B Multiplicand; Q Multiplier

Partial product is formed in A and stored in A & Q.

Multiplier Circuit Operation

Q is an n-bit shift register where multiplier is loaded

that is shifted right. It vacates 1-bit space every time.

This space accepts the lower part of the partial

product.

An n-bit parallel adder produces Sums as

AA+B

C flip-flop stores the carry from addition. It is reset to

zero during the right shift.

Counter P counts the number of add-shift or shift

actions. It is initially set at (n-1) & it counts down.

When P counts 0, the final product is in the double

register A and Q.

Control Unit is the heart of Multiplier:

Its input, G initiate multiplication.

Control unit generate control signals to perform addshift or shift operations.

It uses Q0 (LSB of Q shift register) and counter zerodetect, Z signals.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 32

�Multiplier Control, ASM

IDLE

C 0; A 0

P n-1

MUL0

Q0

AA+B

C Cout

MUL1

C 0, C || A || Q sr C || A || Q

P P-1

1 Multiplication Done

sr = shift right and

C || A || Q sr C || A || Q is equivalent to 4 transfers

A(n-1) C, A sr A, Q(n-1) A(0), Q sr Q

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 33

�Multiplier Control Unit

Control Unit is the Heart of Multiplier

Its input, G initiates multiplication.

It uses Q0 (LSB of Q shift register) and counter

zero-detect, Z signals.

Control unit generates control signals to activate

following micro-operations:

Sum of A and B.

PP transferred to A.

Cout transferred to C.

PP & multiplier in A:Q shifted right.

Carry from C is shifted to MSB of A:

LSB of Q is discarded.

After right shift, 1-bit of PP is transferred

into Q and multiplier bits are shifted one

bit right.

Control unit decides between add-shift and

shift depending on the LSB of Q.

Control unit checks Z for an end.

Control unit checks G, to start

multiplication.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 34

�Multiplier Control

ASM Chart Analysis

Multiplicand in register B

Multiplier in Q

State Changes from IDLE to MUL0

MUL0 State

MUL1 State

Decrement Counter P

Four transfers take place

A(n-1) C;

A sr A;

Q(n-1) A(0);

Q sr Q;

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 35

�Control Unit Design

Control unit design by using classical FSM

design is impractical due to large number of

inputs and states it may have.

An attempt to minimize and simplify these

circuits usually ends up in irregular networks

that would be difficult to recognize and debug.

An extension to the classical approach is used by

experienced designer in designing control logic

circuits:

Sequence register and decoder method.

One flip-flop per state method.

(One-hot state assignment method)

Microprogramming.

The first two methods result in a hard-wired logic.

Any modification will require rewiring.

The micro-program control uses ROM/PROM.

Modification of the PROM or replacing the

ROM modifies the micro-program control.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 36

�Hardwired Control

Type of Registers Used for Datapath

Register A is a shift register with parallel

load and synchronous clear.

Register Q is a shift register.

C flip-flop needs a synchronous clear.

Register B has a parallel load.

Register Q has a parallel load.

To Implement Control Unit Consider:

Control of micro-operations i.e. generate

the control signals

Sequencing of control unit and microoperation i.e. to determine what happens

next.

Control Unit Design Approach

Simplify ASM chart to represent only state

transitions.

Generate a new table to define control

signals in terms of states and inputs.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 37

�Control Signals for Multiplier

Micro-operations for each register

Block Diag Micro-Operation Control

Module

Signal

Register A A 0

Initialize

AA+B

Control

Expression

Load

CAQsr CAQ

Shift

Register B B IN

Load_B

C0

Clear_C

FF C

C Cout

Load

Register Q Q IN

Load_Q

CAQsr CAQ Shift

Counter P P n 1

Initialize

PP1

Decrement

Count

Same control signal for different registers:

Derive control signal logic from ASM

Initialize:

Clear_C:

Remove information on micro-operations and redraw

the ASM for sequencing purposes only.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 38

�ASM for Sequencing Part

Remove any decision boxes that do not affect the

next state situation.

Remove all the output boxes and any outputs in the

state boxes.

Design the sequencing part of the control unit

using the simplified ASM chart

IDLE

MUL0

MUL1

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 39

�Sequence Register and

Decoder Method

Sequence Register for control states

Register with n-Flip-Flops can have 2n states.

n-bit sequence register has n-FFs & associated gates.

Decoder provides outputs corresponding to each

state

Combination of the external inputs and feedback

from the present state generates the next states.

other control

T0

External

Input

conditions

Decision

Logic

Sequence

Register

Decoder

Present

State

Tn

If there is no external input then it reduces to a

counter decoder control circuit.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 40

�Sequence Register

and Decoder Method

Binary Multiplier Control Sequencer

3-states and 2-inputs:

State Table

Present State Inputs N. State

Name

M1

IDLE 0

0

MUL0 0

MUL1 1

1

1

M0

0

0

1

0

0

1

G

0

1

x

x

x

x

Z M1+ M0+ IDLE

1

x

1

x

0

x

0

0

0

1

x

x

Decoder

MUL0 MUL1

0

0

1

0

0

x

0

0

0

1

1

x

2 Flip-flops : M1 M0

States 00, 01 and 10: IDLE, MUL0 and MUL1

DM0 = M0+

DM1 = M1+

Outputs: Initialize, Clear_C, Shift and Load

Initialize and Shift already available

Gates required for Clear_C and Load

Clear_C =

Load =

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 41

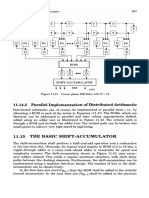

�Sequence Register

and Decoder Method

Implementation

Outputs to

Datapath

Inputs

Initialize

Go (G)

Clear_C

Z

Load

Q0

A0

2-to-4

Decoder

1

2

A1

Shift_dec

Clock

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 42

�Multiplier VHDL Code

-----

A behavioral model of a multiplier for

unsigned binary-numbers that multiplies a

4-bit multiplicand by a 4-bit multiplier

to give an 8-bit product.

-- The maximum number of clock cycles needed

-- for a multiply is 10.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity mult4X4 is

port ( Clk, St: in std_logic;

Mplier, Mcand:

in std_logic_vector(3 downto 0);

Done: out std_logic);

end mult4X4;

architecture behave1 of mult4X4 is

signal State: integer range 0 to 9;

-- accumulator

signal ACC: std_logic_vector(8 downto 0);

-- Q0 is bit 0 of ACC

alias Q0: std_logic is ACC(0);

begin

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 43

�process

begin

-- executes on rising edge of clock

wait until Clk = '1';

case State is

when 0 =>

--initial State

if St='1' then

ACC(8 downto 4)<= "00000"; --Begin cycle

-- Load multiplier

ACC(3 downto 0) <= Mplier;

State <= 1;

end if;

when 1 | 3 | 5 | 7 => --"add/shift" State

if Q0 = '1' then

--Add multiplicand

ACC(8 downto 4) <=

add4(ACC(7 downto 4),Mcand,'0');

State <= State + 1;

else

-- Shift accumulator right

ACC <= '0' & ACC(8 downto 1);

State <= State + 2;

end if;

when 2 | 4 | 6 | 8 =>

--"shift" State

-- Right shift

ACC <= '0' & ACC(8 downto 1);

State <= State + 1;

when 9 =>

-- End of cycle

State <= 0;

end case;

end process;

Done <= '1' when State = 9 else '0';

end behave1;

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 44

�One Flip-Flop per State Method

Every state is assigned to one flip-flop.

Other control outputs

State Box Entry

External

input

conditions

S0

State Box Exit

Decision

Logic

S1

S2

S3

Clock

The configuration of the 4-state control logic:

Four D-type flip-flops

One flip-flop for every state

Only one flip-flop will be active (level HIGH) at

any one time.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 45

�One Flip-Flop per State Method

Only one flip-flop is in active state or "1" at

a time that signifies one state.

Main Features:

The simplicity allows designers to design

controller only by inspection from the ASM

chart or state diagram.

Cost saving in the design effort of controllers,

however, it is not recommended for high

volume production.

Large number of flip-flops leads to high cost.

Each of the flip-flop output is connected to

the data-processing section of the digital

system, to initiate certain micro-operations.

If controllers do not have any input and the

control needs to be repeated then it becomes

a ring counter controller.

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 46

�One FF/State Implementation

Suited for Implementing Control Unit from ASM

charts.

ASM Transforming Rules

Entry

Entry

State Code

(optional)

State_Name/

outputs (Moore)

Entry X

Entry

Exit 1

Exit

State Box

Exit

0

Exit 0

Exit 0

Exit 1

Decision Box

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 47

�One FF/State Implementation

ASM Transforming Rules

Entry

Entry

X

Exit 1

Exit 1

Output

Conditional Output Box

Entry 1

Entry 2

Entry 1

Entry 2

Exit

Exit

Junction

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 48

�One FF/State Implementation

ASM Chart for Binary Multiplier Control

IDLE

Initialize

Clear_C

MUL0

Q0

AA+B

C Cout

MUL1

C 0, C || A || Q sr C || A || Q ; P P 1

(Complex Shift)

0

G.Khan

(LOAD)

1 Multiplication Done

Computer Organization & Architecture-COE608: ASM and Control

Page: 49

�One FF/State Implementation

D

C

Initialize

Clear_C

Load

Q0

Z

Shift_dec

C

Clock

G.Khan

Computer Organization & Architecture-COE608: ASM and Control

Page: 50