100% found this document useful (1 vote)

379 views29 pagesModule 3 Animated Single Cycle and Multi Cycle Data Path

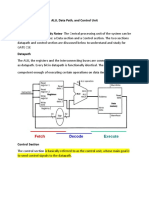

The document discusses single cycle and multi-cycle data path architectures. In a single cycle architecture, only one data word can be moved through the bus per clock cycle. A multi-cycle architecture uses three separate buses to allow transferring multiple words per cycle. It reduces the number of clock cycles needed for instruction execution by overlapping data transfers and operations across multiple cycles. The document provides examples of control sequences to add registers in single and multi-cycle data paths.

Uploaded by

Avv ReddyCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

100% found this document useful (1 vote)

379 views29 pagesModule 3 Animated Single Cycle and Multi Cycle Data Path

The document discusses single cycle and multi-cycle data path architectures. In a single cycle architecture, only one data word can be moved through the bus per clock cycle. A multi-cycle architecture uses three separate buses to allow transferring multiple words per cycle. It reduces the number of clock cycles needed for instruction execution by overlapping data transfers and operations across multiple cycles. The document provides examples of control sequences to add registers in single and multi-cycle data paths.

Uploaded by

Avv ReddyCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 29