0% found this document useful (0 votes)

333 views35 pagesModule 4

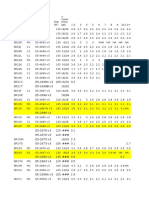

The document discusses the central processing unit (CPU) of a computer. It describes the CPU as having major components like registers, an arithmetic logic unit (ALU), and a control unit. The CPU uses different register organizations like general purpose registers and stack registers. It also discusses instruction formats, addressing modes, and data transfer operations that the CPU performs. The control unit directs information flow and selects components in the CPU to perform operations specified by instructions.

Uploaded by

ajajaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

333 views35 pagesModule 4

The document discusses the central processing unit (CPU) of a computer. It describes the CPU as having major components like registers, an arithmetic logic unit (ALU), and a control unit. The CPU uses different register organizations like general purpose registers and stack registers. It also discusses instruction formats, addressing modes, and data transfer operations that the CPU performs. The control unit directs information flow and selects components in the CPU to perform operations specified by instructions.

Uploaded by

ajajaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 35