0% found this document useful (0 votes)

375 views13 pages8085 Microprocessor

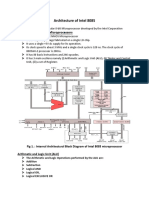

The 8085 microprocessor is an 8-bit general purpose microprocessor designed by Intel in 1974. It has three main sections: 1) an Arithmetic Logic Unit (ALU) that performs arithmetic and logical operations, 2) a Timing and Control Unit that generates timing and control signals, and 3) a set of registers including an accumulator, general purpose registers, program counter, and stack pointer. The microprocessor uses a single 5V power supply and has a clock speed of around 3MHz. It has 80 basic instructions and 246 opcodes.

Uploaded by

Deepak kumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

375 views13 pages8085 Microprocessor

The 8085 microprocessor is an 8-bit general purpose microprocessor designed by Intel in 1974. It has three main sections: 1) an Arithmetic Logic Unit (ALU) that performs arithmetic and logical operations, 2) a Timing and Control Unit that generates timing and control signals, and 3) a set of registers including an accumulator, general purpose registers, program counter, and stack pointer. The microprocessor uses a single 5V power supply and has a clock speed of around 3MHz. It has 80 basic instructions and 246 opcodes.

Uploaded by

Deepak kumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 13