0% found this document useful (0 votes)

17 views4 pagesAddressing Modes

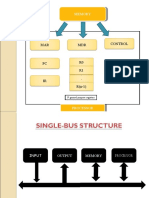

The document discusses the operation cycle and register set of a computer architecture, including the various registers used and their functions. It then covers the different types of instructions in terms of the number of operands and addressing modes, such as zero, one, two, and three address instructions. Finally, the document examines the addressing modes and addressing architecture, outlining how instructions specify the location of operands and results.

Uploaded by

Shalini PradhanCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

17 views4 pagesAddressing Modes

The document discusses the operation cycle and register set of a computer architecture, including the various registers used and their functions. It then covers the different types of instructions in terms of the number of operands and addressing modes, such as zero, one, two, and three address instructions. Finally, the document examines the addressing modes and addressing architecture, outlining how instructions specify the location of operands and results.

Uploaded by

Shalini PradhanCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 4