0% found this document useful (0 votes)

43 views20 pagesSequential Static

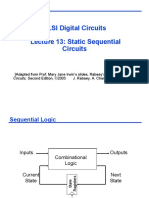

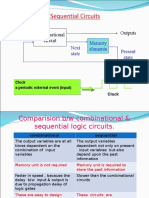

Static sequential circuits use feedback to store state information. They have inputs, outputs, combinational logic, a current state, and a next state. Timing metrics like setup time, hold time, and clock period must satisfy system timing constraints. Latches are level-sensitive while flip-flops are edge-triggered, using techniques like master-slave configuration to sample inputs. Bistable circuits like SR latches use regenerative feedback to have two stable states that can be toggled by control signals.

Uploaded by

vivek singhCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

43 views20 pagesSequential Static

Static sequential circuits use feedback to store state information. They have inputs, outputs, combinational logic, a current state, and a next state. Timing metrics like setup time, hold time, and clock period must satisfy system timing constraints. Latches are level-sensitive while flip-flops are edge-triggered, using techniques like master-slave configuration to sample inputs. Bistable circuits like SR latches use regenerative feedback to have two stable states that can be toggled by control signals.

Uploaded by

vivek singhCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 20