0 ratings0% found this document useful (0 votes)

102 views45 pagesVerilog Mod5

Verilog module 5. Notes

Uploaded by

jairajdattawad123Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

0 ratings0% found this document useful (0 votes)

102 views45 pagesVerilog Mod5

Verilog module 5. Notes

Uploaded by

jairajdattawad123Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF or read online on Scribd

You are on page 1/ 45

ISECSS

Vertlog Hoi

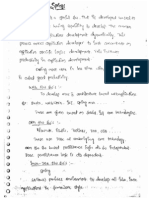

MODULE -5

Logic Syntuests Watn VeRTLOG HDL |

Logtc SYNTHESis

> Logic Aynthescs is the parca of onvedting a Sugh- level

diaswuption 4 the ddsign inte an optimized qr tet

Atpausuntodion, given a atourdard alt Acbaasy and catain

duscgn cornu krouats, ;

+ A skonrdord elt Aihsony con dove avmple ells , swe

Or bosse dogee ote dike and, % and nor oa mand

Us such wou wolders , muxe and specal fiep- Hops.

A rtandard oll Wray tt also known vas He 4 ectunclegy

Ue. : .

Designer's MIND AS THE Logic SYNTHESIS TooL

ad Logie ayrithescs velar. emuked een an the aye of

Arhervatic gote- level design, drut ch Woe valuvouys chong

ansde tre descynets mend,

> Tre deacgner anowld fiat undestand the wrchutectusal

duepiion » He wold Hun condor dustgn eorub cuit:

Auth var terug j Drea sukolrlity word pow.

7 Th husignen wuroutel pork tion the lesan ants Fuigh-fevel

bodes, olow Hem on sa poece of paper or cc computer

toaminal, oud voleccube the fun cdionatity of the react.

Thu anor the ugh - deve duscurphien .

> Finally , tach dhock smould de cmplemented on a drand-

lon schematic , aseng He «lls avor'labte va thy

Atondord wt LtAony

— 4

Nayara-K , Asst. Pael , ECE, ovat

—Vuuleg HDL ISECSE

—> The Lost step wos te mat comple pacceu an the dessgn

fled ond Arpured ueverol dime vonmunung alesse ekeration|

defor, an eptinczed gat Level Atprurentation that oat

wou dlustan wonitrains wos obtaradl «

FP Thus, He dutgnes mud waror used vox the togee synthucs

Fool, as citrated telow

ARCHITECTURAL

DescrirTEON

PARTIZTIONING INTO

HIGH —Lever Brocks

- --- #4 — = Sup DESIGN

rT ———+—_ | CONSTRAINTS

DESIqner's MIND '

1 STANDARD CELL

~ GATE- Le : LIeRARY

REPRESENTATION CrecHNoL ogy

DEPENDENT )

OPTIMSZED GATE-

LEVEL REPRESENTATION

ComPuTeR-AtpED Logic SYNTHESIs Process

+ The invention of veomputer ~ atoled Jogue dypthecs tools hay

voutomokud kha prow “af wonvuing the baigh- Level duwuption

40 aque que «

> Inskead + tagcag to Perform ogc synthecs in ther

minds > durcgnins Mar now wenantruts on the crcl tectua)

ande- offs > dugh - Level clusiytion of the luign » aecunats

Nayana-K, Asst» Pael, ECE) SvIT

z

Vestey HL I$ ECsB

-dussige enskaaints » ond veptirization of ett in thy atandary

wut Utbrany » Thue ore f4 fe the uomputer - cuided Logic

ayntnacs tek, auch pufernu several stesbory sntenally

wand grates Hu opliruzed gels devel du cuption .

+ Instead of drawing the drug daweh cluauncption on a.4Aten

ma pree of pape , saleavynens duwube He Sugh~ devel ealeaign

an kom +4 HDL&. Vea Hpls dhas Lecome vere of the populor

Hols sia aurching Jugh- dw vducurptions «

ARCHITECTURAL

DESCRIPTION

HEgH- LeveL

DESCRIPTION

ComPUTER- AIDED

Logic

DESIgn Consrraanns

SYNTHESIS

STANDARD Cetr

Lrerary

OPTIMIZED (TecHnotogy

GATE- LEVEL Netuser DEPENDENT )

PLAce AND Rove

+ The flow diagram valove Atpauents, computer -vaded Loge

Ayrthus prow.

—> Automated doguc synths dow atari peantly Atolued ting

for wenveuron pom Hugh duwe vduign auprtrentabion to

gett,

Neyana+K, Asst: Prof, ECE, SVIT

Vewhog HIDE MHECSE

Impact OF Logic SyntHests

> to gee ayntheaca dos Atvolutionrzed Lhe digital design endustry

by i grepcon tty dum prowng prcductivity vord by Atducing

volcan syle dur.

> Befos the ays v0} vonckomaked Hoge aynthercs | uchen destiny

wut worverted te gaia manually , te dusign prcuus had

He fotte wuing linitabion.

* Fox dang dlucgnr, manual wonvesion unas prone to

dumon oro. A amall gots ruiused eld mean Adeaign,

©{ enbine locks.

¥ Th dusvgner ould never be suse that ty dese, darutnaing|

wae gorag fe Le met until the gee Level. smplemuntaction

dar Kompleted and Lested»

x A Agri feat petion of be a eyo ar lominated

by te tow token to wonvet va Mug h- devel eargn cate

oe.

9

¥ Tf the gots devel dutgn wcik net met ALqputrements »

dhe bunorcund dime ‘al Audis c Atocks saa vey Aeon

¥ khet- 4f Arenower we dord do vey. For enample, thy

tlesianer Auigned A dock in gabe thot would run at

aya dine of 20a. I} te designer ananted to fra

wut auhither the wired would be optimized ste wun faate,

wk ISns , Ane entire block Sad to Le sedusrgned.

% Each ederigna utould simplonent sdusigin Mocks dittrently.

hee wos Md woruabuney a alusign abyles « For Large

sdlusvans the wold mean thet small tlocks suite optimized

dou che overall aluiyn sinos net eplimal .

Naxjana-k, Asst. Prof 7 ECE, SVIT 4

Vest eq HDI 7 ; pecs

* q a tug nb found dn bbe feral, grt devel des gn ,

shi, aucutd sometimes Auopu'ae the aedurgn of thousands

a) gee

¥ Teeag, arta vand pour ditstpation ah Unbaony walla

Oat frrwcadion ~ Aedrnology apectfre Thus +4 the “ornpany

chang eck tHe fc foerication vendor often the gods Lever

durgn wunes vompdete, thu susuld mean tho vadaagn of

He entinn vtrcaut rand ow porseble shang an, dustge

¥ Deg ALLE wuor not pesschlo. Descgns sure technology —

peutic , drard to port cand vey diffu to ruse.

| Automated Jogi ayrthucs trol vadoliuued Aue problems

* Hegh - Levey aad” uu dew prone to Juuman uroxr lecawe desig

Axe dasctbed ot o aghe devel of abe traction

* Huign— Awd sdtaign iu deny sw’ Hout ae gre prcant wont

wodrouk dissge wonadrarints » Logee Ayrtheis auth convert @

tuigh - devel aluvgn te 0. ot el matic and eur thet

wih weratnonts howe Leen mot. I} not, the darsgaer

bok , modifier the Jug Lave) dusign end Apeats the

PrAcay antl wo gue devel nekdiat that sodia bres touing ,

ann ond pow woutram'at u obtaraud.

% Lonvossons from Jugh- dvd duvgn to gata o fot» keleth

Hwa. umprovement lusgn aye times wars shorted

Aonad derby « hak towk months efns won new Le done in

frou a lays.

Nayona-k , Aest. Paol , ECE, SVIT

Vewles HDL IseCsE

¥* Tumnoround time je sudesign af locks a shouter Lecouse|

hanger AL ALopa'red vod wok the Augeake — transfer lava.

¥ Klhat - af SALONS OAL ty do veuty . the ugh devet

duccphior slo not hang» the ucignen dros monly to

| thong fom ona to Sar cand Auyrthescze the slevgn

to get the nw gets lew netlist that is optimized to

ahuwe a wage. time 4, isrs,

* dogee Ayr toescs toe oparmize the selenvign as a whos .

This Armoves He prchlem auth vaued lessen Abayles fe

He adifprenk docks in the sdesvgn sand «ubepdirral salesvgny

* Ya doug 44 found in tho gote-livel duran, the dean,

wos dak vad eheunges Hee ugh devel geen to eLiminaly

| Ha dug. Then, the duigh- devel vduscrcphion is vagain cack inte

| the ogee + pgp dol to automat cally gerade a new)

gate devel description

| * Logic aynthurs Aeools ollow A echnetogy - eadepenlerd

dungo « A dugh - Awd ducniption may be when su'thout

He IC fotucation technste gy in mend «

* Der reuse is ponsebte for technology sndspendent

leptons,

Nayana-K , Asst. Prof , ECE, SVIT

IeEC

Veatleg HDL ust

rc a

> Fo the Purpore 4 Aegie ayrthers, dus ign wont eusently

awHen in van HDL wt wm saguiter traneda Aevel (RTL),

> The kum RTL is used fr on HL dewuph'on styl

Anak wilhze a cembenabion 4 wat & flow vand

behavioral eonutaucts ,

— Logic synths tools take the Atgiake- tranfa- level HDL

desription and veonvat Lt to van sptirnized gate level nutli,

+ Behavioral ayunthucs tol that conve a Lehaw'cral

Wuwupiion inte aa RTL wlucuption ars slowly evotwng.

VeRtLoG Constructs

—— os reese

> Net wa conutruck van de duced hen suaing a

| dicuption few we Legis aynkhests toot, Any wonubuuc that is

used to dafene a age by-sayde RTL luuription is acceptable. A.

Heat of conatmuds thak wore accepted fy tegee synths tol on

Construct Tyee | Keyworo OR Descerprrom Nores

ports inpuk » output, snout

Paramekeu parameter

module defincton| module

[segnals £ vauably| wun, reg, tat Vectou vere vallowed

wnukontiabion medule snitances, Eg- ruax mi (ont, ¢0,c1,5);

Paouhive gots ceatanuy |Eg- rand (ent) a,b);

functions 4 Lasks function, task Timing werstruce (aored

Procdunel elunougs af) tun, de, Anibvol is net supperted

ae MaseX, AOKEL

Prouedurcd block, begun, endl, nroumed block, Pusalivng of named blocks

waaay wotlowed

dato {low OwLan ir on a

ee er

ile ver 1 t

“esp Preah, reve fonain Gt deci

Nayana-K, Aest. Prof, ECE, svIT ie

1B EC

Vetleg HDL

+ ince sue one proveding a wycle-by- mycle RIL vuwuption of the

MUnuk » thee wu autachen on the ay Aue won buck aye

ded fm the dogic ayrtieescs doh. For trample, He udwle wand

fern Loops mut be token ty @ Cposcalge lock) o

@© Cregg lack) stabenent 40 enfouo eydle-by- cycle behavist

wand bo parent wombiaational fctback.

> Lome ayrthascs grein vol towing delay apeerfeed by

tL > constrauct ,

The initial vonitauct di net dupporbed dy Lagi ynthuss

deels. the duscgner mut ue a Auek mechani bo

dni dtalize the auynolr tn the sexreut.

— ALL argral wutdthi and vesoby uudth be empliatly

Apeerfred » Defraing unszed vawabler con aumlt tn tasge ,

tes Level netlists Leco.ue ayrthess trol con tafe mrnesasy

Loge tasel van te yaualte definition.

| VERTLOG OPERATORS

> Almost wl ep rakes , emapt === andt== tot ay.

Aoked 6 x and B vom not alloureel for togee ay nthescy

+ Wilke suarting emprusvoray, st dt Arcommended fo

42 poranthuis te wepoup toxic Os AcQpulatd .

a4 due aly or eprraker precedence togee ayrthens tools

mulght prediuce en undeutrolle loge stauctun,

> The bik of Verttog HDL wperatou fu fog syntheses

4s shou:

Noyana-K Asst, Prel, ECE, SviT

Vertleg HDL ISECSe

OPERATOR TYPE | OPERATOR SYMBoL | OPERATION PERFORMED

pl

ARITHMETEC * raat ply

/ wh'vi'de

ta wold

- subtract

% modulus

+ unany plus

- Mnory minus

hogrcat ! wh negabion

A lage xg

I ‘ead 0

| eget on

B 5 thon

RELATIONAL Zi sa

>= greeter tran o equol

. Aus than a equal

Eavattry cqpolitey

srequolity

s 0 betuize jadn'on

Bir ntse & brtuuse anol

| brtuuse on

~ betuuse xox

an ww bctuvse xnox

REDUCTION & Atduckion anol

wd Atduction nena

| ALducb'on or

ma Auduction nor

a iF Arduchion xox

ned Atducion xnes

Suter >> Augit shaft

Ze daft shift

mae vearthoubic AUght shift

eee au tral deft sbi

CONCATEN ATION {4 eoncoben action

CONDITIONAL hs Conoli't onoy

Nayona-K, Assts Prof, ECE) SvIT 4

Veuloy Hou SECS

ENteERPRETATION OF A FEW VERILOG CoNnstRUCTs

> THe inka pactatien c vewlog tonstaucts wand thik

tronstotion to hoger goss 4s shown telow

i) ASSIqN STATEMENT

* The wuaign consknuck 4s the mort fundamental cenekrud

| Mused bo denem'be wombinabona dogee wt an RTL Level,

¥ Lensrder logue enpausvon thot te the asian statirnant

wausian out = Casbyic ,

* The satove emparuton is traniloted to He filtouuig gate -

devel Aupauuntation

a —

b out

ra

* Tf a, bre wrk out am 2-bit vectou Lio], then thy

walove vamcan stokenent wcll trans tote to two rdenticap

neu ia for each bet

Dest

ao}.

clo ——____J

blo}

of—_—__4

bo ——_} ovt [1]

cf}

Noyona: kK, Asst. Poh, ECE, SVET 10

Verilog HOL ISEcse ;

¥ qf wuthmetic eprrator wore used , each vauthmobic

vepuotr is amplurented in teu 4 vauthmetic droacduiary

blocks ovorlelle fo He dogte a yritheas dol A Ieee full

sadder is amplmented Lelow.

ustan fcouk, aun} = atbte tn;

¥ Acsuoung Hhok He I-brk full vadldlen ik wavertelte

an te topic seybhends trol, the above assign statement iy

sink upreted ty logic syrthess trols vos follows

: p> an

[a

an

* If @ vont onal epnator 2G wel , a multiplexer sccrerutt "4

anign ok = § 2 it: toy

* Me above enparsvon translotu ko pr devel epresentabion

% shown

De

r

Nayana-k, Asst: Pxol, ECE, SVIT

Veu'log Hol Ieecse

i) Df-€1se STATEMENT

¥ Aungle af cue akoterents trailor to mubiplerers sudwry

Ls ths dtgnat er vasabe én the of couse,

¥ The above statemmnt uull Aanstatr to tho got dove

Apruentation 0s shown delovs. (aux) » Mutlbple af deaf lo not

yo Jor MAN cee oat we be

” Da ie

Os

ti) CASE STATEMENT

* The ease statement can olio Le sued bo tube multiplere,,

xoue ls)

Too: uk =L0

* The aleve shaotirent uu'dl translotr to Hee gots - lover

Arpresentasion of multiplet shoun above,

Larger cose statements moyy te taed to snr Large

rrusliplexea-

+

Noyana-K » Asst- Prof , ECE, SVTT

Vewleg HDL ISECSR

iv) For Loops

* The $e doops tan he urecl to Anuld wascacled ambiratrona)

ogee » The fotlous'ng jm Loop Anatls von 8- bet Pull oolder.

C= tm;

(£20; 4¢=7; Lest)

fc, aumliTh = aft] + blide Cf I bweldy an @-bit pple adie

C Out = c)

V) ALWAYS STATEMENT

¥ The volurays stoterunt con Le ured de Lefer sequential and

ombenot'ona) Aagee « For sequonb ob Logic , the valeusoiys abatemudd

mut Le controlled +4 Hu chong, in the value of tock

At gnod lk.

aways @ Cporeclge lk)

ys

¥ The valve stoterent 4 brorutloted os & postive edge

tugged D- pup flop auth wh as int , oy 4 output ancl Lk

as the docking atgnoh

a t-¥

* The volove statement iu tronsleted to a bevel — denartive (ates,

¥

% Fer combrnational dogee the a

? wluuags ctatement -—-v

musk kacggeud gral othe cl, ntseh D-FF|

Noyana+K, Asst: Prel , ECE, SVIT cl

IP ECSS

Veslog HDL

vi) FUNCTION STATEMENT

* Fundions synthacze to wombinabona) Locks uth one output

Vowel. The output mgt de talon vector, A y-bet Put ay

on an the Veulog Beroupt on below, Thy

& implemented 00 a fonts

met acgnfant dat of the furchion i used for the asny bil,

function [20] futadd ,

anput — [3:0] a, bs

taput can;

begin

futtadd = atbhtan » yh pet fultadd fos casing , bets [3:0]

und W fsum

end function

==

SYNTHEsIs Design Flow

a ONES ee ES TON a

* The synthecs duvgn floo fram wan RTL deseription to

An veptimized gat twel decuption 1 os fottows.

RTL te Gates”

* Th 1c synthe flovo prom RTL t0 Gabe & cepted

din Kre flovochast :

Nawyana- K, Asst. Prol, ELE, svar

Vertleg HDL ie ered

RTL DEscRIPTION

f

' *

, | TRANSLATION ;

1

'

| [ UNoptEmizeD

' | CNTERMEDIATE '

| LREPRESENTATION '

; \

| [beate OrtimazAtioN| |

' | [ Leerary OF

DESIGN Lyf TECHNOLOGY MAPPING | | Avarcasue bares

Consrrasnis| | "LAND OPrimIzarso T [AND Lenr - Lever

L-~s= == — = CEUsCTetrmovogy

Li

OPTZMIZED GATE- St ARY,

LEVEL REPRESENTATION

Logue Syntheses Flor from RTL to Gate

_RTL_DescrzPTion

¥ the dearer wlisenibes Lhe \ oe wat we hgh devel ty aseng

RTL constructs. The designer spends kine in functional

veufuabon to muuy that the RTL oclucuptior fonctions

conuctty . Aftr the fonctionalrty “a voufred , the RTL dewupbin

ts unput to the Lagi ayotheacs tort.

TRANSLATION

% The RTL dercrrption 4 worwerted dy the Loge synths

Fool bo an uneptim reo in termediak , 1 bend teprerentaten

The prow U «atled “ tranitabion!

* The translate unrdeuterds the boc parmikives wand eperodoy

An he vencleg RTL desertion

* Dengan worukrornts such as Aen , teoung ard pour au not

tenucdered in bre dranstabion prea

* The Loge synths’ kook dows simpde ellecation of unterraf

Atsouws at tho poral.

Nowone- Kk, Asst. Pavk, ECE, SWOT 1S

Velo HDL IGECSR

UNoPTeMIZED Inrermensate REPRESENTATION

& the translot'on prow yds an unoptinuxed

Aprssentation of te dessign. The dun ia Aepsuserted|

intunolly 4 the dogec aynthess tol in teums of cabesnal

dato. structures,

hogte OPTIMIZATION

* Th doguc ts now optimized to remove redundautk Logie.

Vostous technology ~ drdepemolent rovlean Logie eptinization

Aechriquer ore used ard this procey yields an optimized

dnkeinol Acprttent ation 4 He design.

TEcrINOLOGy MAPPING AND OPTzmrzaTION

* Gn this step) he aynthess teol takes tu intenaf |

Atpatentation and ampliments the Aepauentahion we gotu,

maung Ehe culls provided Gr the Lechnolegy Lcbrany » te. the

design ix mapped fe tre dewnd target Lechnelogy, |

* The implementation «hawtd sokisy -Ausrgn weonstrounts such |

a bimang, area and power ,

TECHNOLOGy LLBRARY

¥ The Lechnctegy ray vento Livery walls prodded by

A tompany + Library alla can be base Logic gals omacte

wl, Ath 4 addery , ALLS , meade ple cers word A pectic ferplops

¥ The aly ere He bore ditding Mocks that a

wompany ull se fo Cc jebwration.

* Phycol dayout of library ll 6 done fort, Hen the

aan of ack “ell is computed from the veel

+ Nent, modeling Lechner ore uued £0 eatimat the tow

worl peur wharactem atu 4 ea debrany Mell « Tht proves

ws welled welt whoract exzation,

+ Noyang Kk, Agst, Past, Ele, Svar

16

Vieai og HD) IgeECsy

% Each eu ss whaewbed in ow founak that is unelustood

Ay the aynthess tool. The cll up ton wonkains 4% ‘oy

wobout the

iS Functionality of the colt

© Arco of tre cell tagout

. Torning tnformahion about tha cell

© Pour infoonatron volout the elf

+ A cotich’on Huse elle ts called tHe Lechnolo 7

The synthases 4A mses there uelts to snplonrt dr

DESIGn ConstRAINTS

# Deugn constraints dypicolly include Hu fotlounng

© Timing - The rot must meet certain tin Acqua

‘i An catenal atutic deur vonalyce, vais ing.

* Ara ~ The aa vf tre feaal Layout mut not enced a

dimet» .

© Power - The pow durcpaton cn te ura muut not

end a tHuuhold ,

* Thee 4 wan inverse Aclattonsbhip Leturen ean andl hinag

veonastroun, For a piven tecology Ubrory, to ephimice

dirung ( pute wine), Hoe dass Fos te le porallelrzed,

aaluich means wrcnurt hove to te dwt.

# To drtlh small erru'ts , alessignens mut Lompromerse on speed]

This caverse abotionshup 42 shou in figs

% btha than dun ontrount ,

apusking enveronmant jactou, such oy

dnput wand cutput delays , dave sbrangtiy ¢

wand Loads, mutt oflect he x

op hinuzalron {eo tha target technology,

Ts

* forca vs Timing"

Nayone-K, Asst. Pol) eee Sver

Vesrlog HDL ISECSR

Optimized GATE- LEVEL DESCRIPTION _

* Aner Lhe technology mopping ss comple , an eptins zed

ake-level netlist descubed an terry 4 target technology

Components an produced.

XT, tha netlist mete the rrqurred conatrourte, cb

Aranded bo the sompany for feral Layout. Otrouuse, the

alessgner meoolt'fres Ane RTL Or Acconstrarnts the Auiga 7

achieve the ducmd ruts, This proeu is stermted until

the netlist meets tho Arquured eonstrar chs . The company

wrt do the layed , Aemang checks Lo unsure thet the

eneuk masts Aapuitd Koung alter Layout end tun

fobasicodte He i6 dup.

1

Examece OF RTL ft Gares

a RAMPLE UF RIL jto GAres)

¥ Lender Hue dessige 4 yebal wa womparater .

Design Apeafication

* 4 meagre bude comparator checks +4 ee numba is

quota thon, equal to, o Leu than vancthes aumbe,

Deasgn Oo b-bwk magn buck omparoter IC whup trot

dros the follouning sprahiotions ;

* Inputs A ad B ay U-bet . No x! 2 values Appear

on A wand B an pula

© Qutpud A-gt-B vs tye af A ae poke. than B,

* Mukput AME B is tauo af A at Lew than B

* Outpnt — An caB as bane tf A cqyag eB,

x The msgrtteude comparnter cmt mut be os dat

5 pomcbls. Area con be compremvsed for ape.

Nayonak, Asst-Paof, ECE, evar

Verwleg HDL ISEcsB

eta RTL altnaiption Aha incacbe the mayactch

tompornter 4 shoun telow. Thu us & Lechnology -

dndapendent dlscruphon, the sales tignen des not have to

suouy alout the target technology at this porrt,

module bade comparator ( A-gi-B ALL -B , Atg-B, A,B),

siAput mo By , ~ “

butput Agt-B, A-wB, A-eq-B

Onsen A-gt & = CA>B), 4A greet than &

aug AM B= (ALE) A Lew tan 5

wousrgn — A_tg-B = Vey WA eaprol to B

endumedute

Feeknolegy Liban |

* Amur tHrat wie decide to we the 065 Murer CMOS prow

tolled abe-too used dg ABC Inc, bo make our «bup.

4 ABC Inc, supnlts a technology bkrery for synthe .

The Litkory contain tre follouurg Ib ely luis any

dpned in a format unoluutrod by the synthens toot.

d] kibrony eetls fo, abcloo bechinology

VNAND || 2- tapnt NAND get

VAND Il 2-4nput AND gee

VNOR Il 2-4nput Nok ge

VOR 2 -anput OR gue

Vor il not gate

WBF I Auafter

NoFF Il ve edge tivggerced D-flep flop

PDFF Il He tog tugged D- fup flop

Nagane-k, Asst. Pref, ECE, Svir 4

Vuwleg HDL IS ECR

Desgnr contrat

¥ According fo the apeccfreabien , te design shoutol be ay

fut as porscbde fe the target technology 1, &bC-100, There aro

no wire conetrainh, Thus , oplinwze the feral eet for

fostut binung.

Hogex synthases

© Te RTL deseuption of the macgeetucle omparator iy 400s)

dy te fogic syrthen's toot . The dugn constrounts and

kechnelogy Library for abe-ico ware provideot to the Logee

syrthecs toot, The Logee aynthercs tool perfor the neces ary

aeptimrzabon and produces 0 gee burt descupbien -optimazed

for abe loo technology

Fino , Opdirnized , Gate level desuptron _

¥ The Logue aynthescs tovt produces a final , got level

Asscxsptior

+ & the olan er, deudes to sue ancthn technelogy,

ay my Z-1o0 pom XYZ Ing He RTL dewurpkion and

dessin wonstrounts do not vonge ; BUT te Ledurelegy

Adnaay ahvenrges

EC fodaacadion

4 The gate devel nekitsk is verrfred for puadtocalety

sound timing wnd thet submited to ABC. Tne.

* the ABC Enc, dow te lup Aoyout , checks Lhat tre

pock— oor out: wink mute demng Atgpacaserentts »

ond Haun porburcates the 2¢ chip, maing abe- lov technolory

Nayara-k, Asst Prof, ECE, svar oe

Vextlog HPL Wee

eVEREFoCATION OF THe Gate- Lever Nerirsrs

x The epkimczed gods devet netlist prccluced dy the loge

ayers bod mut be veupred B fonchien cbcty.

¥ The aynthars trl may nt eluuays be able to mack

both kung anol ama recqurrements 4 Hay sare too

stutagent. Th, a teporak Heung vowfreation can be

done on tne gute devel nethast.

() FUNCTIONAL ‘VERTFICA TION

* Tdenticot skim i aun wcth de sregeaal RTL and

Ayntheacxed te - evel les crc'pivons 4 the wluscgn. The

Butpt is comparud to fone stavg miimatihes » The stimulay

for a magnitude comparator ts shown

Module shire 5

eri} [3:0] a, 8;

Masha Apt-B, AAL-B , A-eq-B y

HW swrskowtioate the mognad comp orator

Mapmckardt- comparator mt (A-gLB, A-dB, Apter By A,®);

Ani bod

gmoniter (ghime, “Az eb, B= Ab, Ag Bab, ALB = tb

A-ey-B> Lb", A,B, Agree, AALB, Ata-6),

snr kiod

ac Aiblo1o i B= 4'bIoDI;

#10 Az A’bIllo 5 Bz A bility

#10 A= h'bD000 B= 4'b0000 ;

H#IO A= 4'b1000 » B= h'bI100

#10 A = 4'b ONO » B= h'biioy

#0 A= A'billo ; B= h'bIN0 ;

end

enrdliie dite

Nayana-K, Asst. Prof, ECE, SVZT 2t

Vou'leg HDL SECs

x ThE same adtirmtus 14 appled to roth the RTL desupton

una aynthaczed ode - devel lescuption. end tu simulation

veukput 44 corp ored i musmotches .

¥ The agian devel Aecuption is sin Leuns 4 Llcany “ells VAND ,

VNAND e&c. Vea armubetery do not undestand the

meouning 4 there «ells,

¥ Thus , te acudate kha gol tevel ducuption a svmutation

AdLaony » @dbe_lO0-V muuk Le promdee] ty the ABL Inc,

* The stmuletion Ab. musk olerou'be «ells VAND, VNAND

tk un bem of Veuiteg HOL primchves andl, Nand etc.

¥ Comu'der the enampte telow, Ars VAND elt olefined ot

the dimulahonr Library

maduse VAND ( aut, ino, int);

dnp ain 0;

Faprk wnat},

veudpnk gut »

NH kiening anfomasion 7 ause [fall ond oun: typsmax

Apu ”

Cuno =rouk ) = (0.260604, 0513000; 0.455206, O+ 25524 5 0+SD 3000-434

enrdupecify

W tet erate a Veutoy HDL pacmetve.

word (out, 0, vas) 5

enolraculo

WAU Lb, wes sacl trowe sousponding rrewdaale olefin,

MN an kes of veulog Prtols vey

(sind => out) = (01260604 101 513060; 0.955206, 025524 + O-SDB.0ED:0-9345H)|;

Nayana-k, Asst. Paol, ECE, svIT 2

Veuwlog HDL 18ECSR

% Adirules is oppliecl to the RTL dlucuption ond the

qk devel dercrarptron , A Ay pscok anveralion puth a

oe armuledsr 46 shoun below

WW Apply Atinudus te RTL ducuption

7 Vewlog sbinwlas¥ mag compar.¥

HW Apply sbcrrulus te gate - Level vdleruuption

" Tnclude the strlen Arbrany “abe-Iov.v" watag -¥ option

> varlog shins Vv mag— compar. 9V =-V abe-lo0.V

¥ The stmutetion eutpd mut Le colentical fr the two

Atmutebrons. The eutput from Atmilation of magnitude

Aemparster shown

0 A=1010, B=1001, A-gtLB=1, A_MB=0, Atq-B=0

JO AS WIO, Be tit , Age B=0,ALLB= 1 , Areg a=

20 A= 0000, B= p00, A-gt-B=0, A-Lt-B=0, A-eg-B2)

30 A= 1000, &= 100, A-gt-8= 0, A-B=), A-eq-8=0

HO A= 010, B= IO, A-gt-B=0, A-MB=1, A-eq-B=0

SD A=I110, B= N10, Agi B=0, AdtB=0, Aeqg-B=)

X Tf the output 4 not Adentival , He doses needs to check

fr any tugs ond recur the hole flow until all bugs ary

Ukmunaled.

iJTIMING VERIFICATION

* The gate devel atlist as by prcally checked fn Hung by we

of timing acovulation or by a ababre timing veufres,

4 Tf any Meung cons trords ors wolatedl, the olerigner muse

when sedeuvgn part of Hho RTL A make Aodo-offs sin dasa

wantraint for Loge ayrthecs, The entire flow a cteratedt

aunts kinuny Aropurerent wore met.

L

Nasana-K, Asst. Pol, ECE, Svar ae

8

Veulog HOL IBECS

MopuLe &

[[Userue MODELING, TECHNIQUES

PRocepurat CONTINUOUS AsstgNMENTS

+ Procedural auargamerds ausugn. wo Value to pageater

The volue atags an the aquster until onotha procedurol

lac gurnent pyre vancthe value un that Aegeaten,

+ Prewcual cominmovu ourgnmerds behave -clefferently,

They eae prccednad statemants uruich allow values of

emparavony to Le -cuven eantinnoualy onte Atgeaters Ane

fer Aroncteal pewodls of Lime,

> Procedural ronbinuous ei grunants ovemicle enusting

vesignmuda te vo Angeabn a ned,

(ASSIGN Bnd DEASSIGN

> The Ray wordy * vosaugn " ond “clean wrx sued to

emprey the 14k type 4 Procedure) eantinuow es gnmend,

FOThe heft ond cdr of prccdital wontinaous cave

van Le vonly a Aquat’ A a woncetenation vl

Te cannot Le eo past ot Unt select of vce

conn oh Maisto,

— Procedure wordinwow, ust gamers evade Ly

Mmagulor procedural wungaments

> Lovurder the enomphe of negadive

ak vasyachronous suck modeled

‘oleauavgn' wv tatements

greets

Angaben,

St an

ae 4

ege- Cxcegenad D- pip flop

auscng “usugn’ fared

NayenaK, Fest. Pro}, ECE, eviT 4

—Vertloy Hoe

r

(secs

4 Negative thge dacggend. D-FF uth sryachtonou rset

module D-FF (4, ybor, a, «Lk, Atseck.)s

output oy, aybar ;

dngput dh, atk, ruck ;

AQ yj eybOr ;

aluvoys Camect) Il ovede the aeguters sgnounk te g and

e ; Tqbor suhenever acact pe huge *

+f (auc)

begin “a “f Aue wa degn, ovande Argulor vous game

N bo y wrt new values

wuavgn y= Ibo;

BsLGn abar= I'bl;

de

begun Wea} Auek us Low ,rrmove He everrding valuy

Y by Aeauscgning he Aguado 1 After the ty

Wrnguton aston g= ol rand aber sad wu

Nhe atte Lo vchange the Agate on -ve felou)

deauugn x; “Y F

cetascgn, aber »

end

endino cule

x In ky above enamphl, we. overrode ths ourgnrnent on q and

gybar and vagned new valu to them wilun Le reel stgnop

Ausnt Ligh, The eke vawables Achaia the continuous

eutpned volus waft ty deaucgn auntie Hey ore changed cigar .

Nagoa-K, Asst. Poh, ECE, svar 2

IBECR

Vewlog HDL

ti) FOR

Thu Rayon “force” and VArlease” ory aed to onprru thy

decond fon 4 the proudurot centinuous vost marcha

> They con te sued Lo overuide auargemardls on beth Argisteu

and nets,

pwn” and “aeleare” stotenerc om wed oe the satuacie

Auuggirg prow, shin vantain aegeakes a nets vane forced

Ae a value anf the effect on other aegiites ond nou is

noted

fre” and Teleae” statements should voppear only én sbmiday

Mocs rotor tan descgn Mock »

a) ond release on ‘atery

and RELEASE _

*A foe won Oe regener over’ dley soon Proceditsal osignmedy

Hm prccedural wontinuous oaatgrun

the sgester uu rvleased.

* the Masta vawebler uu vonbinne fo sto Hy foced valu

often Jeng Atlosed , but «can Hen be changed diy a futicrs

Procedural Puatgamand ,

x Eni~ To oveurde the valuu of Yy and qbou fea Lnsbed persed g tm

module Abinuatus 5

ents on te Auguater aunt}

HW sinakawtiods the d- {Up flop

DFF Af(q, vba, d, alk » Aesek)

SD foe dif = I'bl; Il four value of 4 to4 at ru sd

# SD slsase aff g ; N aeteare the value of 4 at time ioo

end

jg These abotements fru value of ton afley behwean toe BIg Set |

Nayana-K, Asst Prof, ECE, SvIT 3

Verrloy HOL 1B ECSt

r

b) fom ard Acleare on rata

* four’ on ne evernders wong torlinuous ata gamers wtih

Ae net ib rlomedl. The net sul smmadtatey sebuan 40 +t

reumel duven value when vt u released,

* A net eon be forced to 2m enprucon oa value

Ex:-

medule bop;

vuatgn eut= aL bLC; I enkinuous axa tgament on nal

din bios

#50 fore out = al bec;

H50 pghease out ;

4 Tn the alo enomple , O new enpruuvon is pod on the

net fem dime 50 to deme 100.

¥ From Lime 50 to hime 160, shun the fore” shaterunt is aki,

He emprucon a)bbe uit Le Ae-wolwoted seal vasa rgrad

Ho cut wtunever volun of aguas & ab oc henge .

4 Thus He foe stobenant dehrover Uke a continuous aur

Cneeph Hrak ck i active for only a dimrked powed of te,

a

Nayana-k, Asst. Paef, ECE, Svat 4

Vuu'og HDL Iwecse

* OVERRIDING TARAMETERS *

> Poramees coun be defined un a module defcartion .

However , using wom pilabion 4 volog modules » parametey,

volues won Le altered separately fo each module

Tuten. This allows rai to pam wa distinct ek of podamday

values Lo each module dung sompaihedion Aagerdlens +

Pardened porometr values.

+> Thee ware two abt ts ovewck parameter voles

O def parom 4 tetement

WD modiute trutance porameta value wevaugunint.

© ALi aroun akotument

¥ Prrmmeter valus won be chongeal en ony rrvodiule

tnskonee in dhe design wut ka dhe keyword def param’.

* The AWearclu'cal noone of Hr madule snstane van be sued

to ovenide pmameban voluss:

En: Bf puam skatement to oversde the porarmeter veluos

ywrodute retlowortd »

P Areumnebe Adnum = 0;

dni kero,

dovuplay (" Displaying Ileweld sd number = %d", 4d_num);

tndmedulo

redule top It dip bop “eh module

deh param whetdnum =4, w2-td-num =2 3 fl parameter,

Uvotue in srotawctiatcd module.

Mairakordiode wo Atle cold moclute

Mutlo-mertd wil) s

Ao-wed wr); |

enrdmoduvle |

Nayana+K, Asst. Prot, ECE, SvEr s

Vert log HDL IS Ec

¥ en emample , the modu Alle world wos defined muth

a difaule idnum = 0» Howwer, uduen the module cnstanes

Wt sand wd of He type bullosield oe crated , tect drum

Vols ore modified auth the defparom abatement

¥ TR wr simulate, the fotiouning outpuk L obtained

Datsplaytng Allowed 1d numba <4

Displaying Awlte weld sd number = 2

CD Module —Tnetance Parameter Value

* Porometr vals can Le evendder wdun «a module u

dnskontated: Lovusder tre trample telew

Fmedute — halle would +

poromeber sdnums 0 + I dapine a module td number

dni hich

$desploy G Displaying AbWlowald 4d number = of A" sd-aum);

endlmodube

module tops

W anskuntioke 9 hello wold modules; poss new parameter yalus

I Parameter value ua tgnersit by ordered List

Atlo-wold #(1) wi 3 I pas value t to module 1

I Poxomutr value sarstquemendt by name

Alo-weld # (.td-num(2)) w2 5 I pau volue 2 to sd

HW parameter fr module w2

endimodluto

* The new porometer volusr are pauedl during maclule trsborcticcin,

% The top-lwu module wan pow poramutey to te smkances wd ond

WL. The sioutortion output uit be volentical os defpasam statement.

Nayarak, Aest. Pref , ECE, svar 6

Verlog HDL ISECR

* Alkanetively, wie con everide apeefee voles ty ranung

the poromutes and the eousapondling value, This 4 walled

parameter value weustgnenent ty nome,

Eu- Module wutone porometer Values

P rwaclite — burmeutea 5

Perounster Ablays =)

Parameter delay?

Parameter dilays =

< module inten >

endunoduo,

Module kop) iY top-level module ; ingband' ater 2 bus-master module,

W Traterdioke te modules unth new delay values

H Porometr value aus gament ty ordered ist

busmauta #(4,5, 6) bt av Mb4 delay i=4, delay2= 5, delays =6

busmata #(4, 4) b20) | Mb2: olay! =9, delay 2= y , delay 329 cedutt)

| Porxameter value espn 4y non

burmeuta # Coleen 26h) jelelays(1)) bs O)s

7

Mb3; delay? =} ) delay3=7, Aelay! = 2C default)

4

4 © Porcumeter value vonez

WM and Perameters an Le

moerying ehrouk Hire ordey_

% Madude- ins taney Porameter value uagnmnedt a ven sudul

method sueol to override prerameter values vord to ustomeze

Module tins tances

ty nome muaimizes the Hance of

wedded or deleted cutout

Nayana+K, Asst» Pref » ECE, Svir 7

IBECSo

Vow Log HDL

¥ CONDITIONAL COMPILATION and ExECuUTEOy ¥

Fd portion sof vearleg code rmught Je sultalts for ene

envionment drut net for anothu. The desrger does nok

ssh ke cnet hoo veurons of ‘Veutog dusyn fo ty bvo

enycronments +

+ Cutead, Hu Aesaigrer won 4 pecity that Lhe Port ulor portion

of te xade Le compiled wonky af e sertain flog 4 act. thes

4s “allel Yeond't ona) sompilation ””

7d des gnes On emecerte wuntain ports the Verwleg dasan

tig when oe ea ts set at Aun kre, This 4 called

tondut onal ertenuhion ”

') Convertonnr _Compscarton

® Lond donel xomprlodion con Le accomplished ty

waving

Mempader di rrchives

> *apaes

7 falas

> ‘he

> Saad .

=a) “wdit

* Examples :- Voulog source wodr to Le compiled Conditvonatly.

Example t- Londcvonad wom palace on

*afdef Test I] vompele module tet only cf tent mano tesr,

module Lek ; tee

endmedult

‘ce " wompele the module ctimulus as Ce

mode adi ulus

J

Sunde UL ompletion of ‘Ufdel direct’ ve 3

Noyana-k, Asst. Prof, ECE, svaIT

Example 23- Conditional ccompelation _

A kample 2 in eas

Module top +

bus_master bi)

‘fda App-82

bwa_ mate b20))

MW dnetuntolt medue wantondi b onally

1b2 is inskantioted conglition

M kemt moro Add-82 u anes i

‘aug App-83

dus- morte b3C)) Wb ib sutentiobed conditic “f

Went maup Add-63 wu defined

| ‘ cue

bws_meoster bHO) W bh it cnadanticctoot by da fate

“endef

‘5 TQ NoOKEBS

zfrdd 16

; bw mate bSU), I bS & Sutantiated conditionally Wa

a Il ent mans IGnort_es & not defined

* endef

endmodue

x The ‘efde} aud ‘af dixeetives wean appear vonywherr in the

duran. A dessa von aovelenally compile statements ,

moduly, Iorks , declaration «url other eompaler dire chives,

* The ‘ele dincbve 0 phonal» A manimun one ‘ele

“afided a ‘ef ade . Arg numbey

any an ‘ef dol o ‘apres

+ Bn ‘af dad vor fade} ts weluvays clered by a corresponding

“endif «

* Te wonditonal wom pals {4 won be set ty wacag the ‘depiw

atokemurt dnuide the Vewlog fru:

dinschie van accompany an

ct "dist dirrcbiver con vaccom p

4

. Nayana+K, Asst. Pool , ECE ,svir

V wiley HDL SECS

CONDITIONAL EXECUTION

> Londikonal encackion flags allow tru decsigner to contact

akakument encoton flew at aun Line ,

> AU stotuvenk wy stomp vhed tude enecuted vandibonably ,

+ Londitiona enraction fags van be ~ued wonky je behaved

Akotomuts

— Th aysten task Flat $plasargs 4s ued fi Londltionap

ereurt on.

Example i- Lenditfonal enetion sith Phat $ piusargs

mMedule duty,

Anttiol

“f ¢ Fert $pluuargs C" prsptay_var"))

Facaplay C"Desplay = tb", La, b, ch); Mdvaplgmy ffeays,

ee

© dedsaploy C*Nlo Display"), II No veplay; conditional enecidien

end

endimeduls

AM Voriobls ors dusplayed only 4 the fieg DISPLAY_VAR is

4 ob mun bie. FI won be «et at aun Kore ty spect byiag

tht ophion + DIsPiay-vAR at aun tino,

+> Combittened enrurtion can be har contacted by watng thy

spite bask kegiord fivalue fplusargs . This system task allows

dating fx arguments fo an trvocabon option ,

> F value $ plunorgs sku a 0 ‘f a matdng Bwecabin way

not found end non- ze 4 a makdung option wad found

Nayana +k, AsstsPeol, ECE, ovr 1D

Vitleg HOL IsEcR

Example :- Kenditiors Exeuten uth Fralus fplusargs

Tmeduk dats

Mg [84 128-1: 0] ut chung 5

arteger lk pewed ;

init of

6

4 C$ valu $ plusargs C"dabreme = % 5") bat sbung))

$rradmamh (dud string, vetou)s Mrrad tat vectou

ee

Sdesplay ("Tut nore option not spectfred ");

Hf ( Pvatus $plusargs (Mlk b= ord", te_peued ))

frown #0 Ak paved /2) atk = wale 5 I cet up clock

eke

Sdasplay (“clock peed option nar ast peated"); ee

tnd “ey

endnote

¥ Fee oample | to invoke ty walove options snvoke atmelate,

auth +hutname = tutl.vec +ele_t =10

NW Tuk.aems = “tubivec” and velk—pusod = 10

|

|

Nayana «kK, Asst

ECE, SvEr

(BEC SB

Verte HDL

* TImE SCALES *

>t w us atmulation , delay voluer in one module need

fo de depirtd by wacng a tain time wt eg. as

sand dilag valu in sancth medule ned do te defined

by warag wm different dime unit , SG 108. Vewteg Hor

allows the sefeunee Lime unce fe Modules to Le speacfed

wath Kho “timescale compiler derschive ; -

USAGE ?— ' timescale (referee bine wb [chine prea ations |

* TNA nabence_ timers > Apesfies the urck of mensusenent

for timer ond Aalaays

+ The < time — preuson> Apa fres the prwsion 40 Lukin the

letays ae rounded bf duniing simulet'on .

S Aely 1 10 cand 100 ase valid int sptatnng Aime

duntk wend me pMascvon. io i irs

Examplet- Defene a bow scale fou Ha module ducal. « the

Adfrence tome wk is 100 nanoseconds ond prrcscon is lag

* bimsscolle 100n8/ Ins

Meoclule dummyt 5

“gq tage 5

ini biod

toggle = I'b0»

lantiys HS WEA the dogg’ equate wey © hime wuts

begin US hime wut = SSO = Ops

baggas apie; .

Pdisplay (" %d , In ther toggle = Yb", $time , ogg’);

und

encnedule.

Nayana:K, Asst Pre y Eck, cvir

Vexlog HDL _ IS ECs

Example 2 :- D ofvas Ow hime “acale fou module dummy 2

Rekune Mow wut 4 ius wand pacusvon iu lOns.

\ ponescole lye] 10mg

needle dumeng? »

Ag eagle 5

witha

Hoge = I'bO }

Ohms #5

ies

ogi

deggh = © Pag,

$dvplay("%d , Br Zon stoggls = hb", dtime , toggle),

end

endmeduls |

“+ In He aloe Avo odes, Hu hig sank fox dium 4 led)

wand the be snk ae dummy? db [pes Thiss the Alesplay

Akokement in duran d wut Le eneeutel 10 bres for cach

Sdesplay emecsted sin dummy2, The fkime task reports

He simuletion time in tems 4 tre Aefusivee dime wuts

SiImvtation Ovrput

# The fut fe Faclvsplag skaterent ow shown

ce i scluramy t boggte =!

10, m& harem toggle =

16, Gr daumunyi toggle = |

20, & during t fag = °

25, Tn dummyt koggle= 1

30, Tn dummy! koggle= 0

3S, Tn sclummyt — Loggur= |

40, Tr churn boggts= oO

4S, In durvumy 4 boggl= I

5) In run 2. boggle HT e duunmy? eneeuter once entry

5 i 1 bogge= 0 10 Mebioweals Ait clesmmy 1

SS) Tr dummy —_boggee- | Z J

B

d

Nayana- ky Asst. Pool, ECE, SVIT

Vlog HDL IB ECsh

] * USEFUL SYSTEM TASKS #

Fle output + Dvsplageng Hreran *Sb.0bvag + Random Number .

@ FILLE OCvurput * Gebiobixtng memory from file Value cha eS dump ht

> Wakput fom Vewlog nounally gas te the 4tandard

tulpuk cand tre frle vewlog. log. Lt & poscbla bo redirect

the output sf Veu'log Ae a chon pele.

a) OPENING A FILE

LENG SEE :

¥ 4 fe wan be opened, sucky the system task dfepen

USAGE 3 £ fopen (aD rame-of - pe My

USAGE : frlehandle a $thopen C" mamneof fel as

* The Louk $fopen Arbus ol 32-bLt value tolled a multichona|

les.criptor- Onby Lbrkt & sek tn a muolbichannd her cseptsr ,

# The standard eutput thos 0 multichennd decupter

wath the teosk Argrfecank bit (bt ne 0) 4ek do 4, Alnndard|

Butput <4 wlso rolled channel 0, The stander outpub is |

oluways oper.

¥ Enoch siceasve colt b9 tfepen wpe a nus whannep

and Ach, we 32-bit dereacptr utth bit t seb, bee 2

4k and 40 on , upto bit 30 et, Bee 31 a rawewed,,

* The channel numba couupends te the sndiveduol bet

atk in the multicore! cluatpter +

Examplo :- File Dercurp tory

MH mraddronndl des op tor _ - a

inkeger Arandlet » Mandle2, tarde: Winkeges ate 32-betvalia)

tribal WAtandad oP is open ; lere'pter = 32'howsn cov) (bt 0 seb)

6

te $fppen (" prleLiont"); Mhonde = 32'hovmecoo. Cb't cet)

Aronrdle2 = Sfeopen( "fur cut"); I! Parndbe 22'h0000.0004( vit 2sef)

L 5: $fopen( “fl aeut")? M dvandle = 32'h 0000-0008 ( bit Bact)

Nayana-K, Asst Prof, ECE, svir

1B ECSE

Viele, HDL

6) KiettiIng TO Frees”

* The system task $f display ) tfroncter , ffuate wand

$fsbrobe on ued fo wk fo fe:

¥ There taske ore simelor sin Ayrckon to Anquan, system,

asks $display , growls e&e , Ind thay provide the

wd dedionaf eapalut ty 4 sucking ko fils.

[ome 7 $f display Ce pole dercarptor>, pl, p2---, pnd;

$famonitar(< ple dercniptor>, P41, p2,- pn);

* pl, p2--- PN wom he vasratbles , Atarol names a quoted

Abe

+ A Fleder to, ua mubtichannel descu'pter Lat

wan te ao fle handle o wa diturre eombrastion op

file handles,

+ Vee. ued wuathe Hee outpud to all dele, Hat have

a 1 amowated with Mem cr te pu derarptor ,

Example :- Warkig ko poles

" Honrstder all ~ Landle, deferred an prewous Cramp Gopen)

dake ausaps Aesexep2, deenp3 > Hs fre derewptoy

Anibal

b

descupd = hondlet| Ly Mbitusse on;

Ff Aviplay (desatps , Display 195 Haste files ffletcut 2 stteut

4 (st tps

desi 2 = randie | handle t 5 // leseip 2. 32'hovoo_v00g

Ffdeeplay (desenp> , “Display 2")5 Masset to filer futcout for. cut

dertrip 3 = handle3

Ff-display Coles cup 3,

end

deseuup 4 = 32'hoooa_0003

JM lesrip3 = 32'h0000_0008

"Deeply 3s); Houle bo dk fles.out enty

}

Is

janack , Asst. Pref, ECE, SVIT

Verloy HDL _ - 1BECSE

2) CLOSING FILES

Filer on be ered ith the ayitm task ‘$futose!

USAGE : $fclore Cec pre-hende >):

[Fnample i loscg Rly

$feclore (rand) :

¥ A fole tonmok Le iutten te one Lk uv cloed » The

tomupondiing bet or the multichannel duct, i set to).

¥ The nent ffepen toll van Auue the bet,

* FEN

Gi) DisPLavtne Hrerarcny

—~ He tj ay Awel con be Ae played

| he %m opbon in

| guste touk ;

by mean

any os He display tosks , Fidisplay,

$mawkr oo fstrobe task

7 Wher multiple snratonces of a module enceute Hy

4ome Vewleg ode , the Yom option uy usbingucsh

m adic module iu banes Hhe cubput ering,

A No argument 4s nuded for He tm Sption in the rsplay

tasks:

Example Drsplayerg Hierarchy in

module My

inibal .

$aviplay c Desplayeng tn wm");

enclnedils

MI iva kordiccke medul: M

module kop y

M m14O;

M moc);

M9 3% endreial

Nayana-k, Asst. Prof, ECE, SVIT

Veuleg HDL IBECSE

+ The output fom tye simulation wu Le

| Disptaging tn bepemt |

Decsplaycag an dope md

Tha fede con -Aieplay fut Ierarchuical ramet , Lneluding

Module duukanes , tasks , foctions vand narud Mocks,

(Hii)

— Akselng is dene wath he system task keyword 'batrobe' |

7 Yy many sth atatevants cx entcuted in the soune tomo

dunk var the $uclisplorg fosk, the order in auch the sbatenoit}

anol the $disploy task wore enreuted 4 nondebeaumiatic >

Th Setrobe’ tn waed, cb a obunys erucubed ofter val! obfut |

augnmens stotuvents in Ho tome bre wut have encouted

Tht, fatnobe promis syndwonrcabion mechantsm te

ews tat deta ow displayed only after atl other

seungnmenk stobements ; which whange the data ur that

dima step , rave eneasted »

Enarmple M1 atroboag

alunos @ (poredge Lock)

ated

a=

c=

yy

4;

end

olusays @ Cporedge clock)

$atrobe C*Dusplageng a= hob, Cm %b6") A,c); H desplay vobses at pos

> in Hu above tnampl, , the value at postive edge of clock

au Le dit played vonly after staterant A=b cand €= of

ened 5

> af $aisplag wes uted» ah amught eneecke Lefora Abatement

O=b wnd cad, tu i aploying Af herant values «

=

Nayona-k, Asst. Prof, ECk, svtr

V ewlog HDL IBECSE

Civ) RANDOM Numpee GENERATION

—> Random number guration Mapalr liber vara Aeeutrad fe

gruating ae random ack of tut vetou,

— Random tet & important becuue ot Often. catches

Furdden deugs inthe devin

Random weber generation 4 oli used ue performance

ovals of whip vaachu'bectuncs .

—+ The system tou frondon is used

t sed fon :

Acndem number , gentry

USAGE + $rondom

$random Céseed>)s

—> The value ct Lseed> ds ephenal nd in wed to entry

the somo randem number sequen cath time the tat tru,

> The cseed> parameter can uth de aL Ang , enkegsr, 0

bime vawable.

—* The tusk grandom actus 2 32-bit a4 gned ankeper . AU bits,

bet-select oy Port selects 4 Hhe 32-bit random rum bey,

ton be sted,

Erample :- Random Numbo. Geneakion

Hierwselt sander mbes sand apily Hush Bea ample Rom,

module Lub»

aitege Asad;

[31:07 adda Wunpuk te ROM

uns [310] lobes I output from Row

Rom at (data , addr);

A-sud = 2 5 MW dandownly lfine dhe seed os 2 |

cdurayi@ Cporedge cock) |

add,

= gaandom Crseed) + MN gerescts sordom numbey

enclmecule

¥ 1

Nayana -K, Asst. Prof, ECE, vir s

ISECSB

Viewley HDL

> The random number quusater 4s alte to squeak

Argned integen « Depends

“4 on the ane the frendom

task ts sued

yet can generate pesckive ov mugative enkeges

MW Frample '- Generation af Porative anc Megatie ruumbeu by faut

a4 [23:0] pandt , Aand2

Aondt = grandem % 60;

Aond2 = Etsandom } % bo;

;

M gerarates & Aandam number bly -59 154

1 addeh on 4f eoncodencetion operator to

MBs0xdom pee valug

MN ketween “o wond 54.

|

Te algoutem used by $random i standerds red , Thuwfou,

the some simulation dat run on du ffpent sumuctocoa ull

qenwrots Moruvatent random patterns fou the same seed value.

¥ £ He x |

() Ona rracr zene Memory From Frie

SS EM ORy FROM Foe

— Vetleg produ o aueful agpten tuk to vu tialize

memo fom wo lobe pe.

— Two tasks vary prowded to rcad numbeu in binoay ot

> Keywords “$radmumb’ .surd "grradmemh' ore ued to

Ans be ab'ze memo,

USAGE ; $aradmumb ("< fb_nanu>’, < memory —neura >) »

$rradmemb ( “< fname", < mamory-namo?, < 4tart_addes).

$rrodmenb ("< pram", , , ),

Aoms syatan (usage) forfrtadmemh

+ Th pu-nomo vend mamoy nowy ear mand atoug suhereos

short -oddr sand fins addy as optional ,

14

-

Noyana k, Aest. Pre , LCE, ovir

Veulog HDL

Example Gatiainiy Mem

module dest 5

inten i ;

dnitiot

er

Brradrumb ("init dat", memory);

fer Chao, fee; far ti)

$dsploy Cl Memsuy [40d] = hb", momo lI);

und

the fl “inik dot” veorbois the inilialication data + Addteuo]

aan spurfed on the dabu jule wth" @ wddres |

— Add seer ar sprafred ws tunodenmel numb. Data cs

separated doy wlwbupats, Data van voritain “At! or 'p' , Uru

acetiens viefeelh A Aample fej tnieedat” ib shown bea]

@oor

Heeetiat Olorooy

00000000 +6 101010

@006

WMtizzzz Ood01Ih)

oy , Hee ' ue a

> Kdhen the tut module os stimulated fotlounng eutp a

Memoy LID = xx vxvexy

Memoy [3] = Vy

Memory [3] = 0101010)

Memory £4] = 00000000

Memory [5] = toloiolo

Memon (6J= wiizzez

Meraouy [1] =000011 11

Nayana+k, Asst. Pash) ECE, Svzr 20

Veullog HDL

=

IBECSE

(Wi) VALUE CHANGge Dump Free

> A value change ump (VOD) i an Accrr fe that

Montains Srfermat on about amulodion tm, scope wound

“tana dafintht ons » turd stgnod valu changes th Hes 4 Labion

Fun,

— du arqnols or a adlected set

be wuuHen to a veo fre sclaasing

Pest procenc

ef tigwals tno destin xan

Aumulation .

Aver con take the vob free as orput wand

Waually “eespay tuvardural or formabion , signal volute and

Atgnal rouretoamns

fy ere svmutedion cutput.

vod pl cH the elu PrOxees 4 shown belo.)

$y Debugging serch Avvatyeoy oh snutation unit veo ke

-_ Ayton Eases oar Prowdedl fou

% modulo inskorno

Ved Jote Chdump feb)

DEBUG / Ay

Post Process [|——¥ MEB06/Awatyae

sdlcking modute dudance,

to dump($cumpvan) , name

7 Atorhing onl stopping tho dump Prous

Chdumpon , gdumpohh) cand. cgeresaliiag chwckepeinb ($ clump all)

Mae oh tach bask axe shaun Se he example elo.

AL

21

Noqann: Asst, Prof, ECC, evtr

Veatlog He seca

Emampg ~ Ved fils sytem beaks _

initcod

$etump fre Coy fete vechrnp") 5M avrnalation. yp clumped 42 rey file-dnp

inikial

$edump vars 4 Wno vaxgumnsrds , dump al aupmrnls un the design

dnikiol

$.duump vars C1, Lop) Mdaump vau'abtes in module sn tare top, The

Mrurnber 4 sirdivates wet of Auernichay « Dump

Hong dnieaady Aovel Lelovs top ) e+ udsump

I vaswadtas sic Ap. only

unibial

}] Pdumpvau C2, Aeprms.); I dump upto 2 fats of Aeenaachy below topmg

hind biod

Facuumpvars (0) kopmt)) INumba 0 meou dump te erching Areva

W helo Lopimt

M Adat ond shop dump prouy

ini kid .

begin

tdismp on W skort the whump prowy

#100000 $dump MSW Alop ths lump procs AbEA 100, 00D hime n'y

ond

Hou dot

Fdermpalt 3 If Vrsads a celuckparnt «Deny count value of a

M VCD vastabtey

> Th f dmp hile ound $dumpvars barks oro novmally

You might also like

- Spring Notes by Nataraz Sir - JavabynatarajNo ratings yetSpring Notes by Nataraz Sir - Javabynataraj290 pages

- Bob Zeidman - Verilog Designer's Library-Prentice Hall (1999) PDF100% (1)Bob Zeidman - Verilog Designer's Library-Prentice Hall (1999) PDF411 pages

- Verilog Designers Library 0130811548 9780130811547 - CompressNo ratings yetVerilog Designers Library 0130811548 9780130811547 - Compress430 pages

- Introduction To Mechanical Engineering 101No ratings yetIntroduction To Mechanical Engineering 1015 pages

- Simplified FPGA Design Implementation FlowNo ratings yetSimplified FPGA Design Implementation Flow36 pages