0% found this document useful (0 votes)

67 views16 pages6 Synthesis and Simulation Model

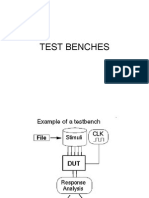

The document discusses VHDL as a simulation language, emphasizing its event-driven simulation model which includes concepts like simulation time, delta time, and event processing. It explains the differences between simulating combinational and sequential circuits, highlighting the importance of event ordering and sensitivity lists. Additionally, it covers synthesis models, detailing how VHDL constructs must conform to specific templates for successful hardware mapping and synthesis.

Uploaded by

Jaydeep KumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

67 views16 pages6 Synthesis and Simulation Model

The document discusses VHDL as a simulation language, emphasizing its event-driven simulation model which includes concepts like simulation time, delta time, and event processing. It explains the differences between simulating combinational and sequential circuits, highlighting the importance of event ordering and sensitivity lists. Additionally, it covers synthesis models, detailing how VHDL constructs must conform to specific templates for successful hardware mapping and synthesis.

Uploaded by

Jaydeep KumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 16