0% found this document useful (0 votes)

4 views14 pagesVerilog Presentation

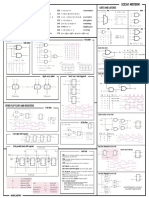

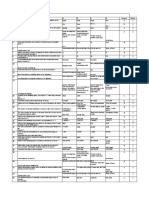

The document compares combinational and sequential circuits, highlighting that combinational circuits depend solely on present inputs while sequential circuits also consider previous inputs. It discusses the role of clocks in controlling circuit processes and introduces Verilog's four levels of abstraction: switch, gate, data flow, and behavioral levels. Additionally, it covers various Verilog concepts such as data types, multiplexers, D flip-flops, and counters with synchronous and asynchronous resets.

Uploaded by

aziz khanCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

4 views14 pagesVerilog Presentation

The document compares combinational and sequential circuits, highlighting that combinational circuits depend solely on present inputs while sequential circuits also consider previous inputs. It discusses the role of clocks in controlling circuit processes and introduces Verilog's four levels of abstraction: switch, gate, data flow, and behavioral levels. Additionally, it covers various Verilog concepts such as data types, multiplexers, D flip-flops, and counters with synchronous and asynchronous resets.

Uploaded by

aziz khanCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 14