0% found this document useful (0 votes)

12 views44 pagesLecture 5

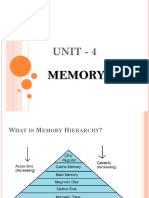

The document discusses the memory hierarchy in computer systems, detailing the various levels of memory storage from registers to secondary storage, and their characteristics such as speed, size, and cost. It emphasizes the principles of locality and caching, explaining how these concepts optimize memory access and efficiency. Additionally, it covers different types of memory, including volatile and non-volatile options, and outlines caching strategies and write policies for efficient data management.

Uploaded by

Anwar SheikhCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

12 views44 pagesLecture 5

The document discusses the memory hierarchy in computer systems, detailing the various levels of memory storage from registers to secondary storage, and their characteristics such as speed, size, and cost. It emphasizes the principles of locality and caching, explaining how these concepts optimize memory access and efficiency. Additionally, it covers different types of memory, including volatile and non-volatile options, and outlines caching strategies and write policies for efficient data management.

Uploaded by

Anwar SheikhCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 44