0% found this document useful (0 votes)

179 views101 pagesProcessor Datapath and Control

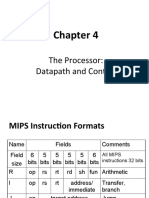

This document summarizes key aspects of a processor's datapath and control unit. It describes the goals of processor implementation including balancing instruction supply, execution, and data supply rates. It reviews sequential logic design concepts. It then details the datapath components for instruction fetch, execution including different instruction types, and data memory. It shows how these components are connected and controlled for a single-cycle implementation. Finally, it summarizes the control signals needed and their values for different instruction types. The overall goal is to efficiently implement a MIPS processor datapath and control unit.

Uploaded by

api-26072581Copyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

179 views101 pagesProcessor Datapath and Control

This document summarizes key aspects of a processor's datapath and control unit. It describes the goals of processor implementation including balancing instruction supply, execution, and data supply rates. It reviews sequential logic design concepts. It then details the datapath components for instruction fetch, execution including different instruction types, and data memory. It shows how these components are connected and controlled for a single-cycle implementation. Finally, it summarizes the control signals needed and their values for different instruction types. The overall goal is to efficiently implement a MIPS processor datapath and control unit.

Uploaded by

api-26072581Copyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

/ 101