Prepared by: Engr. Mary Jane B.

Becite

PROGRAMMABLE

LOGIC DEVICES

�Programmable Logic

Devices

Programmable Logic Devices (PLDs) are IC chips

with internal logic gates connected by electronic

fuses.

These fuses can be blown (by programming) to

obtain different circuit configurations.

Three classes of PLDs are :

Programmable Logic Array (PLA)

Programmable Read Only Memory (PROM)

Programmable Array Logic (PAL)

�Programmable Logic

Devices

Fixed

AND array

Inputs

Fuses

Fused

programmable

OR array

Outputs

Programmable Read Only Memory (PROM)

Fuses

Inputs

Fused

programmable

AND array

Fixed

OR array

Outputs

Programmable Array Logic (PAL)

Fuses

Inputs

Fused

programmable

AND array

Fuses

Fused

programmable

OR array

Programmable Logic Array (PLA)

Outputs

�Programmable Logic

Devices

Programming an array blowing the fuses.

A A' B B'

A A' B B'

(a) Unprogrammed

x1

x1 = A.B

x2

x2 = A'.B

x3

x3 = A.B'

(b) Programmed

Example of a basic AND array

�Programmable Logic

Devices

PLDs use diodes. A PN diode is an electronic device

formed by creating a junction of two types of semiconductor materials, p type and n type.

Forward-biased: When p side (anode) is more

positive than n side (cathode), it behaves as a

closed switch.

Reverse-biased: When cathode is more positive

than anode, it behaves as an open circuit.

P

Forward-biased (closed circuit)

PN junction diode and

schematic symbol.

Reverse-biased (open circuit)

�PN Diode Operation

PN diode operation for digital applications.

(a) With pull-up resistor.

(b) Reverse-biased: diode open; B pulled

up to 1.

(c) Forward-biased: diode shorted, forcing

B to 0.

(d) With pull-down resistor.

(e) Reverse-biased: diode open; B

pulled down to 0.

(f) Forward-biased: diode shorted,

forcing B to 1.

�AND Logic Arrays

AND function realised with a diode array.

(a) Basic configuration.

(b) All diodes open; f pulled up to 1.

(c) One diode shorted, forcing f to 0.

(d) Multiple diodes shorted, forcing f to 0.

�OR Logic Arrays

OR function realised with a diode array.

(a) Basic configuration.

(b) All diodes open; f pulled up to 0.

(c) One diode shorted, forcing f to 1.

�Two-level AND-OR

Arrays

AND and OR circuits can be interconnected to realise

any arbitrary switching function.

Example: f(a,b,c)=a.b.c'+b'.c

�Programmable Logic Array (PLA)

Combination of a programmable AND array followed

by a programmable OR array.

Example: Design a PLA to realise the following three

logic functions and show the internal connections.

f1(A,B,C,D,E) = A'.B'.D' + B'.C.D' + A'.B.C.D.E'

f2(A,B,C,D,E) = A'.B.E + B'.C.D'.E

f3(A,B,C,D,E) = A'.B'.D' + B'.C'.D'.E + A'.B.C.D

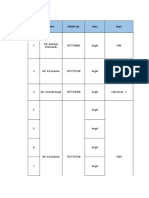

�Realising Logic Functions with PLAs

X

B

X

X

X

X

X

X

X

D

X

X

X

Programmable

AND array

Programmable

OR array

f1

X

P1

A'B'D'

P2

P3

P4

f2

P5

P6

P7

A'BCDE'

B'CD'E

A'BCD

B'CD'

A'BE

B'C'D'E

f3

f1(A,B,C,D,E) = A'.B'.D' +

B'.C.D' + A'.B.C.D.E'

f2(A,B,C,D,E) = A'.B.E +

B'.C.D'.E

f3(A,B,C,D,E) = A'.B'.D' +

B'.C'.D'.E + A'.B.C.D

�Read-Only Memory

(ROM)

A semi-conductor memory is a device where data can

be stored and retrieved.

Logically, this memory device can be regarded as a

table of memory cells (data).

Addresses

0

1

2

3

:

:

:

:

n

1-word data

:

:

word size

1-bit data

�Read-Only Memory (ROM)

A Read-Only Memory (ROM) is a memory device

where data are read from, but not written to.

Writing is done at time of customisation, or, by

special programming devices (programmable ROM).

Any Boolean expression can be implemented using

ROM. Procedure: Obtain a truth table, treat the

inputs as addresses and outputs as data.

Advantage: Boolean functions directly implemented.

Disadvantages: Dont care conditions not used, and

limited input variables (e.g. 10 inputs 1K, 16 inputs

64K, 20 inputs 1M).

�Read-Only Memory

(ROM)

Different types of ROM devices available:

ROM: Read-Only Memory

Data written into memory by mask programming

during manufacturing time. Expensive start-up cost

but economical for high volume. Cannot be erased

after data are programmed in.

PROM: Programmable ROM

Semi-custom chip. Fuses can be broken by

special hardware programmer unit. Cost-effective

for low volumes. Cannot be erased after

programming.

�Read-Only Memory

(ROM)

EPROM: Erasable PROM

Similar to PROM except that data can be

completely erased by exposure to ultra-violet

light.

EEPROM: Electrically Erasable PROM

A PROM where data can be selectively erased

by hardware programmer unit, rather than by

ultra-violet light. Useful for remote devices which

can be re-programmed from a distance.

�Programmable Read-Only

Memory (PROM)

Devices with fixed AND array (which is a decoder)

and programmable OR array.

The AND array (decoder) generates all 2n possible

minterm products of its n inputs (often referred to

as n-to-2n decoder).

n input lines, m output lines.

Bit combination of input variables address

Bit combination of output lines word (each word

contains m bits).

�Programmable Read-Only

Memory (PROM)

X

I1

I2

Programmable

OR array

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Fixed

AND array

I0

O1

O2

..

.

Ok

..

.

m0

m1

m2

m3

m4

Minterms

m5

m6

m7

Programmable read-only memory (PROM) can realize K functions f(I 2,I1,I0).

�Programmable Read-Only

Memory (PROM)

n inputs

2n x m ROM

m outputs

2n x m ROM

=> 2n words, each word m bits

=> 2n x m bits

�Programmable Read-Only

Memory (PROM)

Minterms

Address

input

A0

A1

A2

A3

A4

5 x 32

decoder

0

1

2

31

.

.

.

...

...

...

...

128 fuses

Logic construction of a 32 x 4 ROM.

F1

F2

F3

F4

�Realising Logic Functions with

PROMs

Example (8x3 ROM):

f1(A,B,C) = A.B + B'.C

f2(A,B,C) = (A+B'+C).(A'+B)

f3(A,B,C) = A + B.C

First, we convert each function to canonical SOP form.

f1(A,B,C) = A.B + B'.C = A.B.C' + A.B.C + A'.B'.C + A.B'.C

= m(1,5,6,7)

f2(A,B,C) = (A+B'+C).(A'+B)

= (A+B'+B).(A'+B+C').(A'+B+C)

= M(2,4,5) = m(0,1,3,6,7)

f3(A,B,C) = A + B.C = A.B'.C' + A.B'.C + A.B.C' + A.B.C + A'.B.C

= m(3,4,5,6,7)

�Realising Logic Functions with

PROMs

X

X

X

B

X

Programmable

OR array

X

X

X

X

X

m1

X

X

f1 = m(1,5,6,7)

f2 = m(0,1,3,6,7)

f3 = m(3,4,5,6,7)

m6

m7

X

X

m0

X

X

m2

X

X

X

X

X

m3 m4 m5

Minterms

Fixed

AND array

�Realising Logic Functions with

PROMs

Minterms

Address

input

C

B

A

8 x 3 ROM

0:

1:

2:

3:

4:

5:

6:

7:

0

1

0

0

0

1

1

1

1

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

3x8

decoder

0

1

2

3

4

5

6

7

f1 = m(1,5,6,7)

f3 = m(3,4,5,6,7)

f2 = m(0,1,3,6,7)

�Programmable Array Logic (PAL)

Introduced in late 1970s by Monolithic Memories

Inc. as lower cost replacement for logic gates,

PROMs, and PLAs.

PAL has programmable AND array and fixed OR

array.

Less general than PLA but easier to manufacture

and design.

Product terms belong to different OR gates,

cannot be shared.

�Programmable Array Logic (PAL)

A

P1

P2

O1

P3

P4

P5

O2

P6

Programmable AND

array

Fixed

OR array

�Realising Logic Functions with PALs

Procedure is to obtain minimal SOP expressions.

Example:

f(A,B,C,D) = A'.B'.D' + B'.C.D' +

A'.B.C.D

f(A,B,C,D) = A'.B + B'.C.D'

f(A,B,C,D) = A'.B'.D' + B'.C'.D' +

A'.B.C.D

�Realising Logic Functions with

PALs

f(A,B,C,D) = A'.B'.D' + B'.C.D'

+ A'.B.C.D

f(A,B,C,D) = A'.B + B'.C.D'

f(A,B,C,D) = A'.B'.D' + B'.C'.D'

+ A'.B.C.D

P1

P3

P4

x

x

x

P5

P6

x x

x x

P4

x

x x

x x

x

P5

x

P2

P6

PAL realisation

of fa, f and fr.

x

x

x

x