8051 Micro Controllers

Introduction

Architecture

Signal Description

�What is a Micro controller

Its

a Microprocessor with integrated

peripherals

All peripherals are integrated in a single

chip

System cost is low

Size of system becomes small

Reliable than microprocessor based systems

Eternal memory ROM peripherals can be

integrated

Software security feature is available

40 pin 8 bit microcontroller has all this.

�Micro controller

microprocessor

�Difference of MC and MP

�differences

�INTEL 8051

40

PIN IC

Did not have a on chip EPROM

8751 was first MC with EPROM

8951 is 8051 + EEPROM

128

byte RAM

4kb ROM

4 , 8 bit I/o PORTS

2 timers 16 bit

UART- universal asynchronous remote

transceiver

�Architecture

�Architecture of 8051

ACC-

Accumulator

ACC or A, 8 bit

B-

reg

The reg is used to store one of the operands for multiply and

divide instructions.

PSW-

Program Status Word

Flags contain the status information and is considered as spl.

Fun. Reg.

Stack

Pointer SP-

8 bit reg, incremented before the data stored onto the stack

using the push or call.

After reset SP is initialized to 07H.

Here the stack pointer is incremented.

Data

Pointer: DTPR

16 bit reg contains a higher byte (DPH) and lower byte (DPL) of a

16 bit external RAM address.

�PORT

0-3 Latches & Drivers :

These four I/O ports- - P0, P1,P2,P3

Serial

Data Buffer (SBUF):

Two independent registers

One Transmit buffer PISO- parallel in serial out

Second Receive buffer- SIPO- serial in parallel out

Used for serial communication

Timer

Registers:

Two 16 bit timers accessed as lower and higher

order byte

TL0, TH0- timer 0

TL1, TH1- timer 1, lower and Higher respectively.

Control

Registers

Special function registers IP, IE,

TMOD,TCON,SCON,PCON contains status of

interrupt, timer/counter, serial port

�Timing

and control unit

Timing for the internal operation of the circuit.

Oscillator

Generating clock signals

Instruction

Reg:

Decodes the opcode for execution

EPROM

RAM

& Program address reg.

and RAM address register: 128 byte

ram

ALU:

Performs 8 Bit arithmetic and logical oerations

Special

Function Register bank:

Addressed using respective address - 80H to FF H

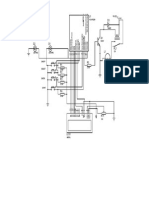

�Pin diagram

Vcc- 5V supply

Vss- Ground

RESET- resets 8051 if high for

2 machine cycles

ALE/PROG: - used if external

addressing is used. Else if

EPROM is used.

EA- external enable

PSEN- program store enable

PORT 0.0-0.7- Along with

address

PORT 1.0-1.7- 8 bit

bidirectional

PORT 2.0-2.7- along with

address

PORT 3.0-3.7

XTAL1,XTAL2Inbuilt oscillator and external

crystal pins

8051- 12MHz to 16Mhz freq.

��Registers

�RAM memory space allocation in

the 8051

14

�PSW (Program Status word) / Flag

Register

�Stack pointer (SP)

Stack pointer (SP) is an 8-bit register at address 81H.

It contains the address of the data item currently on

top of the stack.

Pushing increments SP before writing the data

(opposite to most microprocessors)

Popping

from the stack reads the data and

decrements the SP

8051 stack is kept in the internal RAM

Depending

on the initial value of the SP, stack can

have different sizes

Example:

MOV SP,#5FH

�Data Pointer

Data pointer (DPTR): is used to

access external data or code.

DPTR is a 16 bit register at

addresses 82H (low byte) and

83H (high byte).

The data pointer is used in

operations regarding external

RAM and some instructions

involving code memory.

�(I/O PORTS)PORT0, PORT1, PORT2, PORT3

One of the

most useful

features of the

8051 is four

bidirectional

I/O ports.

Each port also

has an output

drive and an

input buffer.

�Addressing Modes

There are 5 types of addressing

modes.

1.

2.

3.

4.

5.

Register addressing.

Direct addressing.

Register indirect addressing.

Immediate addressing.

Index addressing.

�Register Addressing Mode

In

register addressing mode; the source

and/or destination is a register.

In

this case; data is placed in any of the 8

registers(R0-R7); in instructions it is specified

with letter Rn (where n indicates 0 to 7).

1.

ADD A, Rn (This is general instruction).

2.

ADD A, R5 (This instruction will add the

contents of register R5 with the accumulator

contents).

�Direct Addressing Mode

In direct addressing mode; the

address of memory location

containing data to be read is

specified in instruction.

MOV A, 25H (This instruction will

read/move the data from

internal RAM address 25H and

store it in the accumulator.

�Register Indirect Addressing

Mode

In register indirect addressing

mode; the contents of the

designated register are used as a

pointer to memory.

MOV A,@R0 This instruction moves

the data from the register whose

address is in the R0 register into

the accumulator.

�Immediate Addressing

Mode

In immediate addressing mode, the

data is given with the instruction

itself.

MOV A, #47H (This instruction will

move the data 47H to accumulator.

# is used when ever you are moving a

data not for addresses.

�Index Addressing Mode

1.

Offset (from accumulator) is added to

the base index register( DPTR OR

Program Counter) to form the effective

address of the memory location.

MOVC A, @ A + DPTR ( This

instruction moves the data from the

memory to accumulator; whose

address is computed by adding the

contents of accumulator and DPTR)

�Instruction Set

1.

2.

3.

4.

5.

Data transfer instructions.

Arithmetic instructions.

Logical instructions.

Logical instructions with bits.

Branch instructions.

�Data Transfer Instructions

These

instructions move the

content of one register to another

one.

Data

can be transferred to stack

with the help of PUSH and POP

instructions.

�Data Transfer Instructions

MOV A, Rn

MOV A, direct

MOV A, @Reg indirect

MOV A, #data

MOV Rn, A

MOV Rn, direct

MOV Rn, #data

MOV direct, A

MOV direct, Rn

MOV direct, direct

MOV direct, @Ri

MOV direct, #data

MOV @Ri, A

MOV @Ri, direct

MOV @Ri, #data

�Arithmetic Instructions

ADD

8-bit addition between the accumulator (A) and a

second operand.

The result is always in the accumulator.

The CY flag is set/reset appropriately.

ADD A, # 34H

ADDC

8-bit addition between the accumulator, a second

operand and the previous value of the CY flag.

Useful for 16-bit addition in two steps.

The CY flag is set/reset appropriately.

ADDC A , Rx

28

�SUBB

Subtract with Borrow.

Subtract an operand and the previous value of

the borrow (carry) flag from the accumulator.

A A - <operand> - CY.

The result is always saved in the accumulator.

The CY flag is set/reset appropriately.

�Logical Instructions

ANL

/ ORL

Work on byte sized operands or the

CY flag.

ANL

ANL

ANL

ANL

ANL

ANL

A, Rn

A, direct

A, @Ri

A, #data

direct, A

direct, #data

�Logical Instructions

SWAP

RLA

RLC

RRA

RRC

�Branching Instructions

Compare and Jump if Not Equal

CJNE

Compare the magnitude of the two

operands and jump if they are not equal.

The values are considered to be unsigned.

The Carry flag is set / cleared appropriately.

32

CJNE

CJNE

CJNE

CJNE

A, direct, rel

A, #data, rel

Rn, #data, rel

@Ri, #data, rel

�Branching Instructions

Decrement and Jump if Not Zero DJNZ

Decrement the first operand by 1 and jump

to the location identified by the second

operand if the resulting value is not zero.

DJNZ Rn, rel

DJNZ direct, rel

No Operation

NOP

33