100% found this document useful (1 vote)

78 views20 pagesPresentation ASIC Programming: By, Nayan Prajapati (10MEEC13) Rakesh Prajapati (10MEEC14) MEEC, Sem-I, KIT&RC

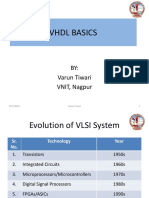

The document provides an overview of ASIC programming using hardware description languages like VHDL and Verilog. It discusses key concepts in VHDL like versions, capabilities, configuration and packages. It also provides examples of functions and procedures in VHDL. The document compares VHDL and Verilog and provides sample code for a counter circuit in Verilog and an adder module in SystemC.

Uploaded by

rocky_ec08Copyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

100% found this document useful (1 vote)

78 views20 pagesPresentation ASIC Programming: By, Nayan Prajapati (10MEEC13) Rakesh Prajapati (10MEEC14) MEEC, Sem-I, KIT&RC

The document provides an overview of ASIC programming using hardware description languages like VHDL and Verilog. It discusses key concepts in VHDL like versions, capabilities, configuration and packages. It also provides examples of functions and procedures in VHDL. The document compares VHDL and Verilog and provides sample code for a counter circuit in Verilog and an adder module in SystemC.

Uploaded by

rocky_ec08Copyright

© Attribution Non-Commercial (BY-NC)

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

/ 20