0% found this document useful (0 votes)

74 views80 pagesIo Module5

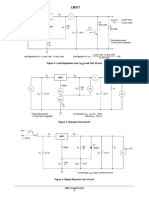

The document discusses input/output organization and describes various I/O interfaces and data transfer techniques used in computer systems. It covers accessing I/O devices through memory-mapped and isolated I/O, examples of I/O devices like keyboards, and methods of I/O data transfer including programmed I/O, DMA, and interrupts. It also describes common external interfaces for I/O like serial transmission, parallel interfaces, and specific interfaces such as EIA-232 and parallel printers.

Uploaded by

bijan shresthaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

74 views80 pagesIo Module5

The document discusses input/output organization and describes various I/O interfaces and data transfer techniques used in computer systems. It covers accessing I/O devices through memory-mapped and isolated I/O, examples of I/O devices like keyboards, and methods of I/O data transfer including programmed I/O, DMA, and interrupts. It also describes common external interfaces for I/O like serial transmission, parallel interfaces, and specific interfaces such as EIA-232 and parallel printers.

Uploaded by

bijan shresthaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

/ 80