0% found this document useful (0 votes)

55 views28 pagesPipeline Processing

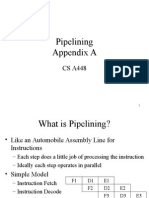

This document discusses pipelining in microprocessors. It defines pipelining as a technique where a microprocessor begins executing a second instruction before the first is completed. The pipeline is divided into stages where each stage performs part of the instruction processing concurrently. This allows new instructions to be fetched while other stages are performing operations. Pipelining improves processor throughput and reduces average instruction time compared to an unpipelined processor. However, it requires careful design to balance the stages and avoid issues like bubbles or synchronization problems that reduce its efficiency. Examples are provided to illustrate how speedup is calculated from pipelining.

Uploaded by

anismitaray14Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

55 views28 pagesPipeline Processing

This document discusses pipelining in microprocessors. It defines pipelining as a technique where a microprocessor begins executing a second instruction before the first is completed. The pipeline is divided into stages where each stage performs part of the instruction processing concurrently. This allows new instructions to be fetched while other stages are performing operations. Pipelining improves processor throughput and reduces average instruction time compared to an unpipelined processor. However, it requires careful design to balance the stages and avoid issues like bubbles or synchronization problems that reduce its efficiency. Examples are provided to illustrate how speedup is calculated from pipelining.

Uploaded by

anismitaray14Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

/ 28