0% found this document useful (0 votes)

73 views19 pagesPipelining. Pipeline Hazards: Sabina Batyrkhanovna

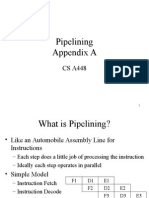

Pipelining is a technique used in microprocessors where the execution of instructions is overlapped or divided into multiple stages. This allows newer instructions to begin executing before earlier ones have finished. While pipelining improves processor efficiency and speeds up execution time, it can introduce pipeline hazards like structural hazards, data hazards, and control hazards that disrupt smooth execution and require stalling the pipeline. Overall, pipelining is advantageous by making more efficient use of the processor, but involves additional hardware and may limit the processor to less than full speed due to pipeline hazards.

Uploaded by

Naski KuafniCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

73 views19 pagesPipelining. Pipeline Hazards: Sabina Batyrkhanovna

Pipelining is a technique used in microprocessors where the execution of instructions is overlapped or divided into multiple stages. This allows newer instructions to begin executing before earlier ones have finished. While pipelining improves processor efficiency and speeds up execution time, it can introduce pipeline hazards like structural hazards, data hazards, and control hazards that disrupt smooth execution and require stalling the pipeline. Overall, pipelining is advantageous by making more efficient use of the processor, but involves additional hardware and may limit the processor to less than full speed due to pipeline hazards.

Uploaded by

Naski KuafniCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 19