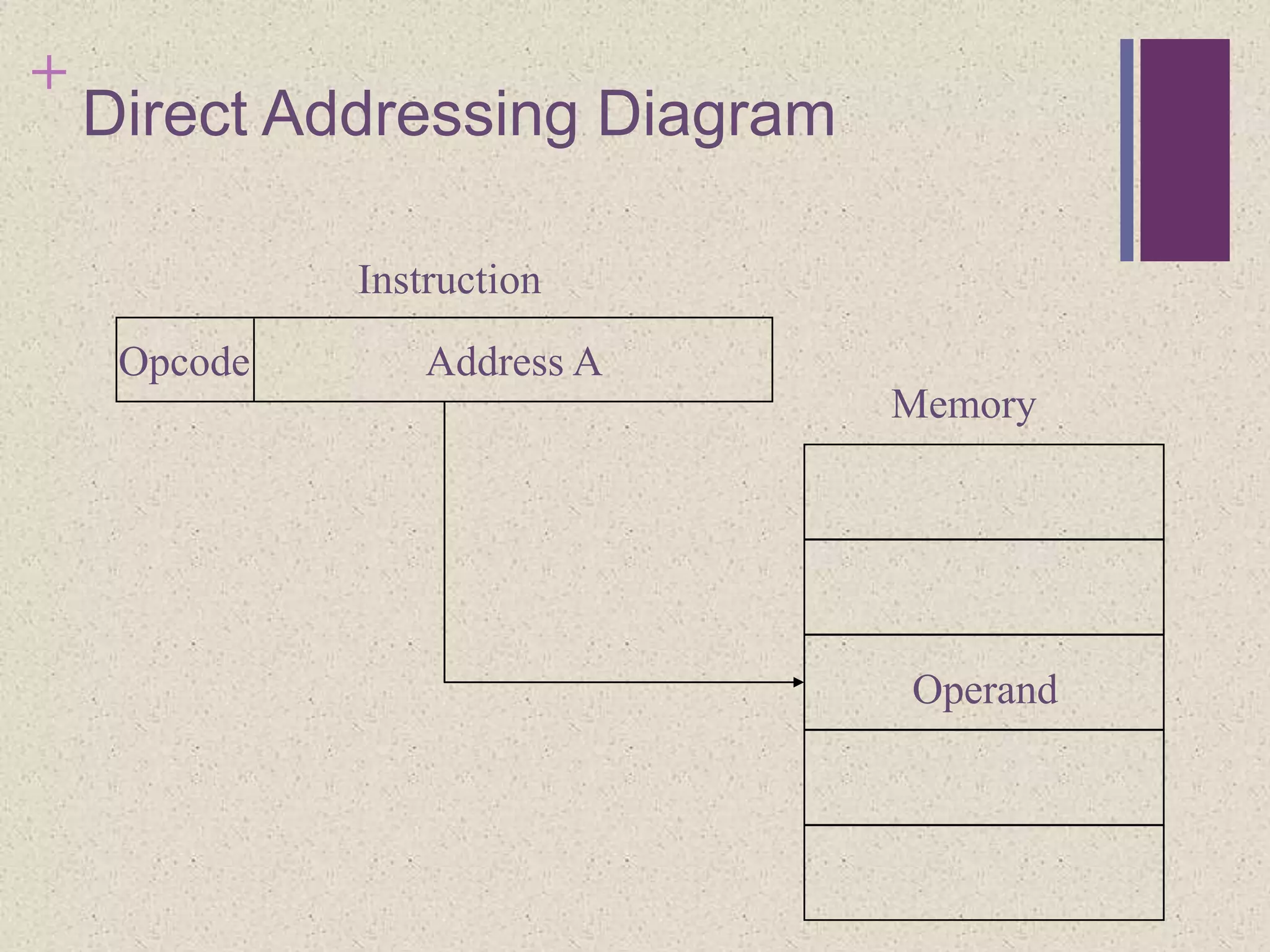

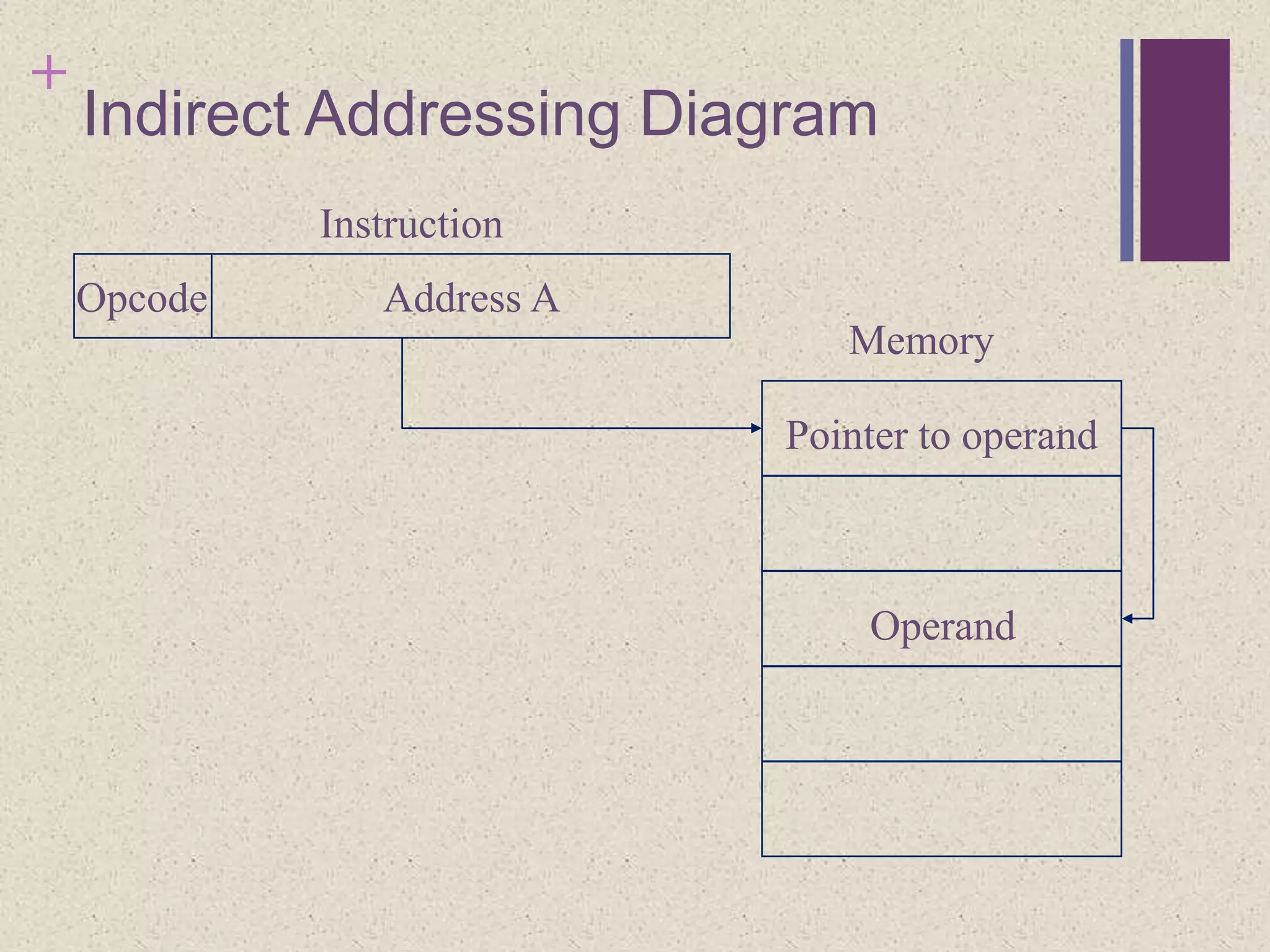

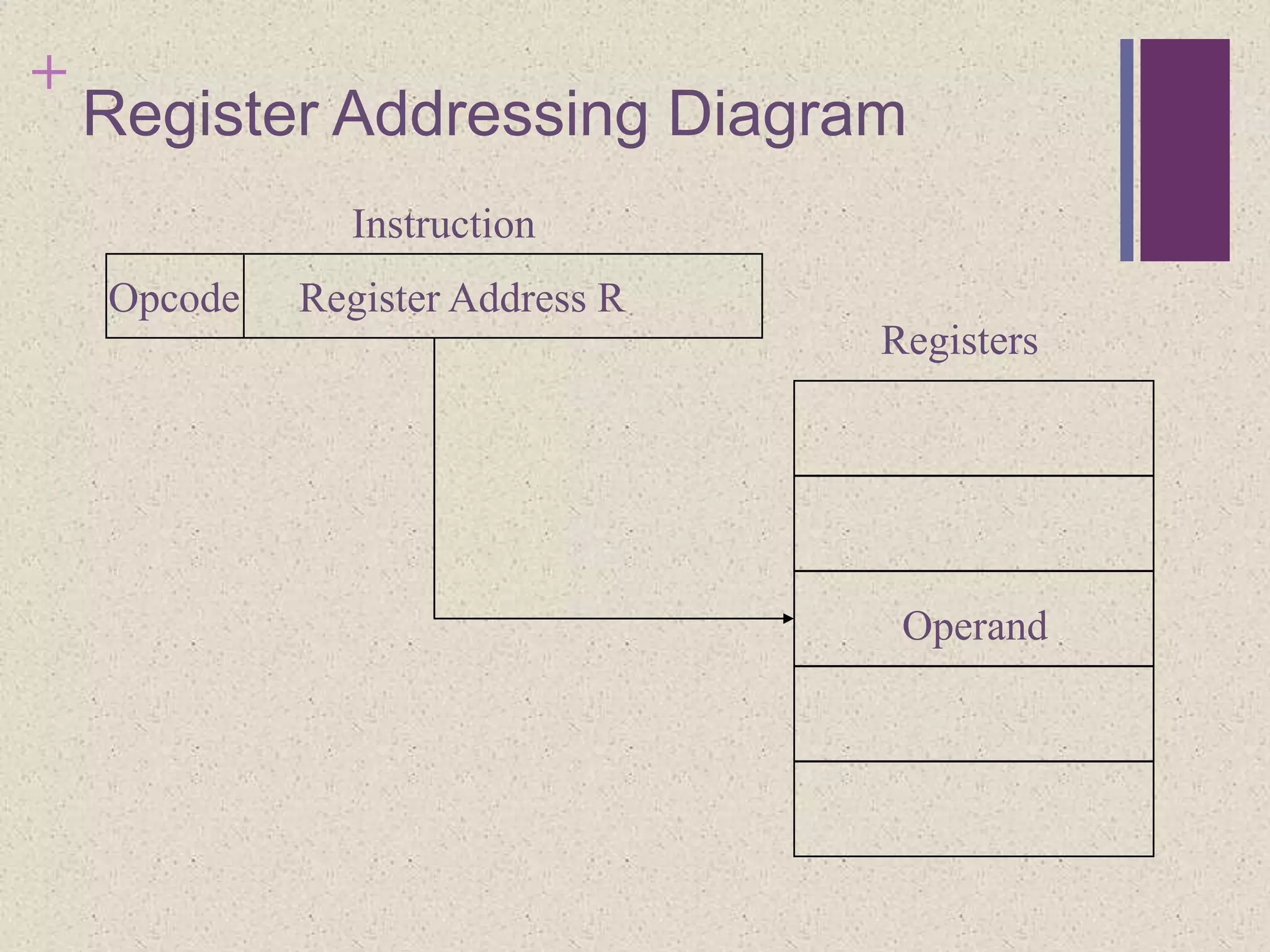

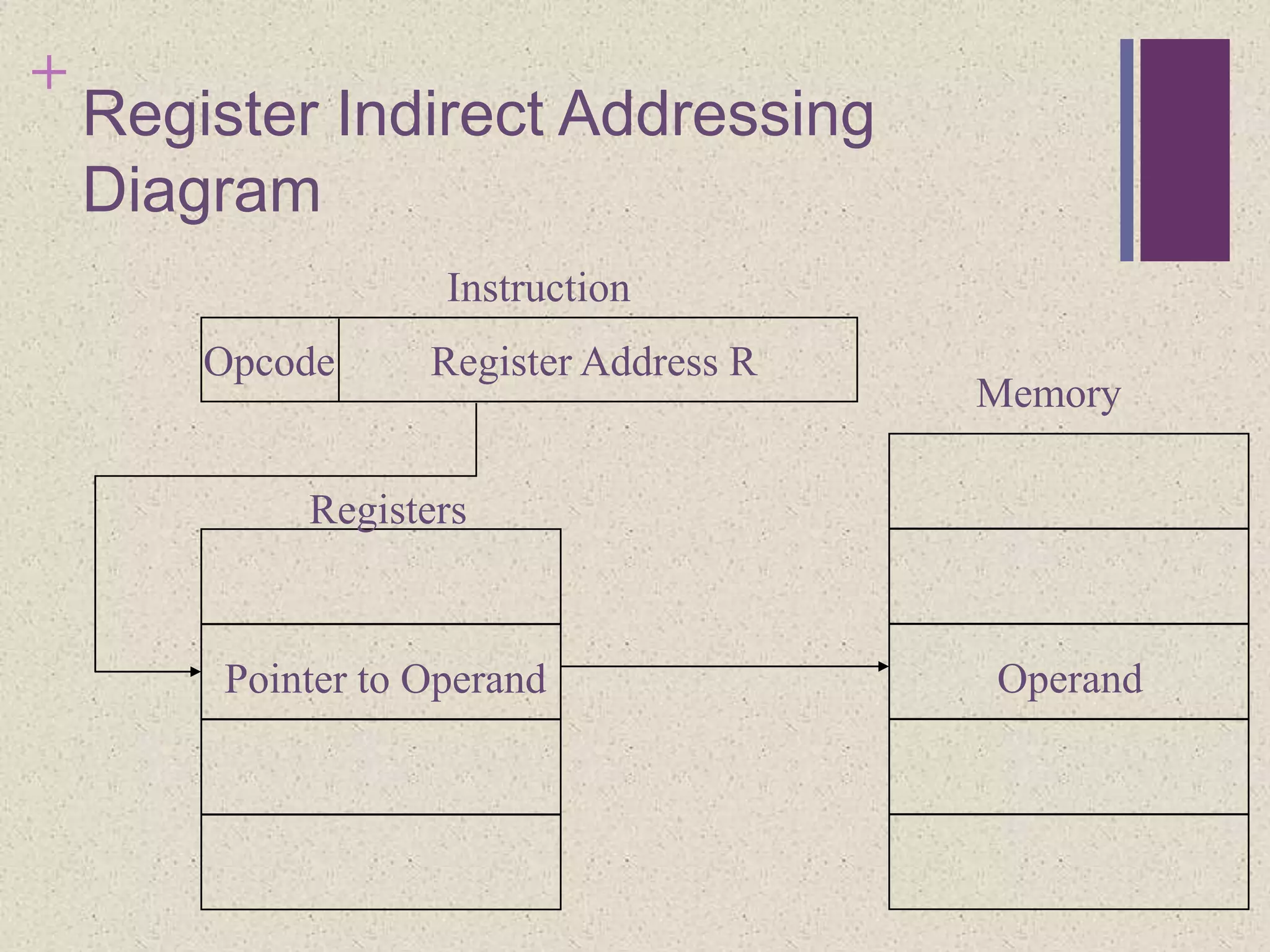

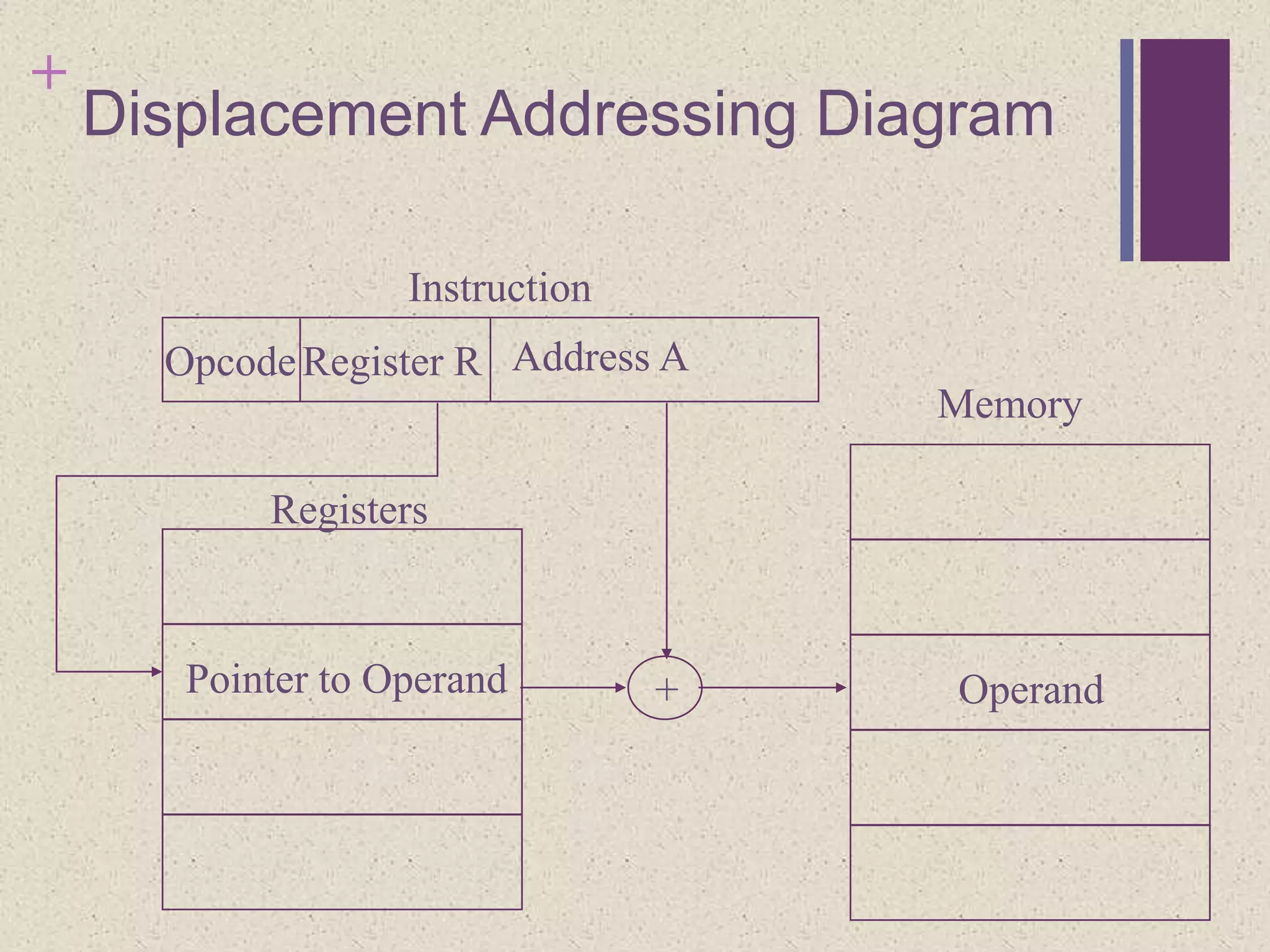

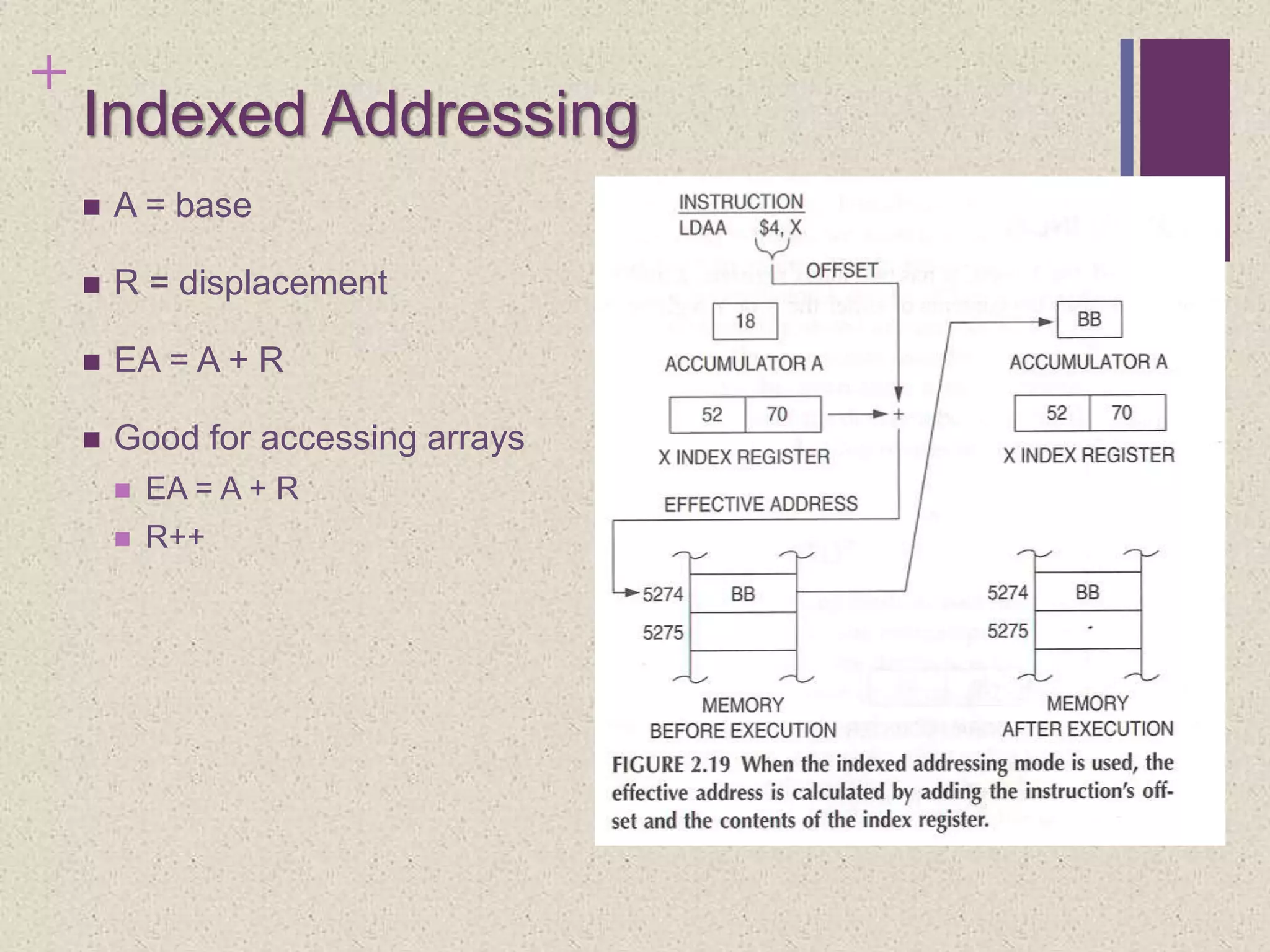

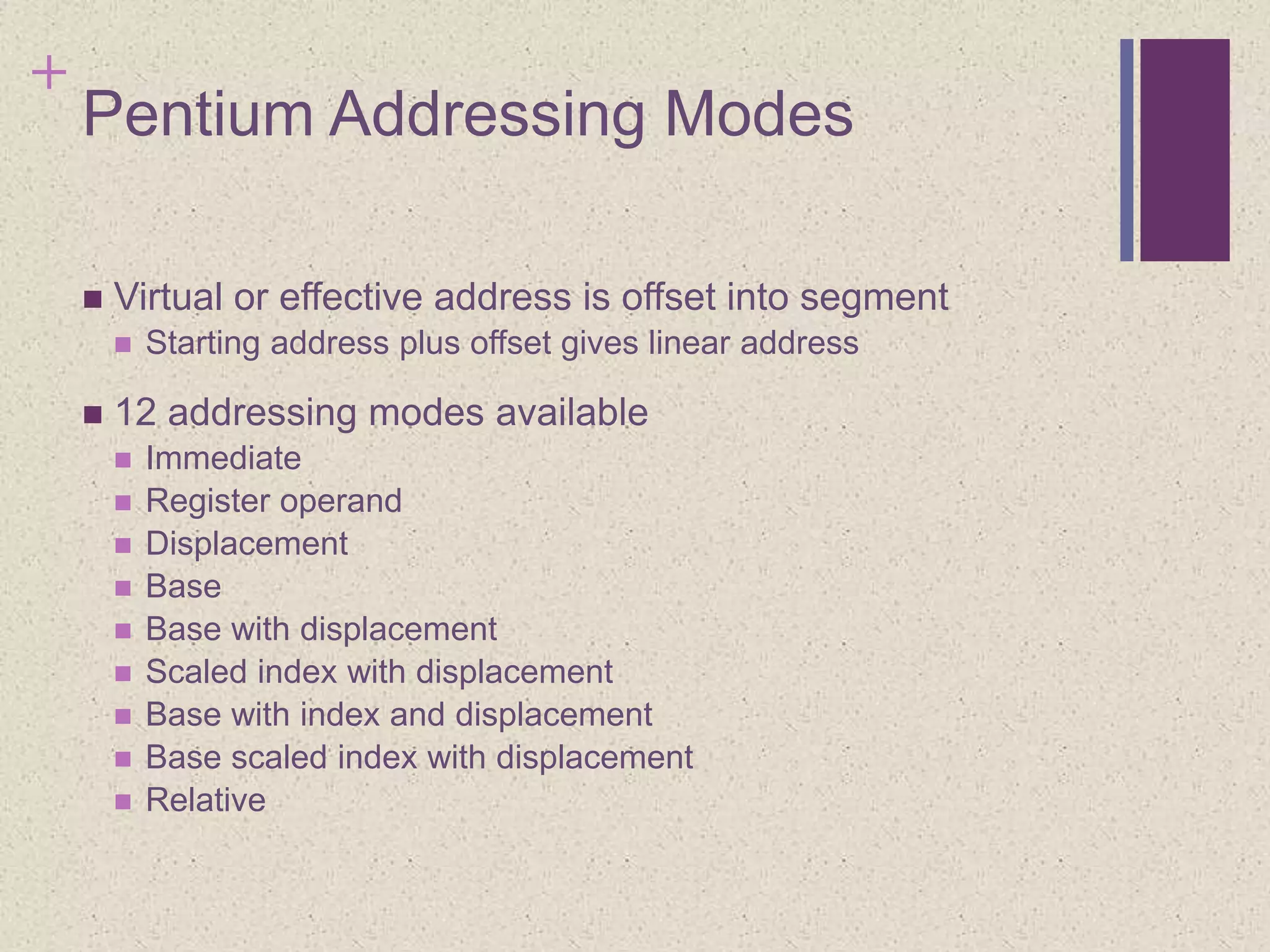

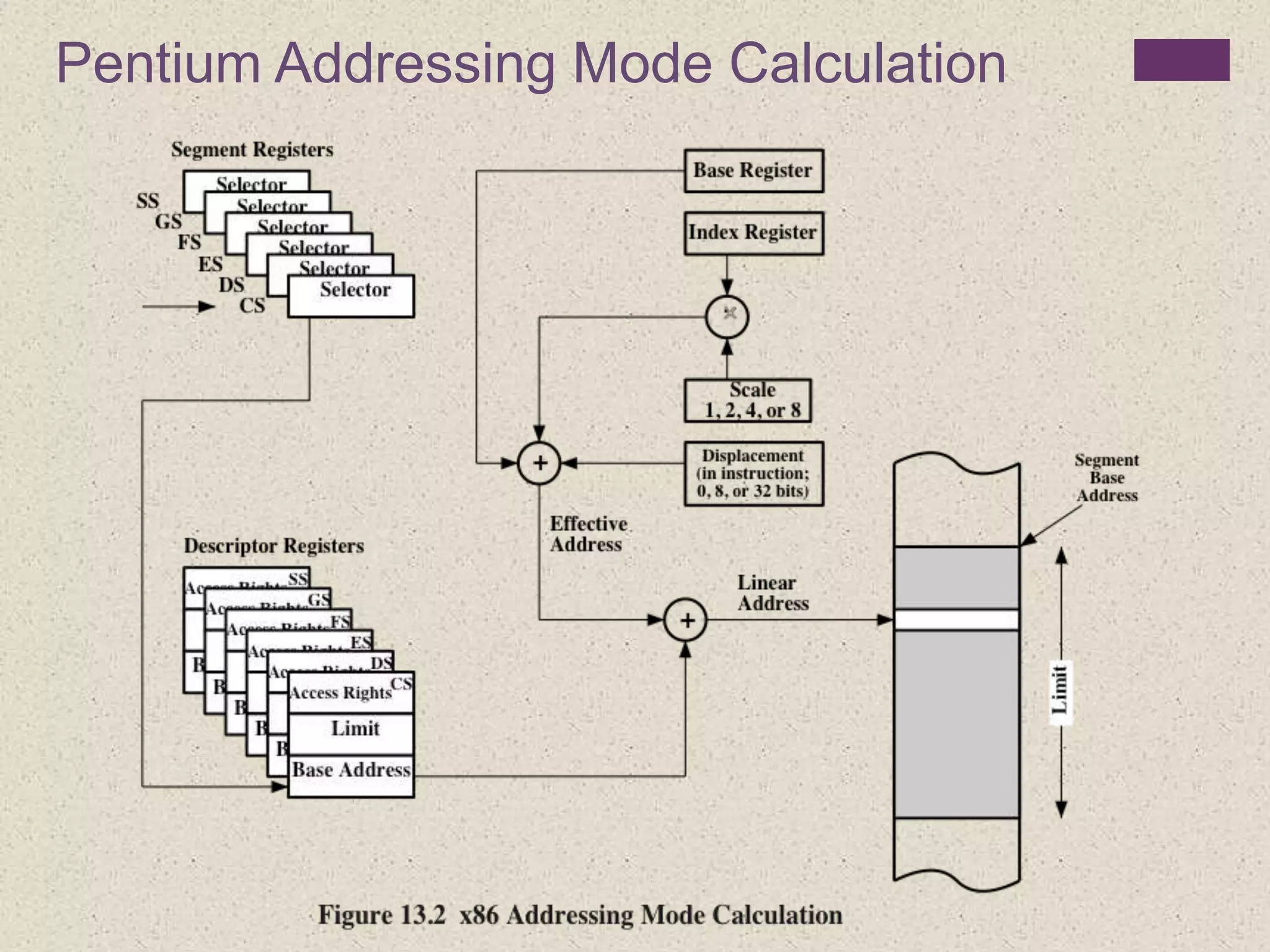

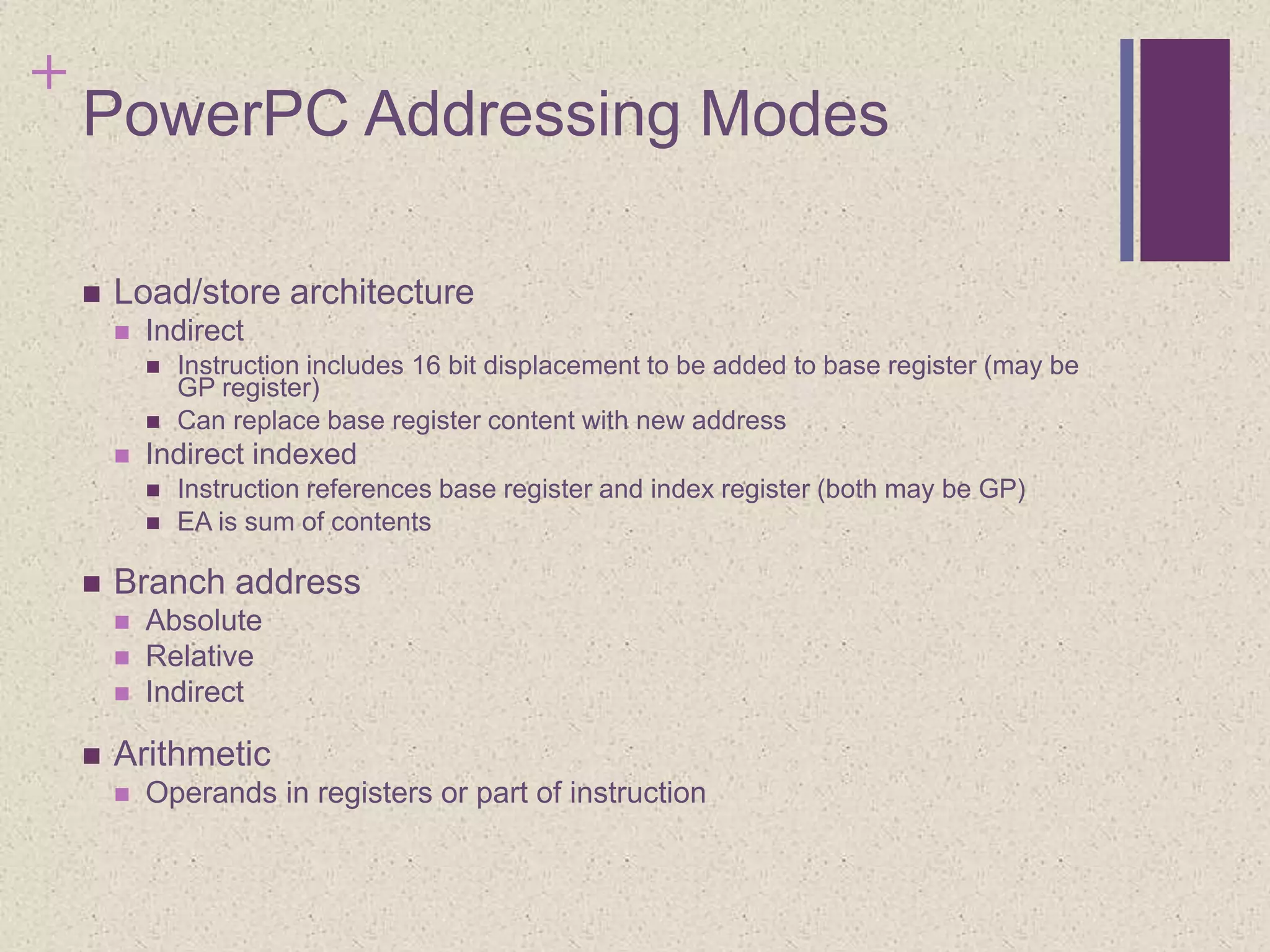

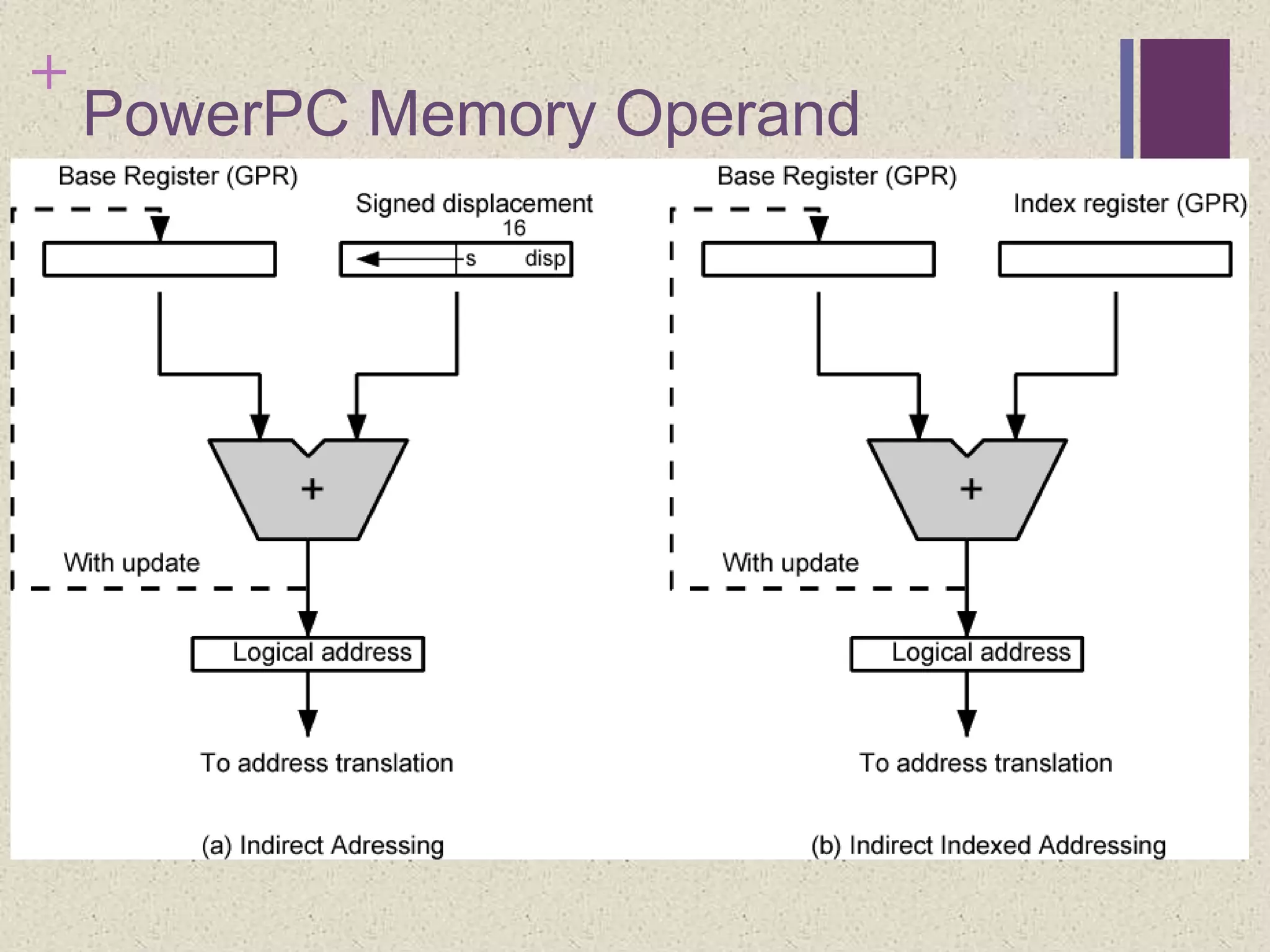

The document discusses various addressing modes used in computer architecture, including immediate, direct, indirect, register, and displacement addressing. It highlights the differences between Complex Instruction Set Computer (CISC) and Reduced Instruction Set Computer (RISC) addressing strategies, emphasizing the efficiency and flexibility of addressing modes for access and instruction execution. Additionally, it covers specific addressing modes used in Pentium and PowerPC architectures, detailing the mechanics and applications of each mode.