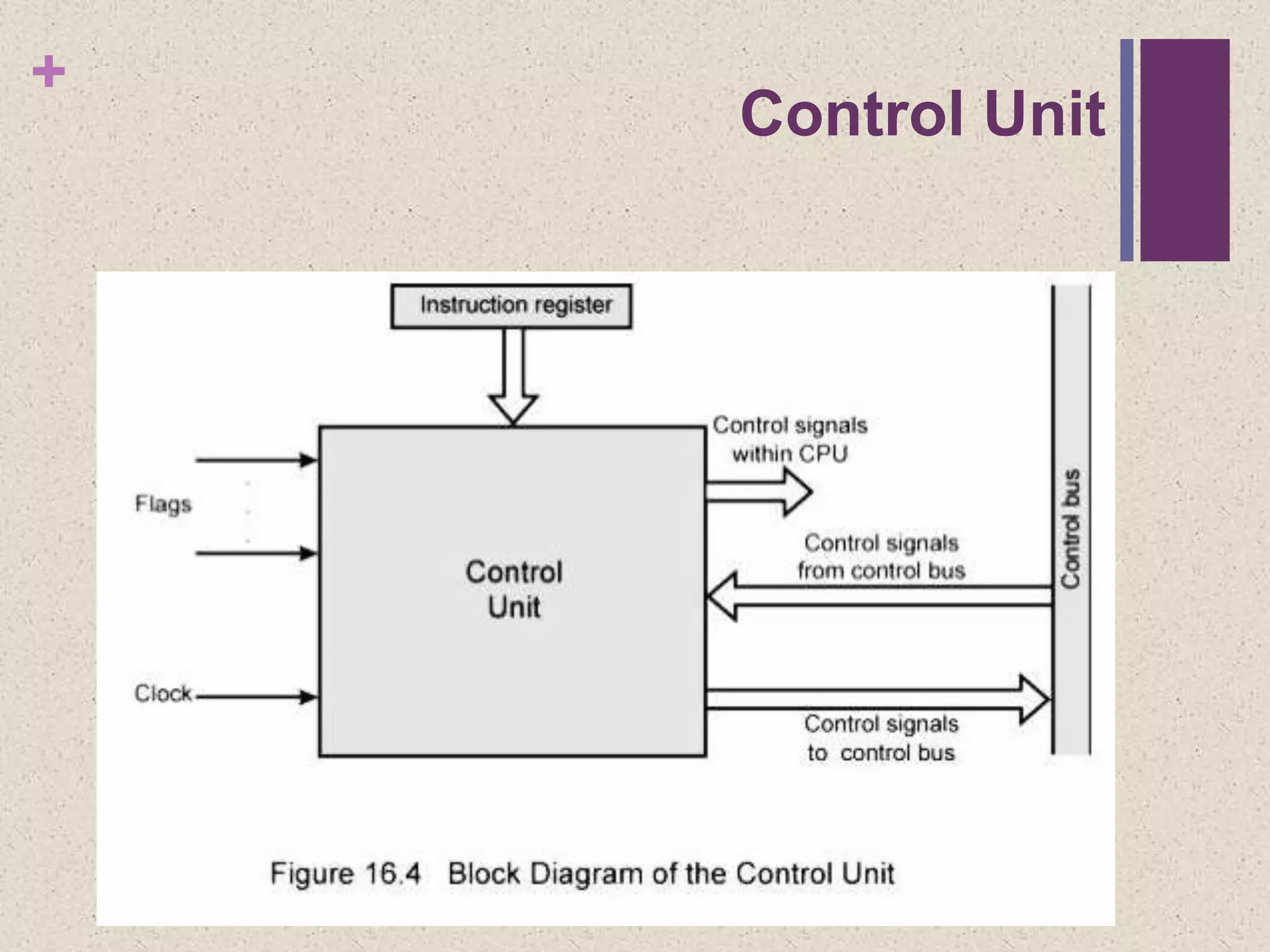

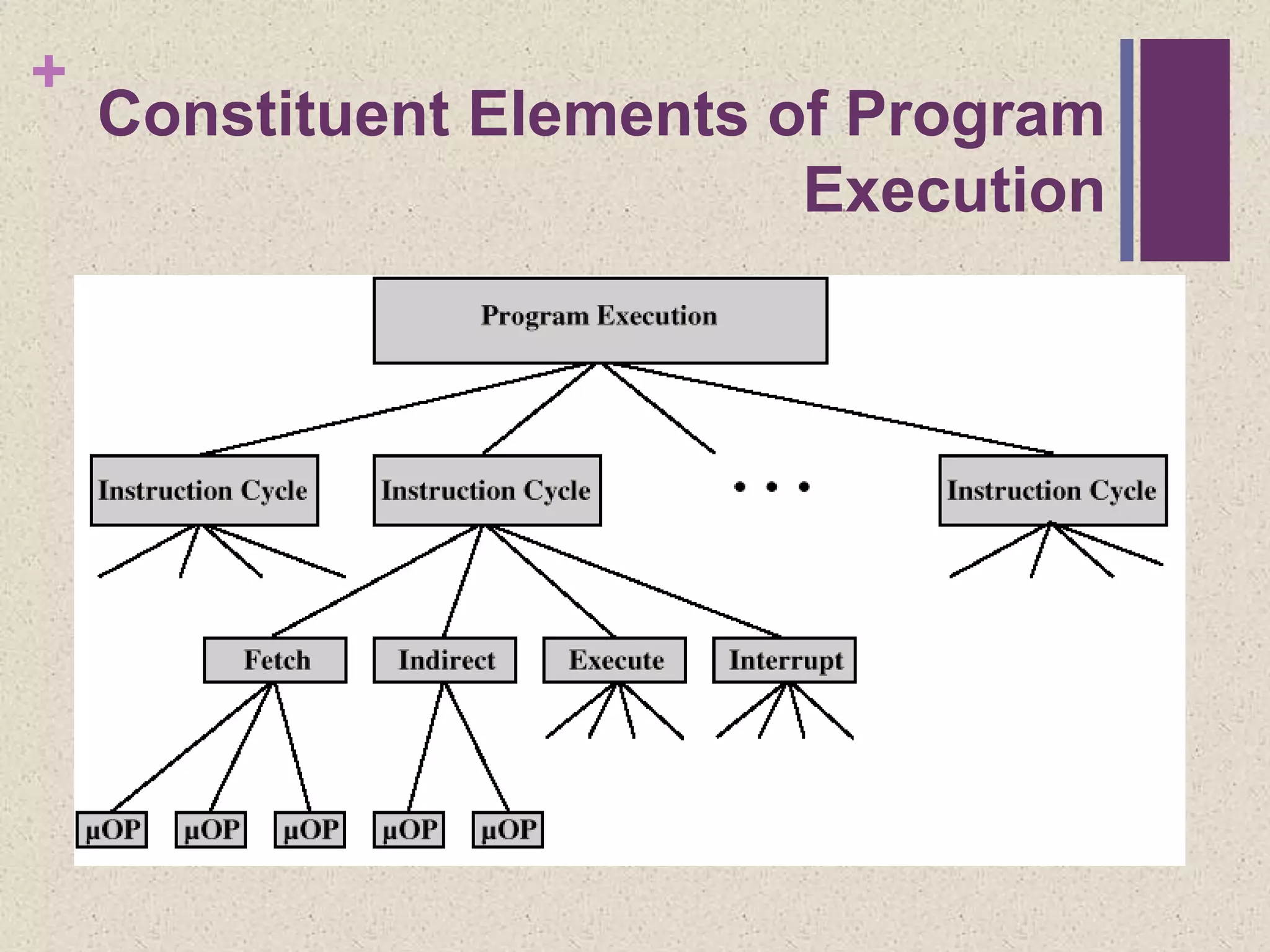

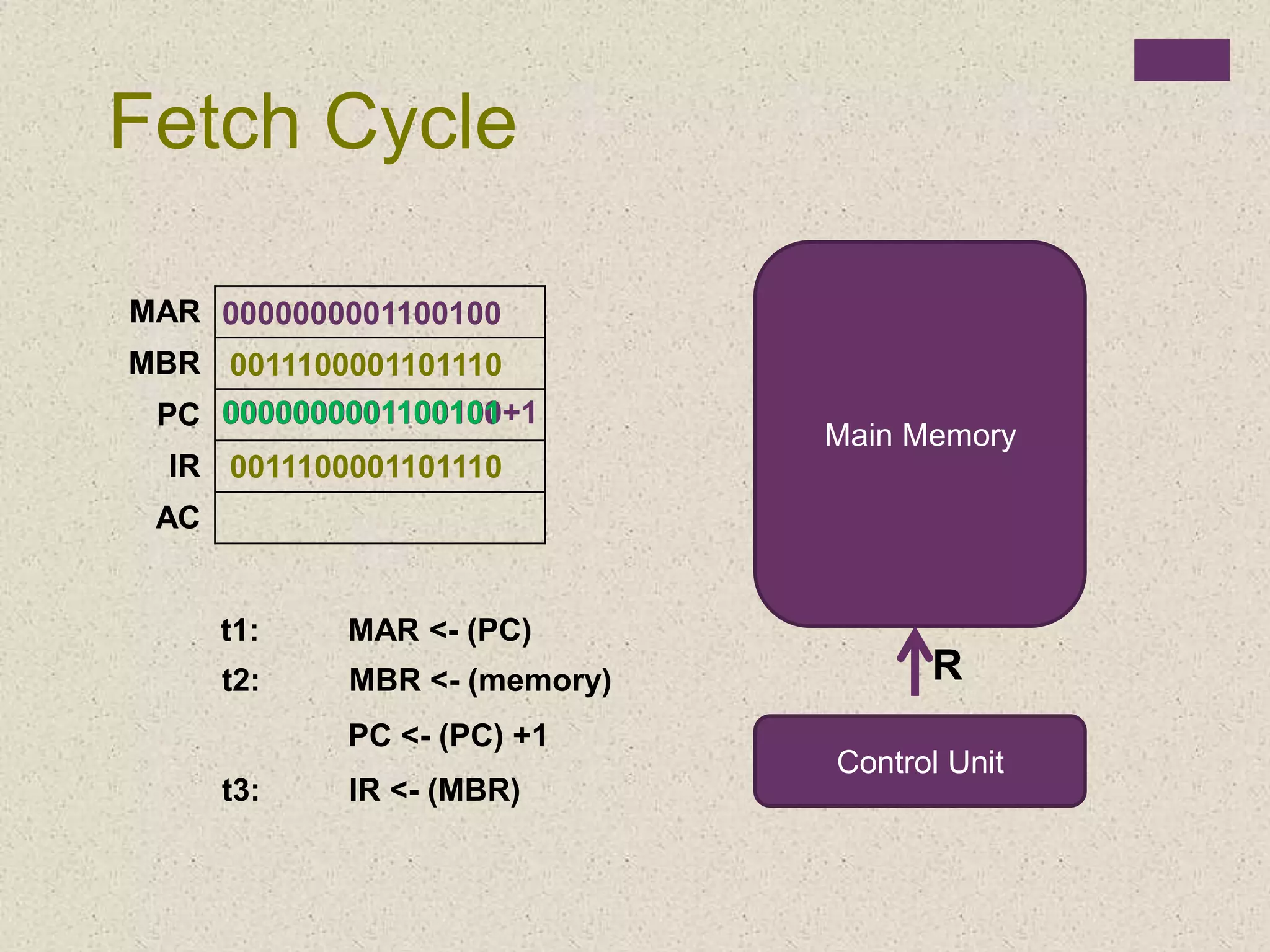

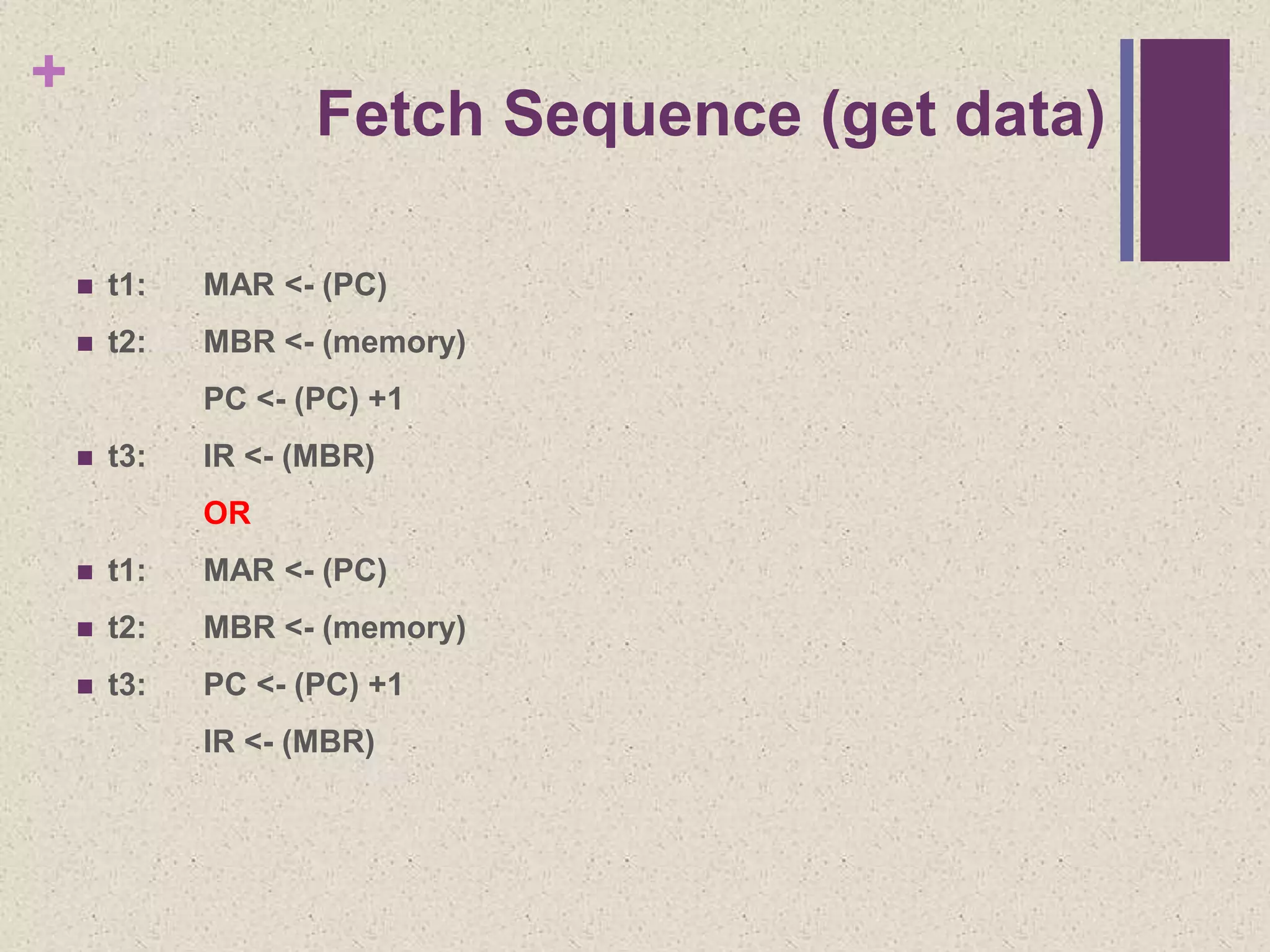

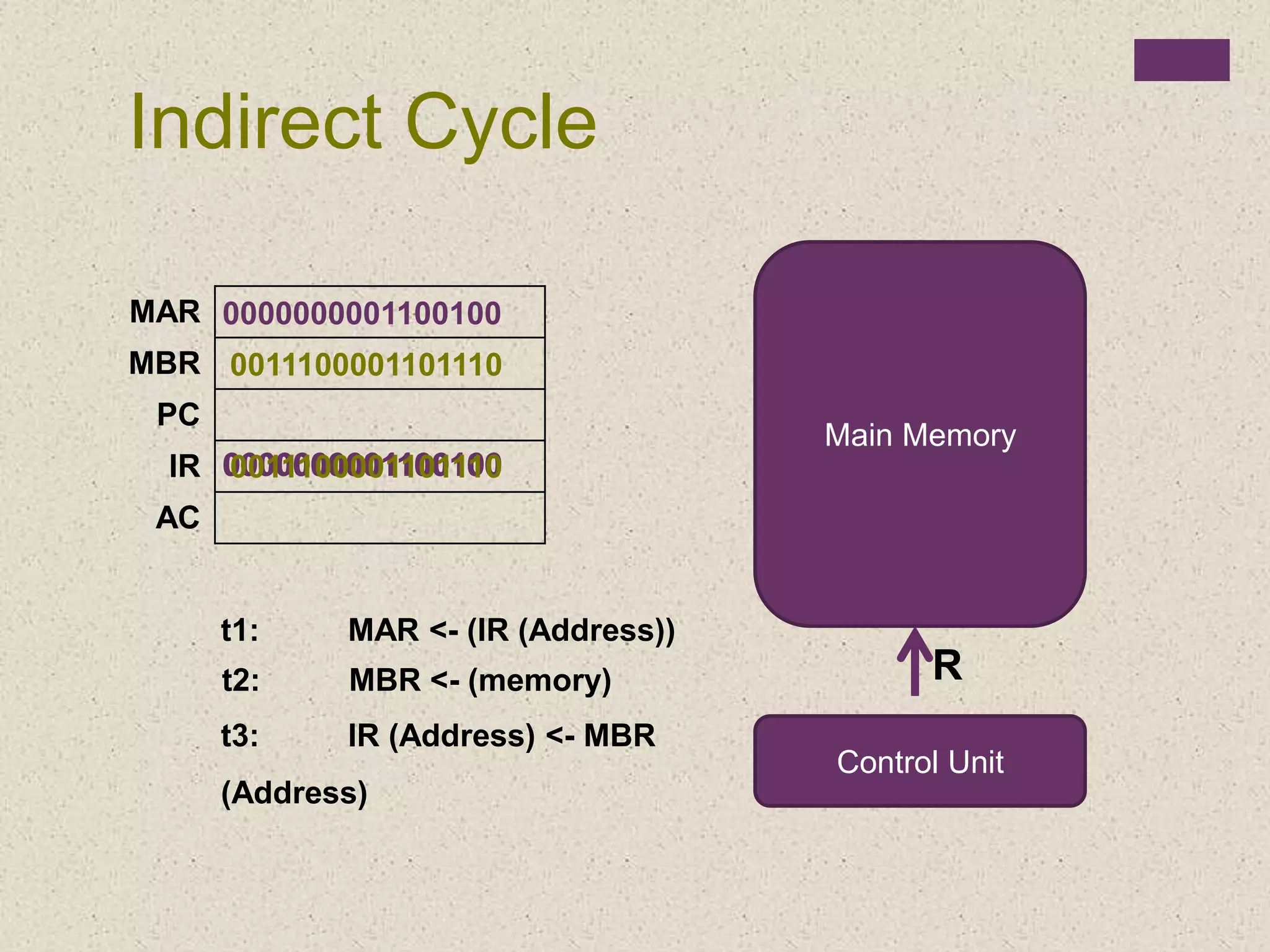

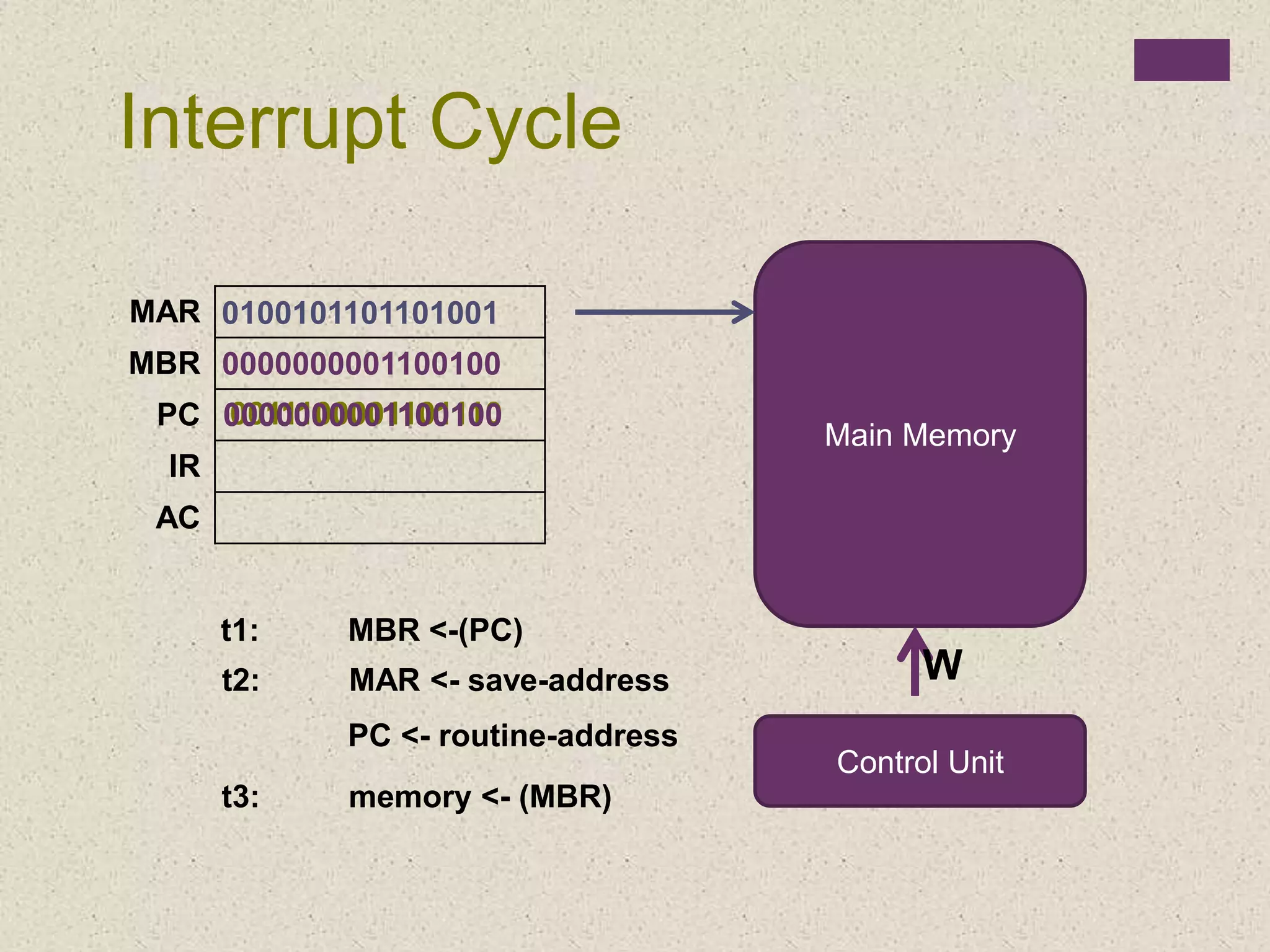

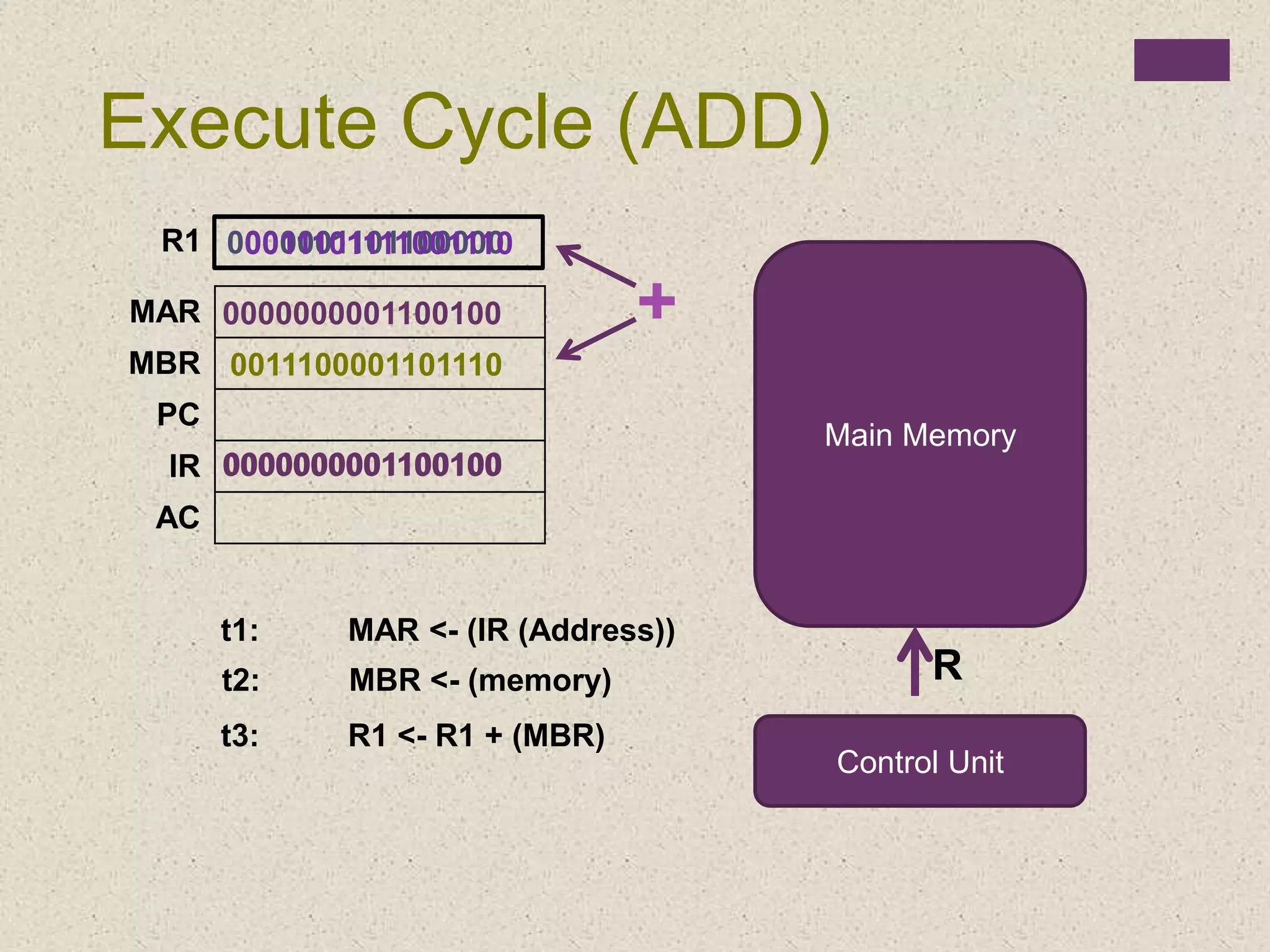

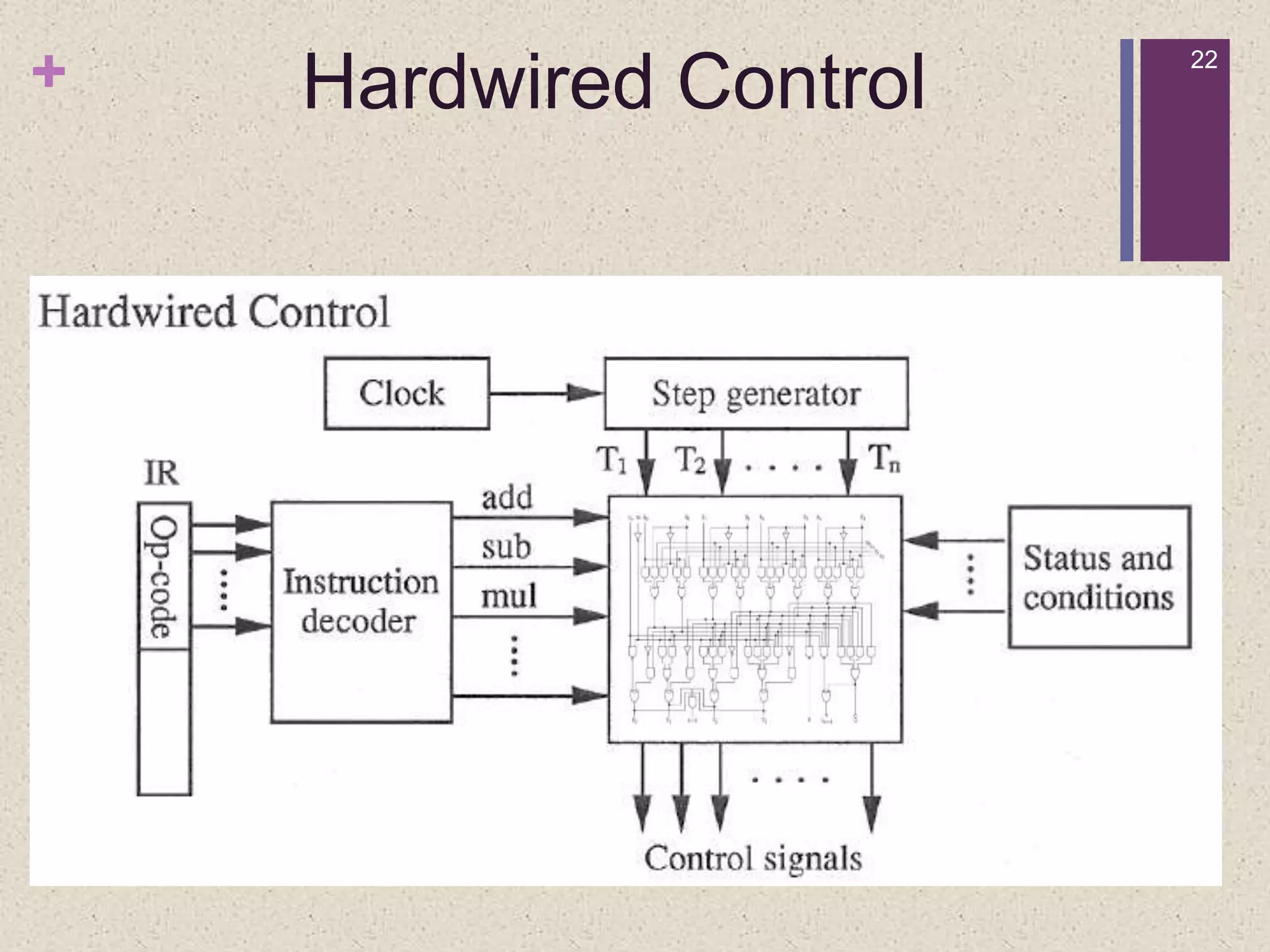

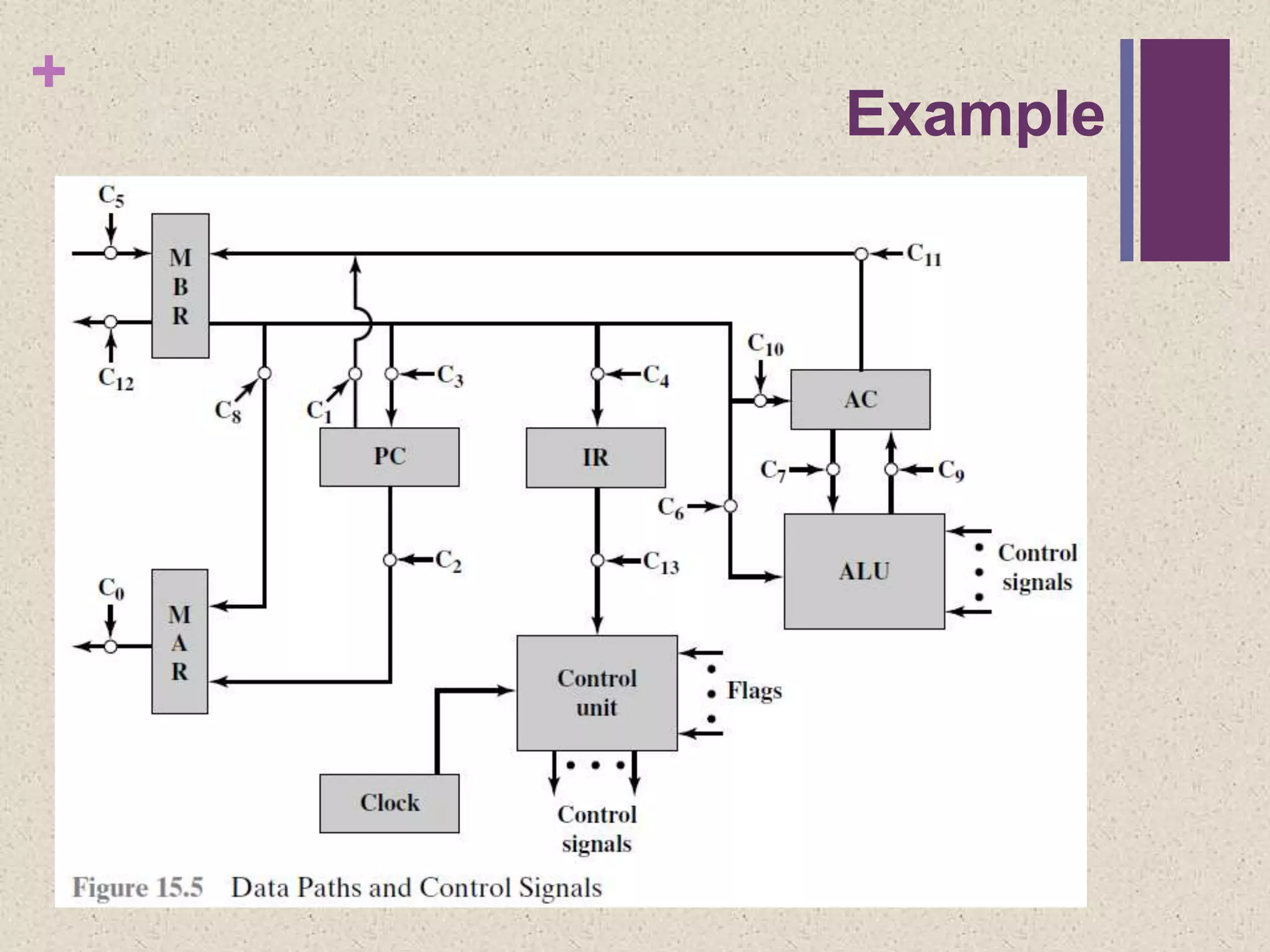

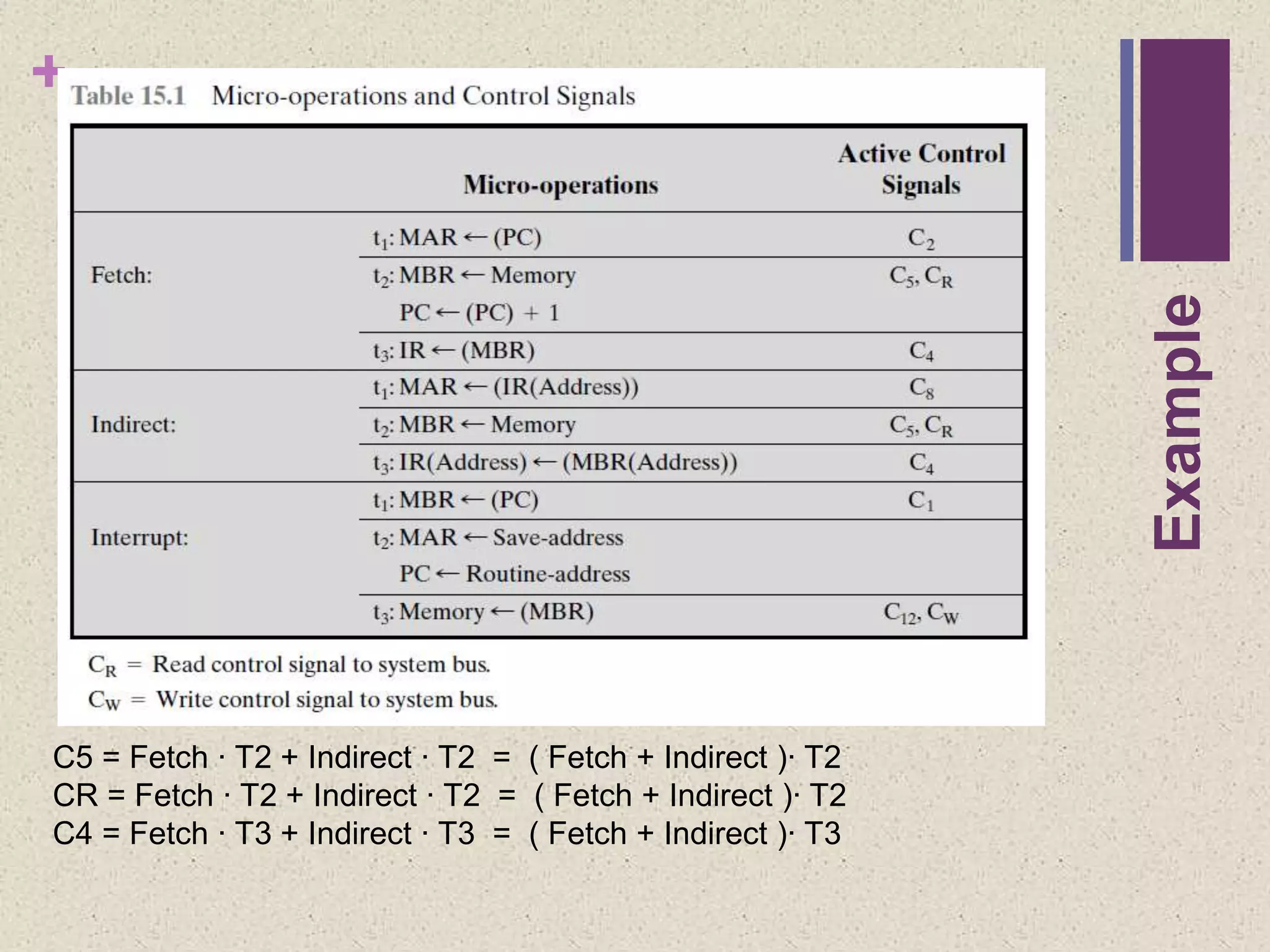

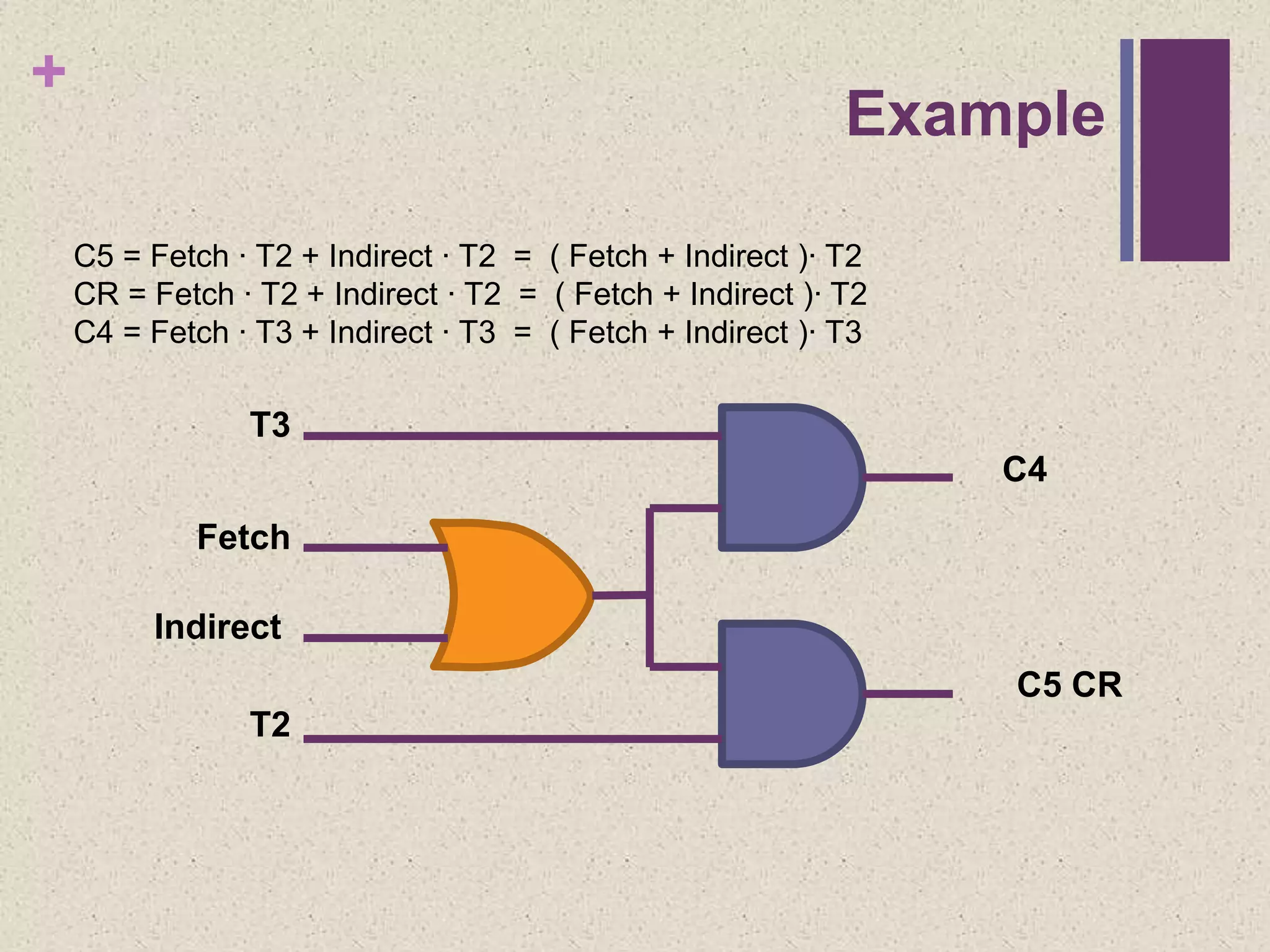

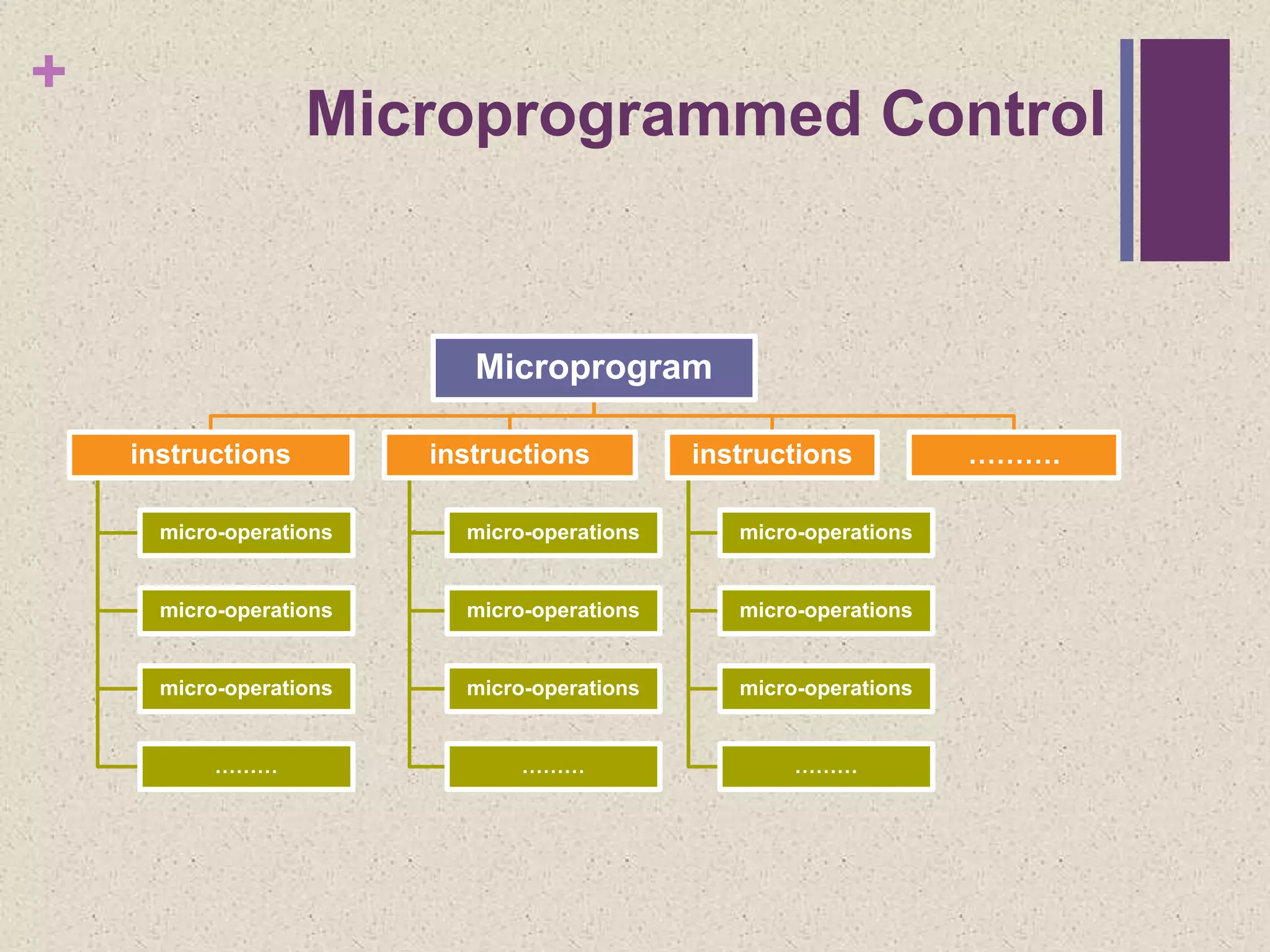

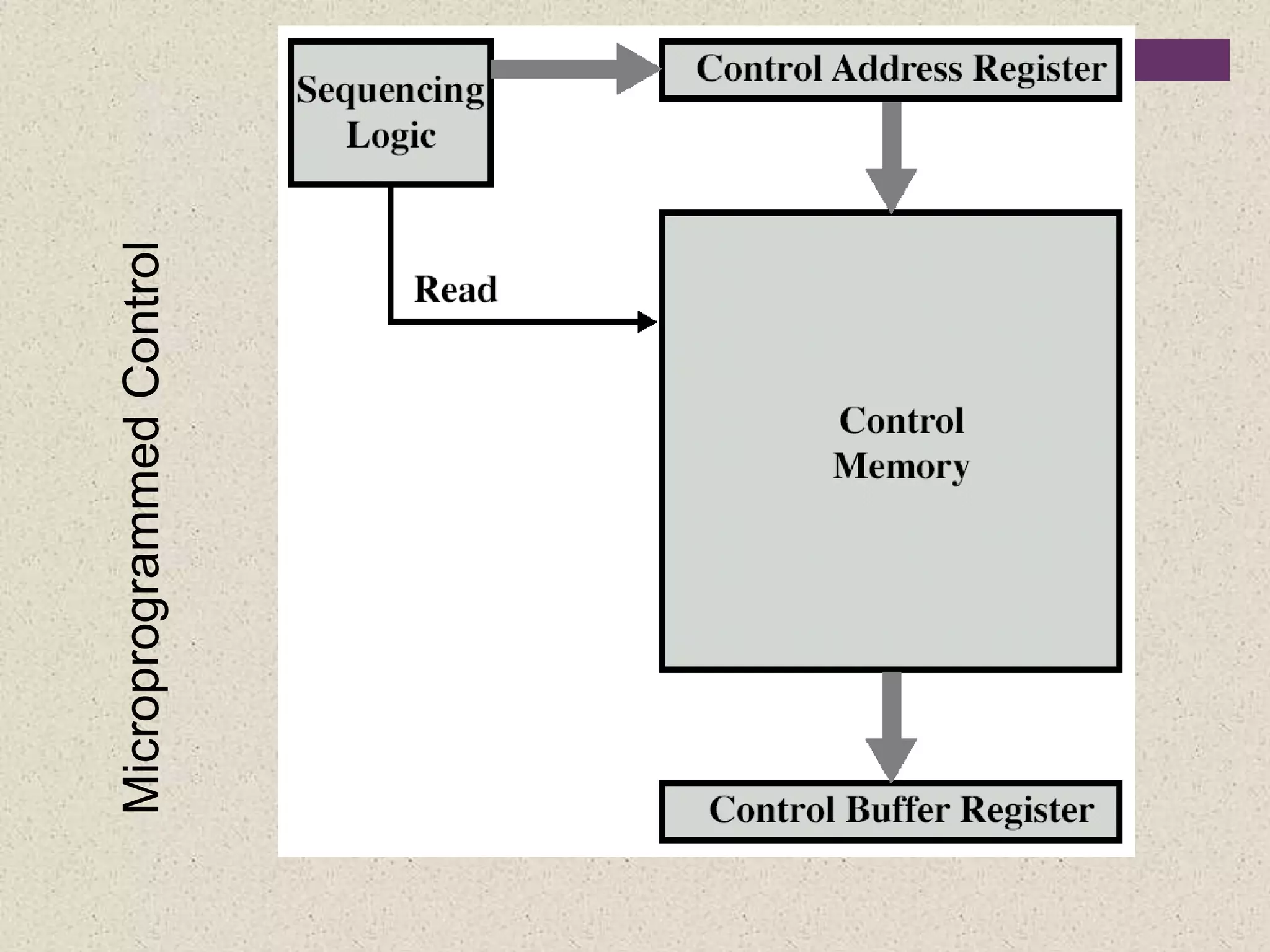

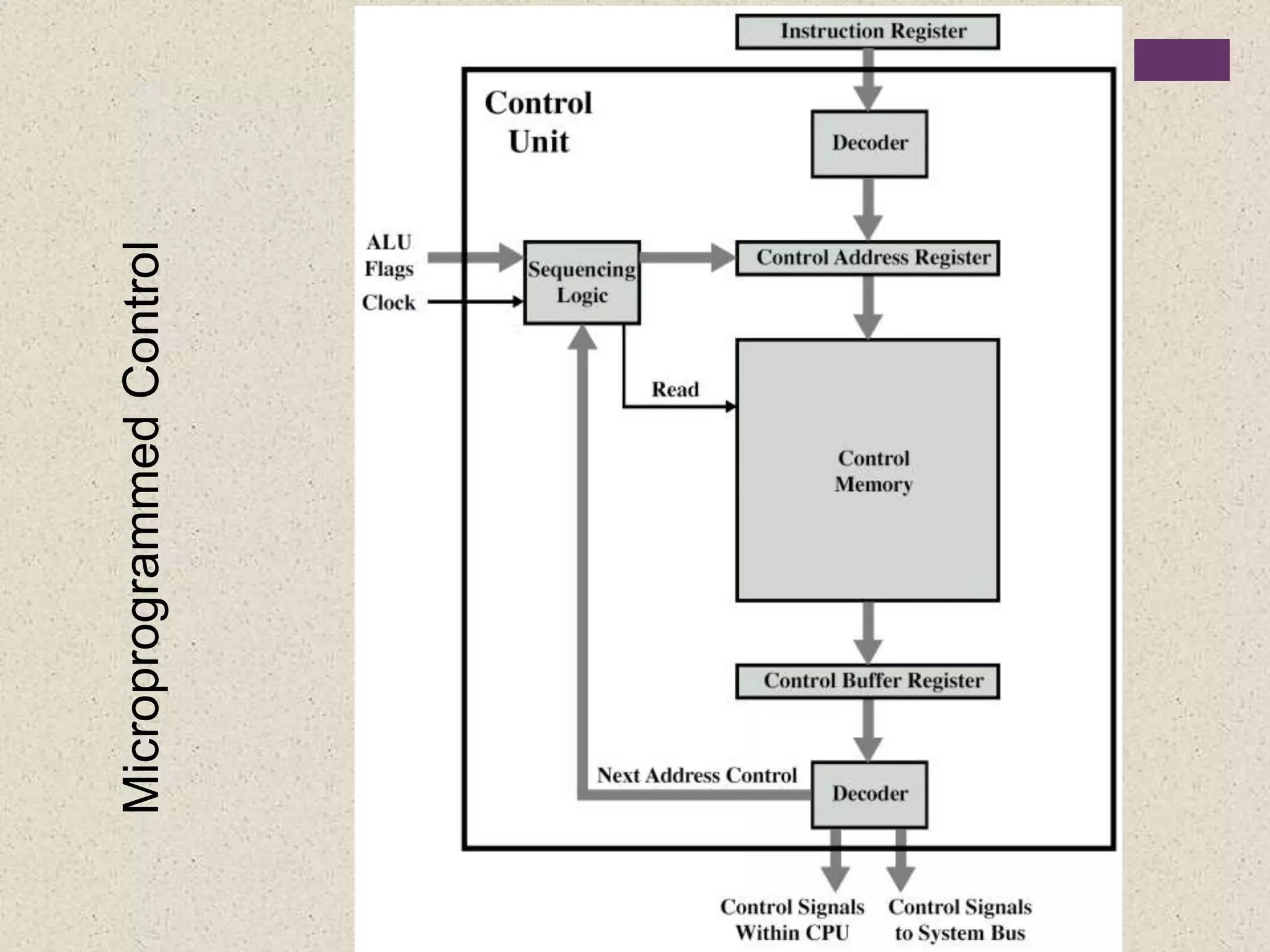

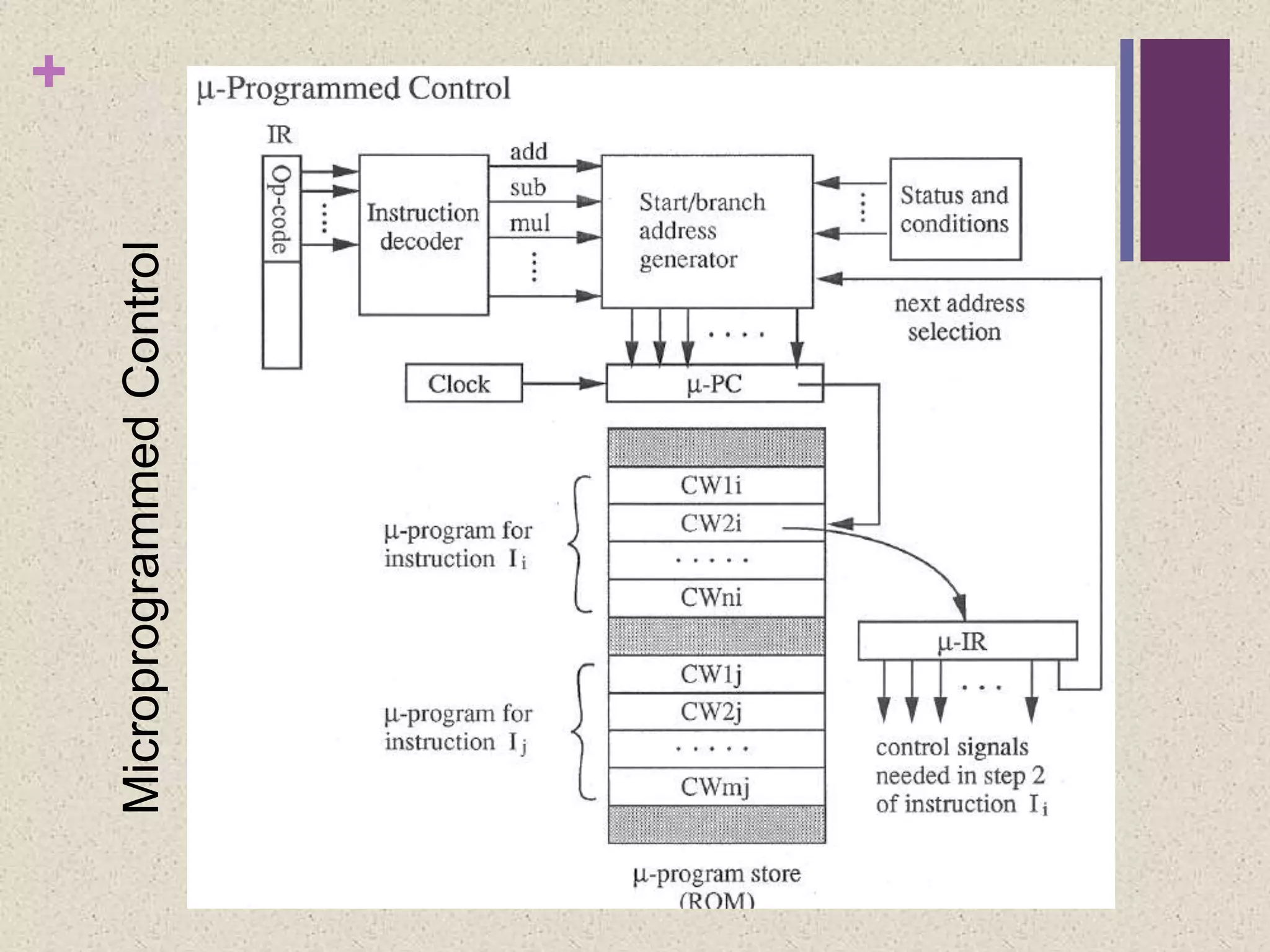

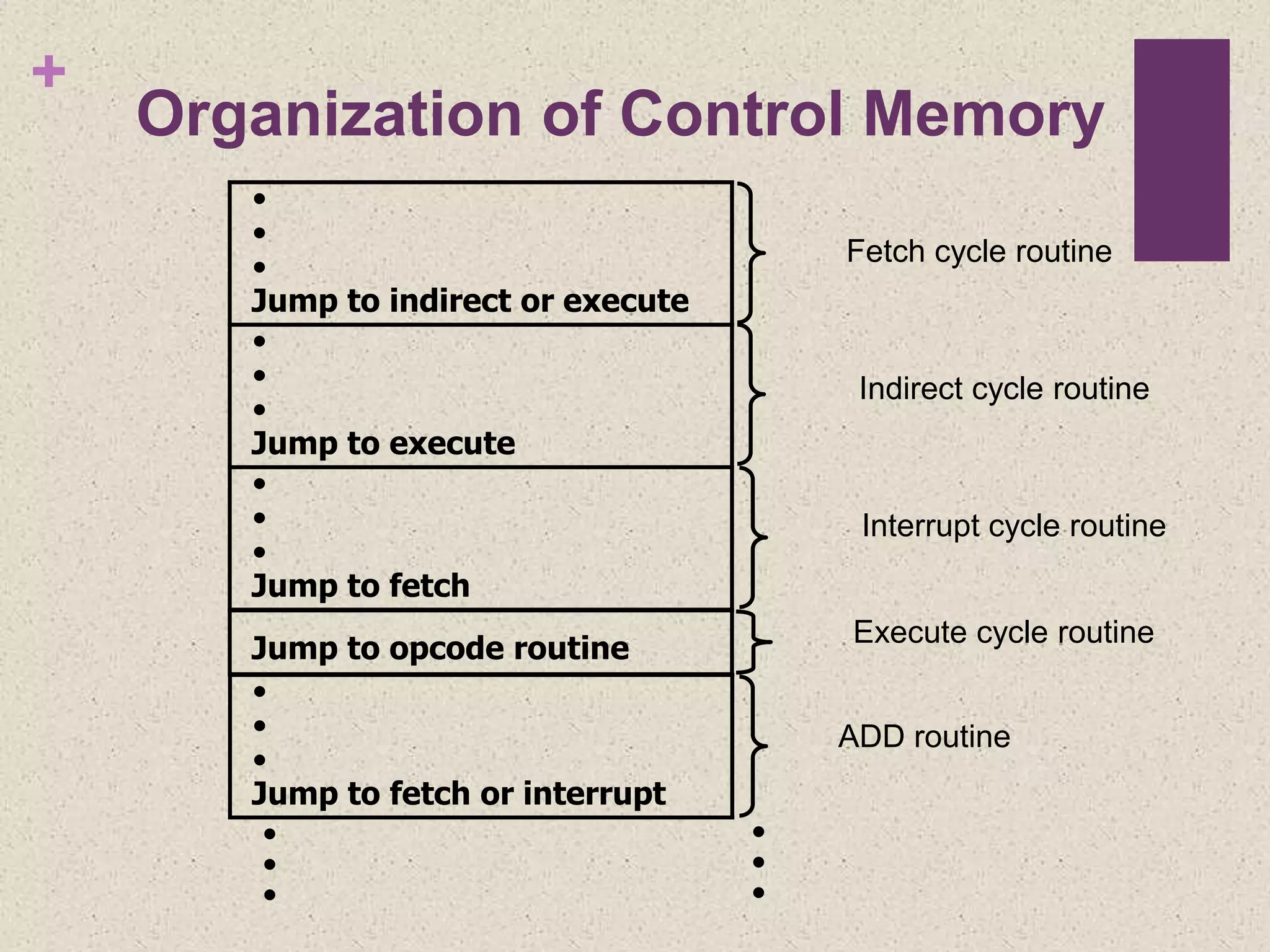

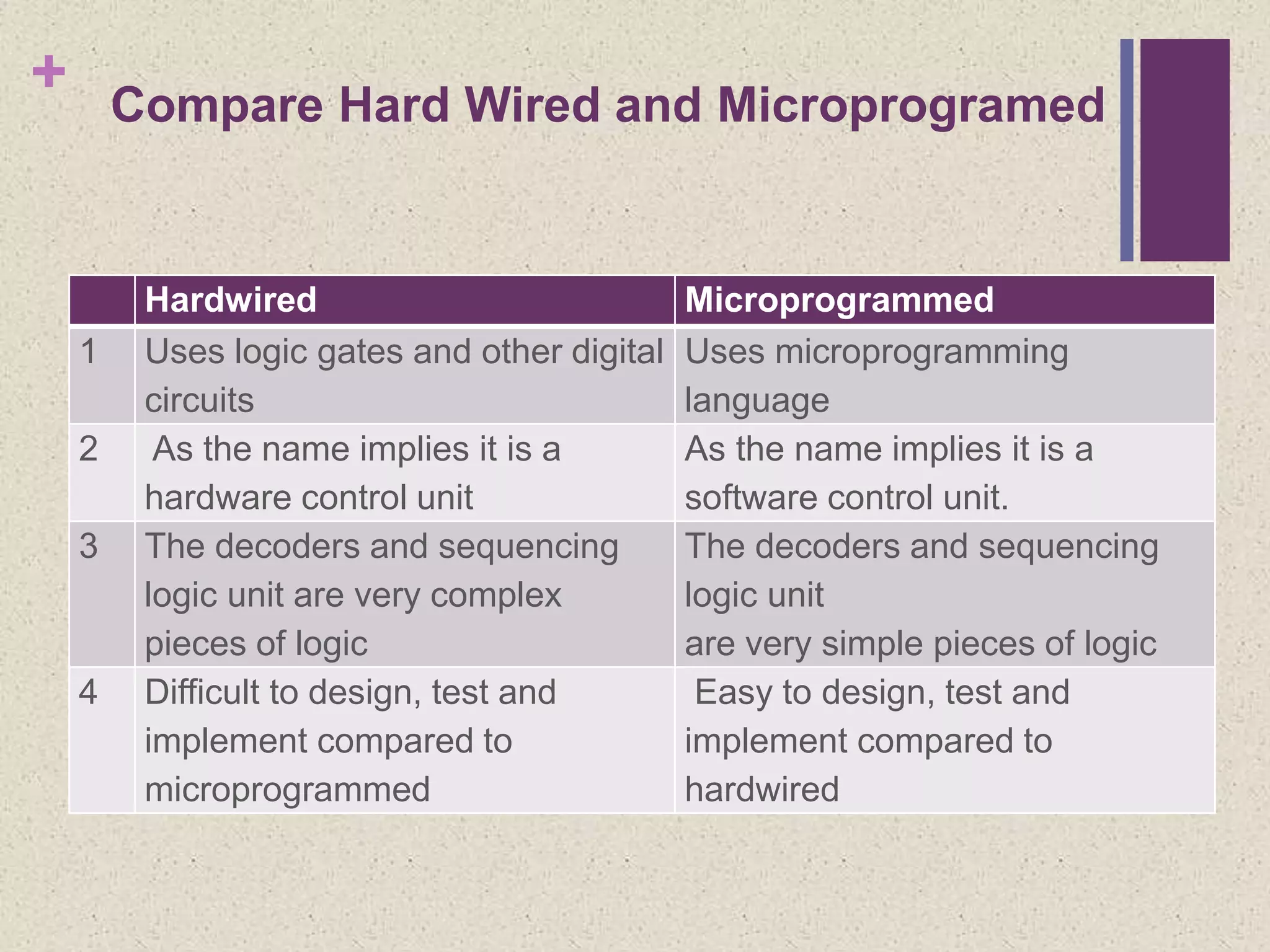

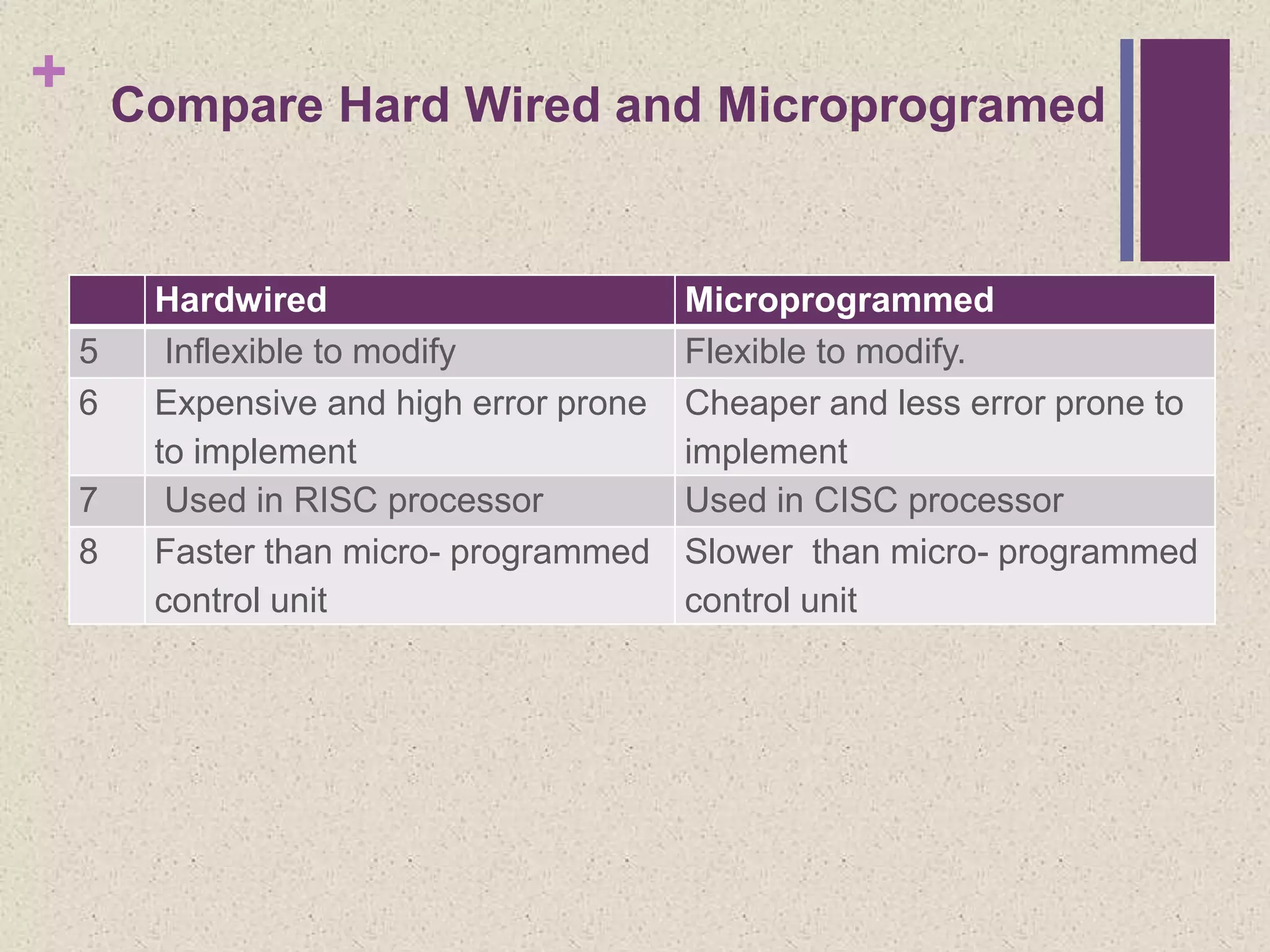

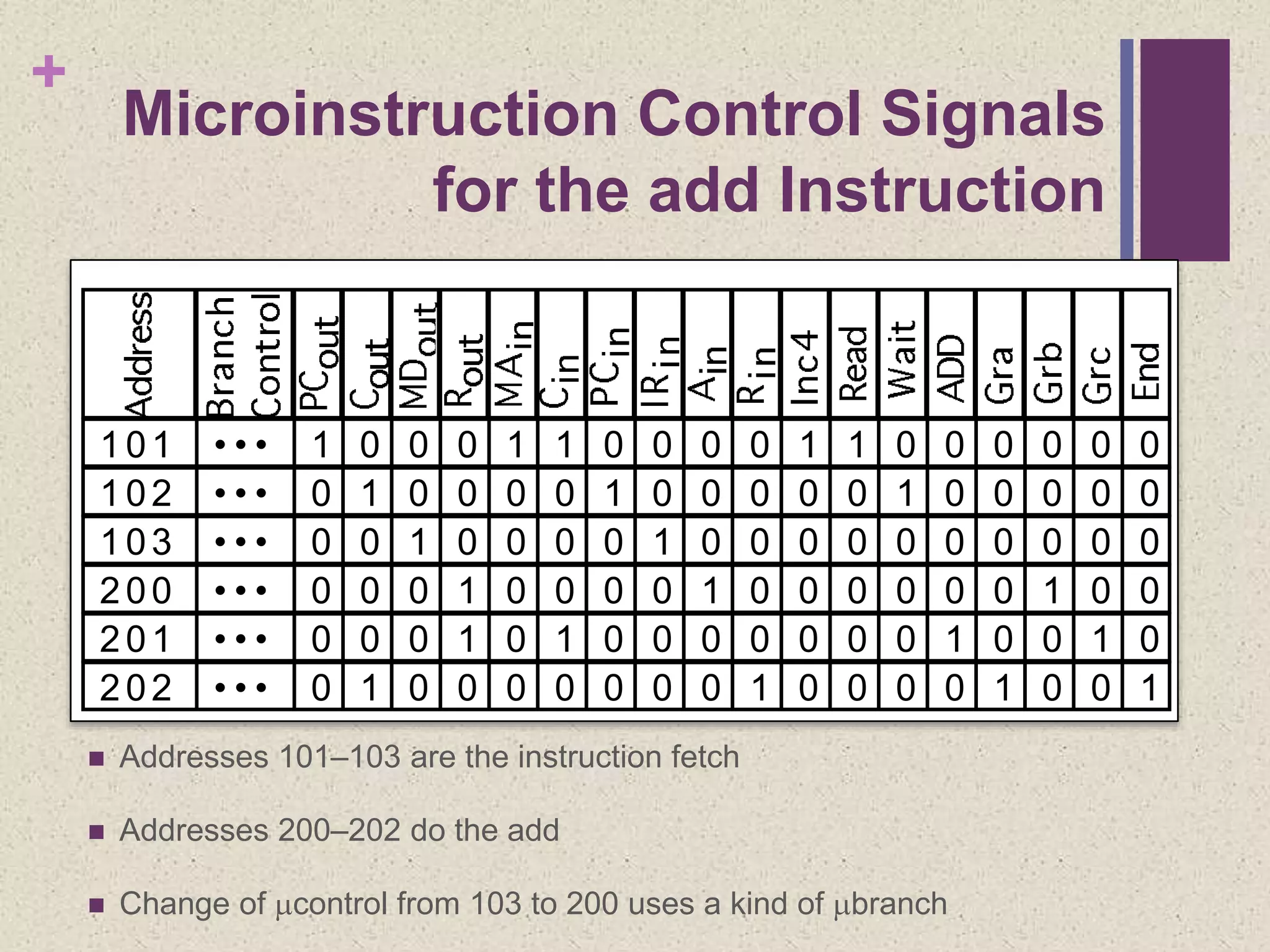

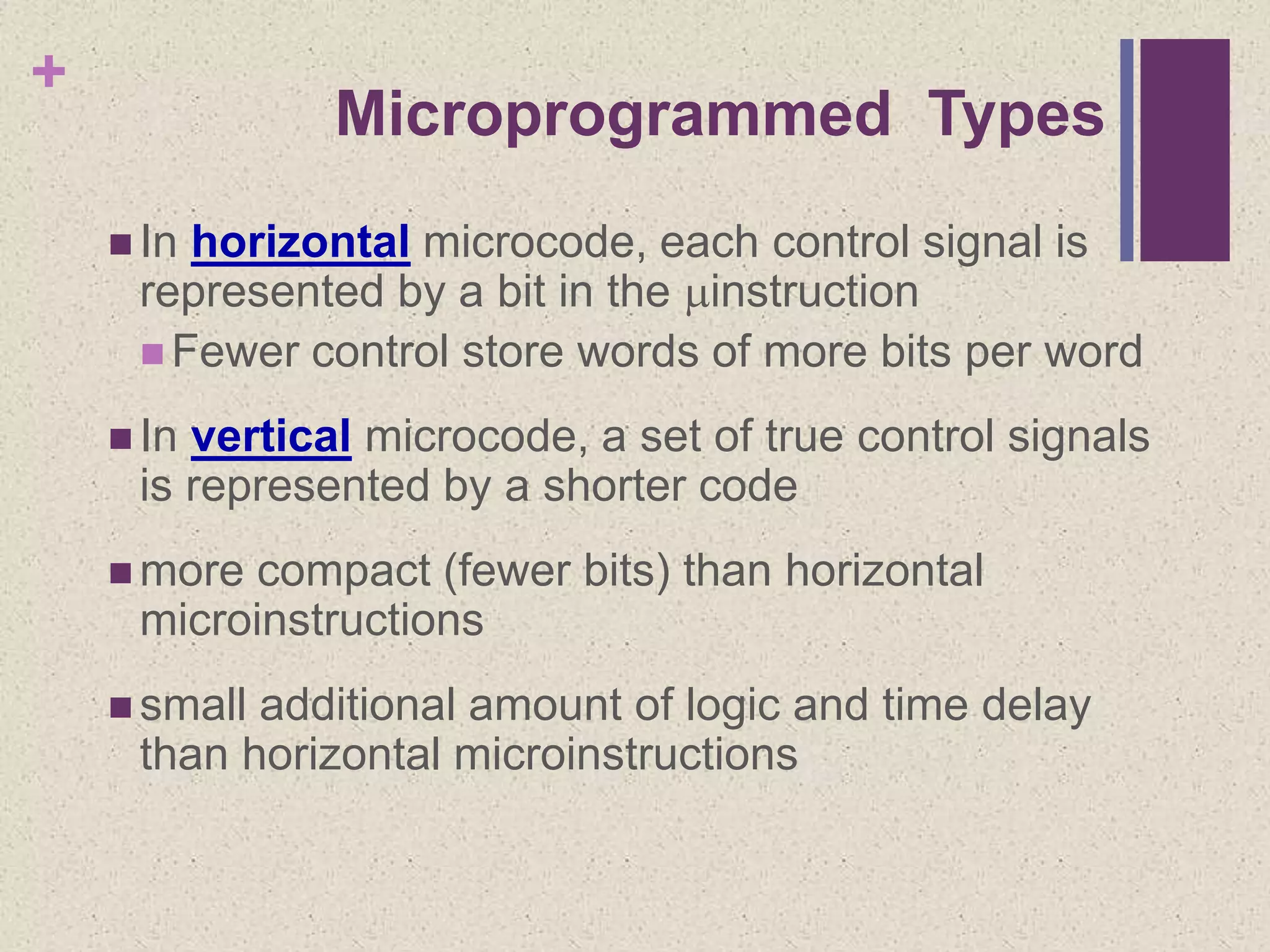

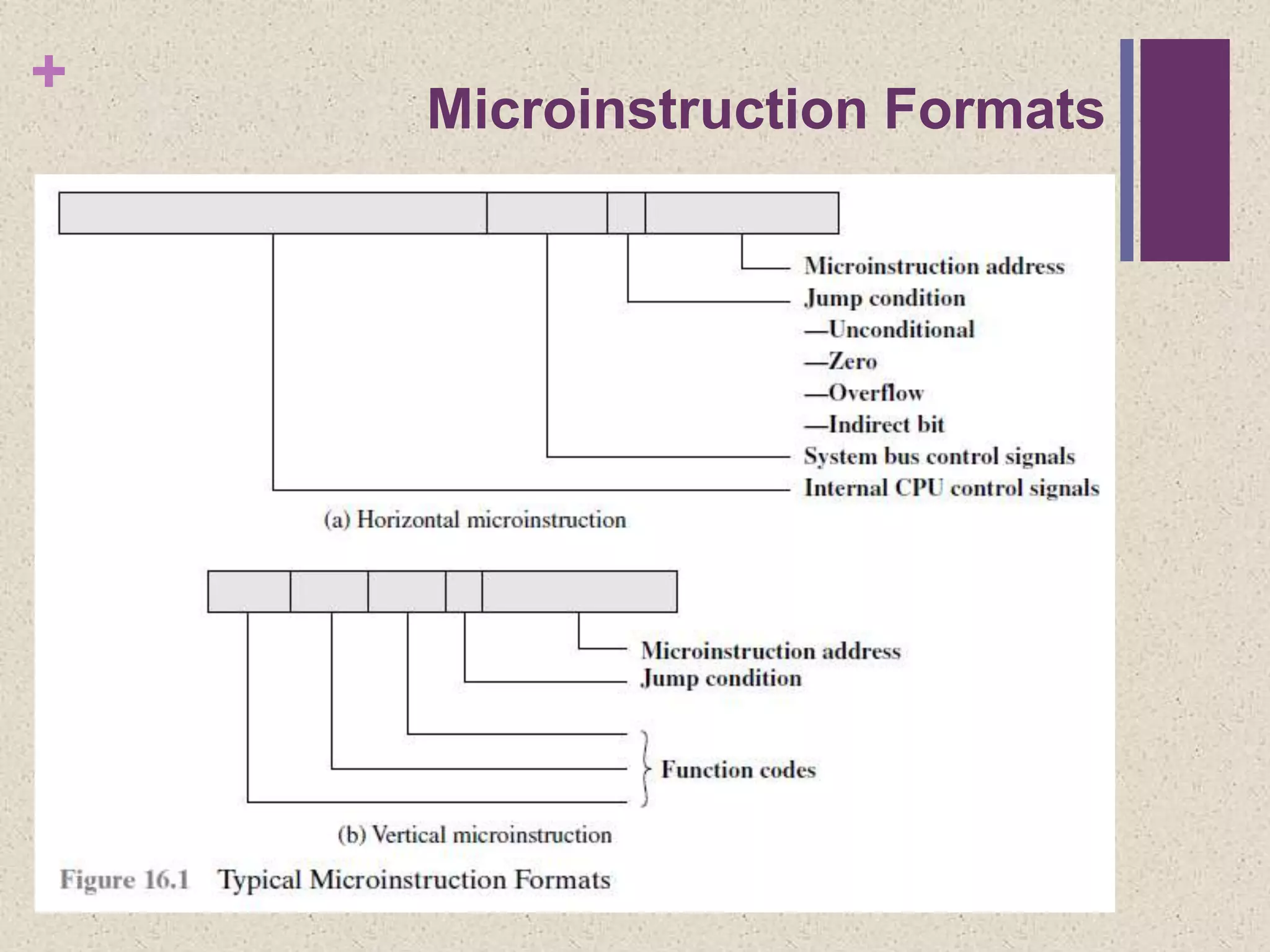

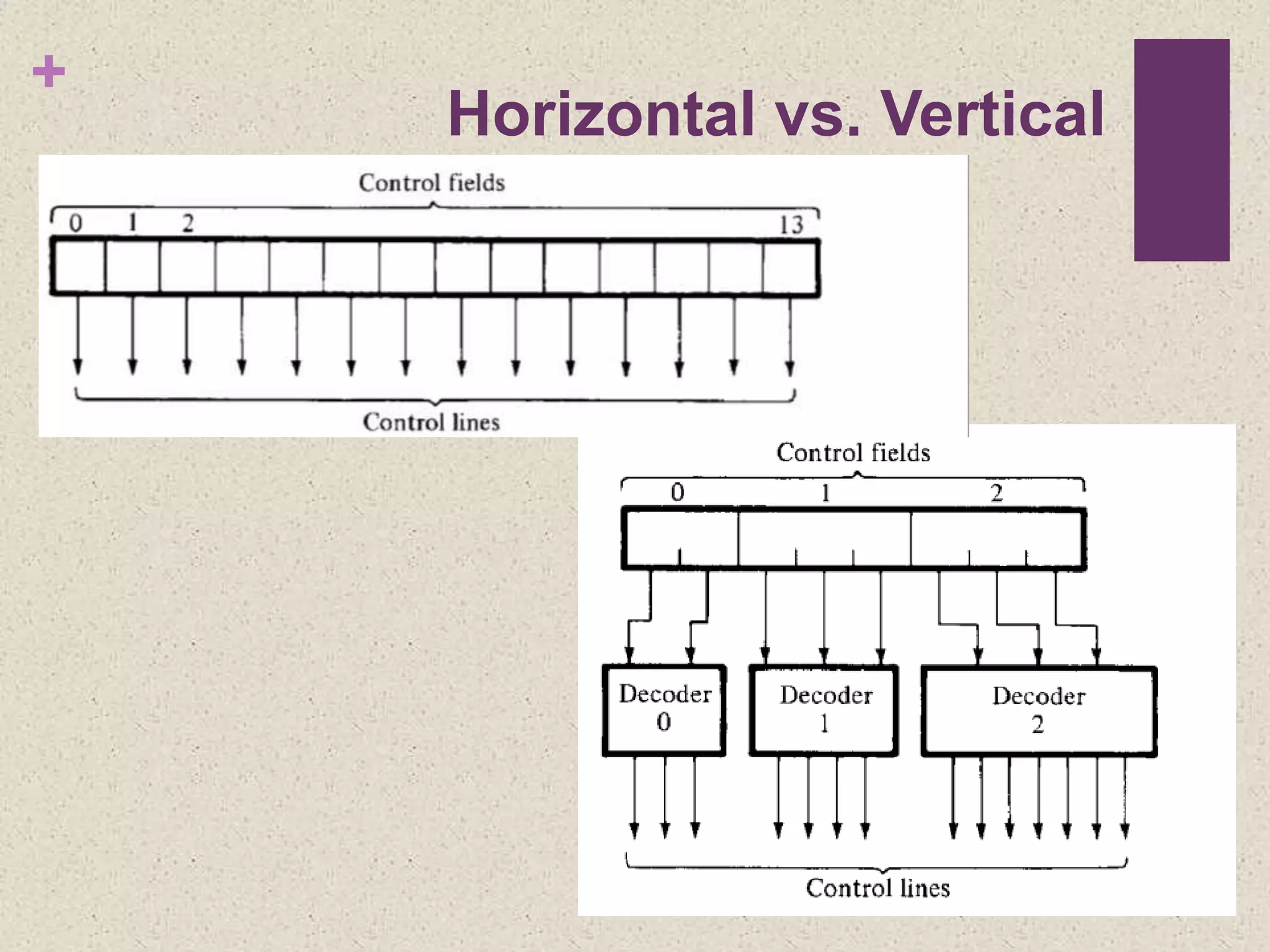

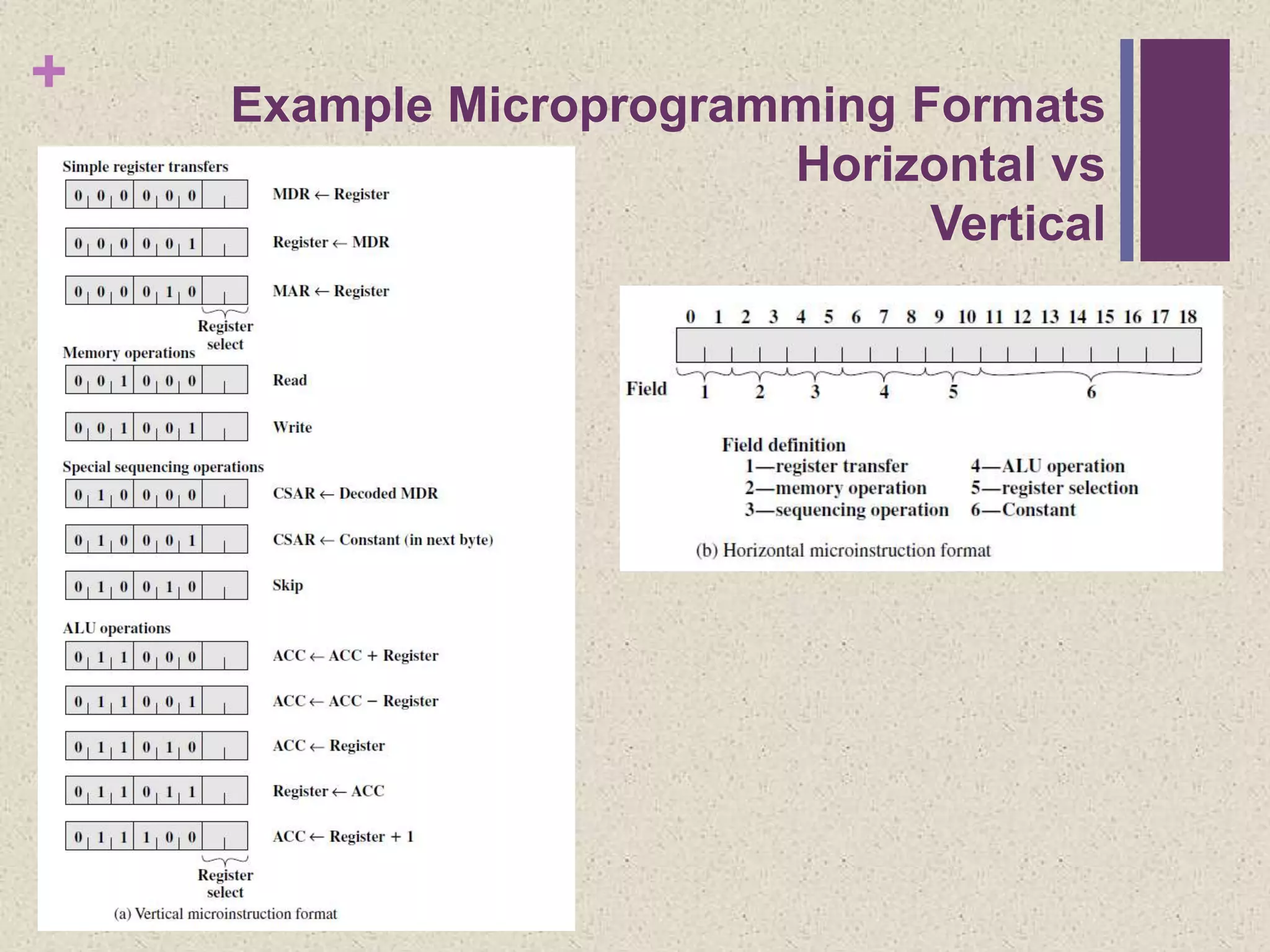

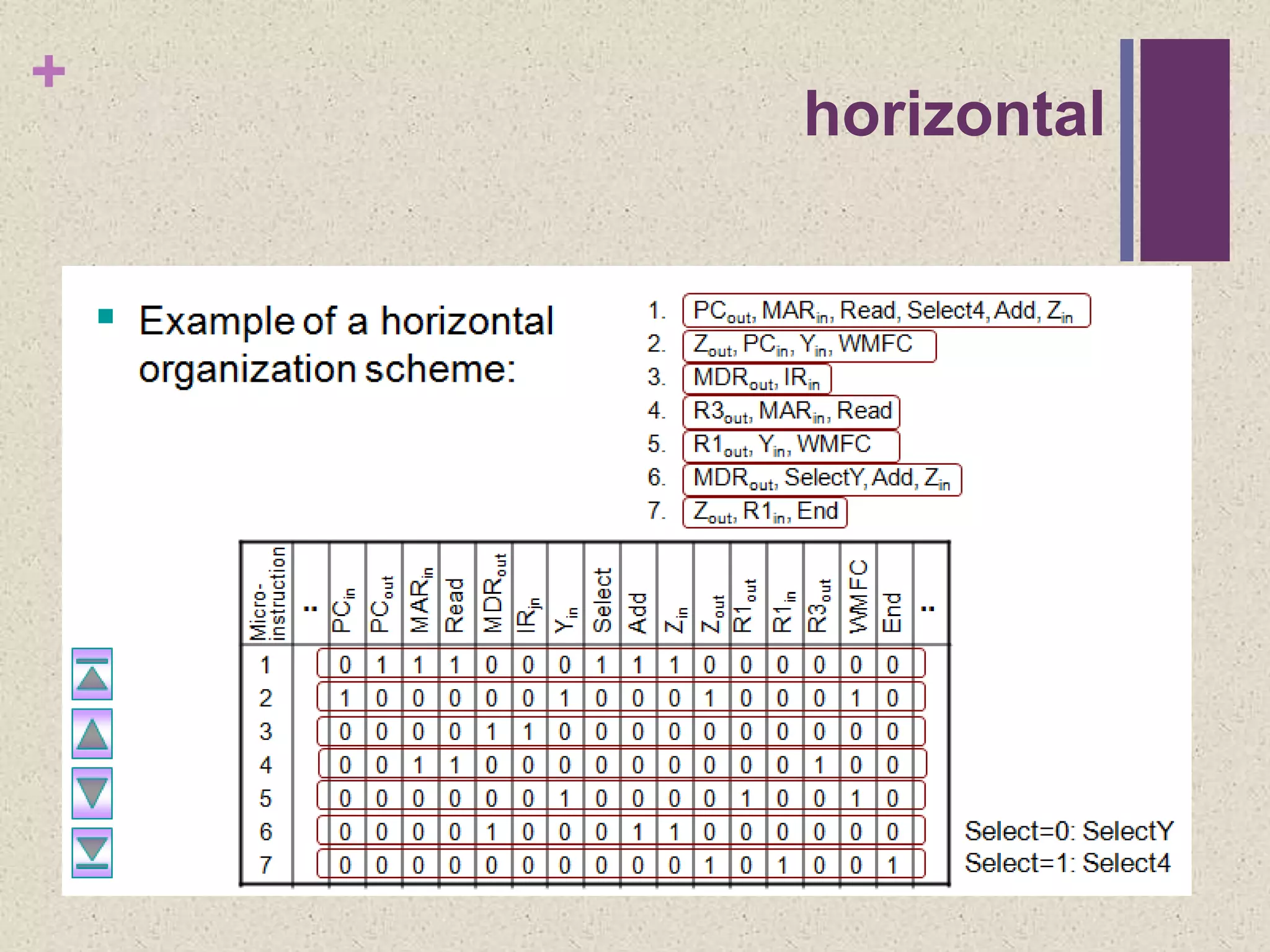

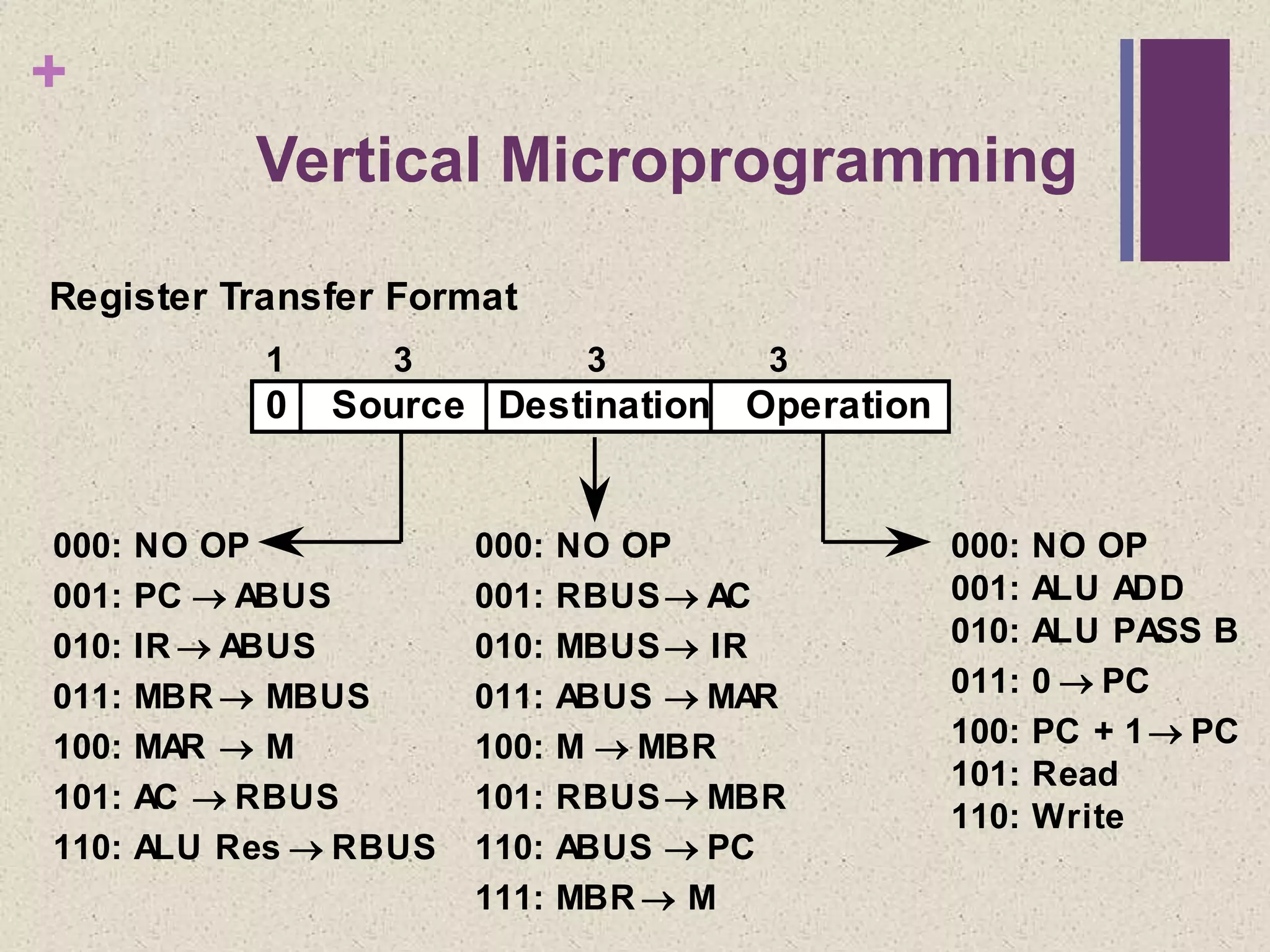

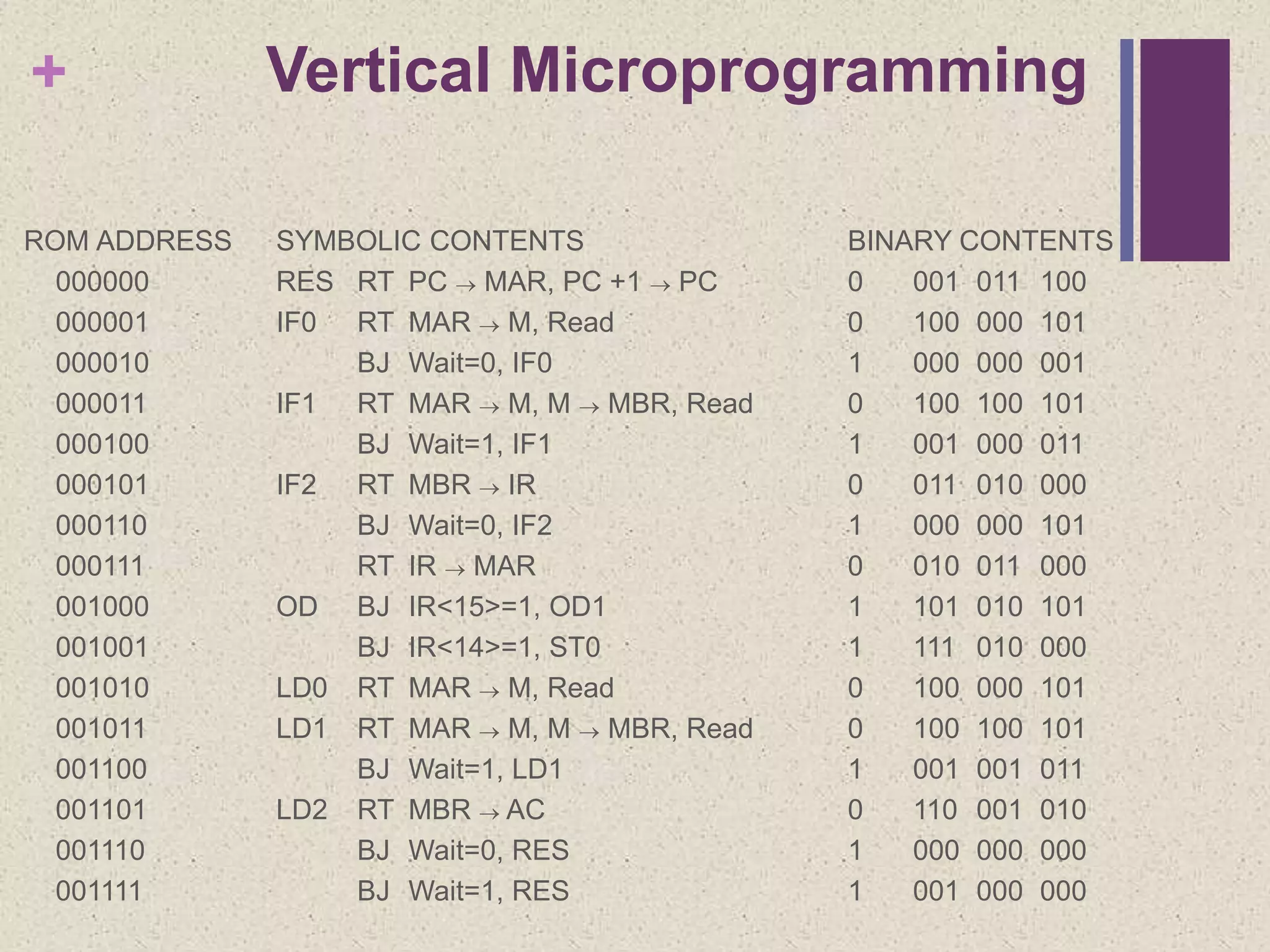

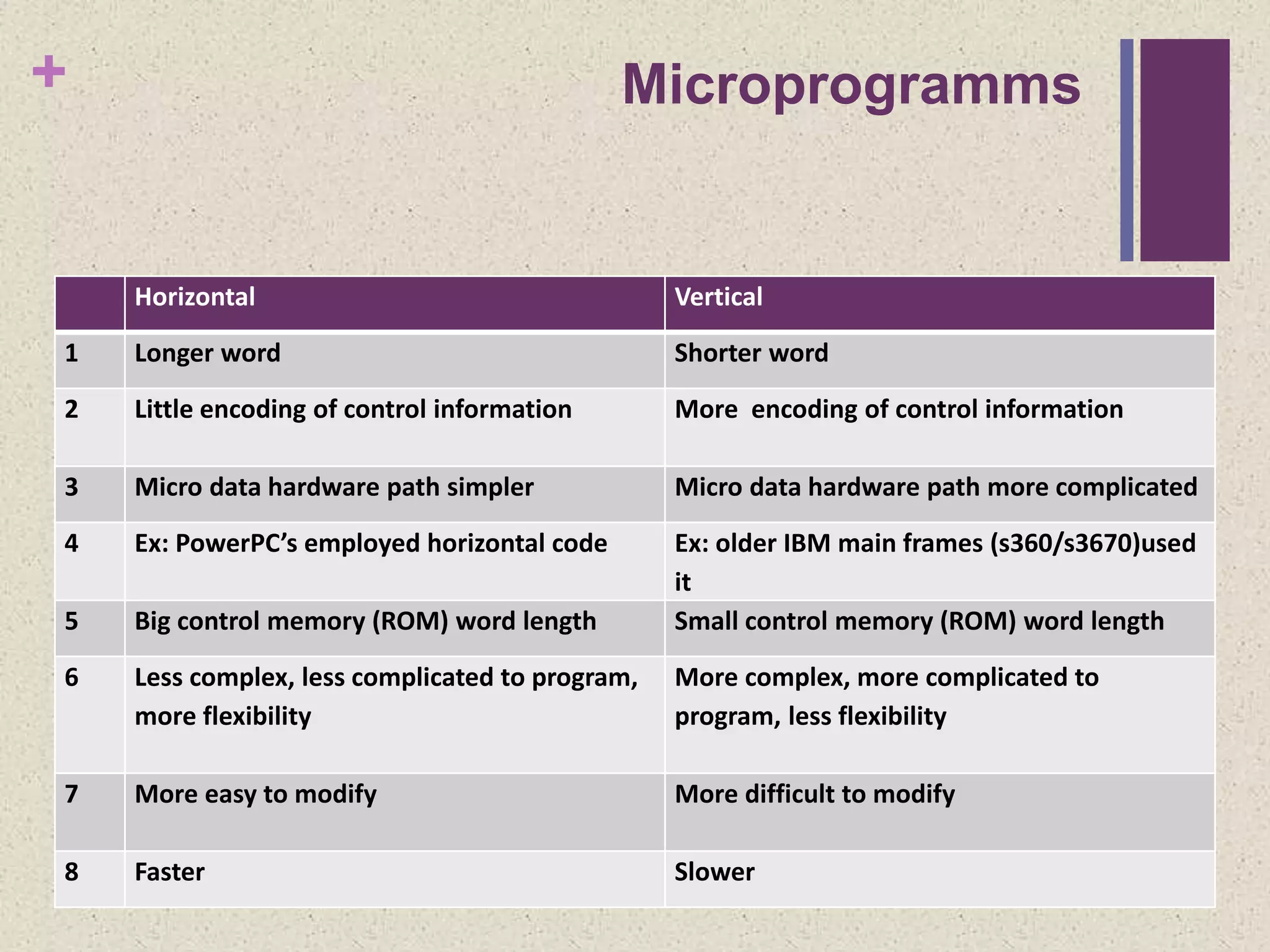

The document outlines the architecture and functionality of a computer's control unit, detailing its role in executing instructions through control signals and cycles. It discusses different types of control unit implementations, such as hardwired and microprogrammed control, and compares their characteristics. Additionally, it covers the control registers, the fetch sequence, and various cycles like indirect and interrupt cycles that are integral to program execution.