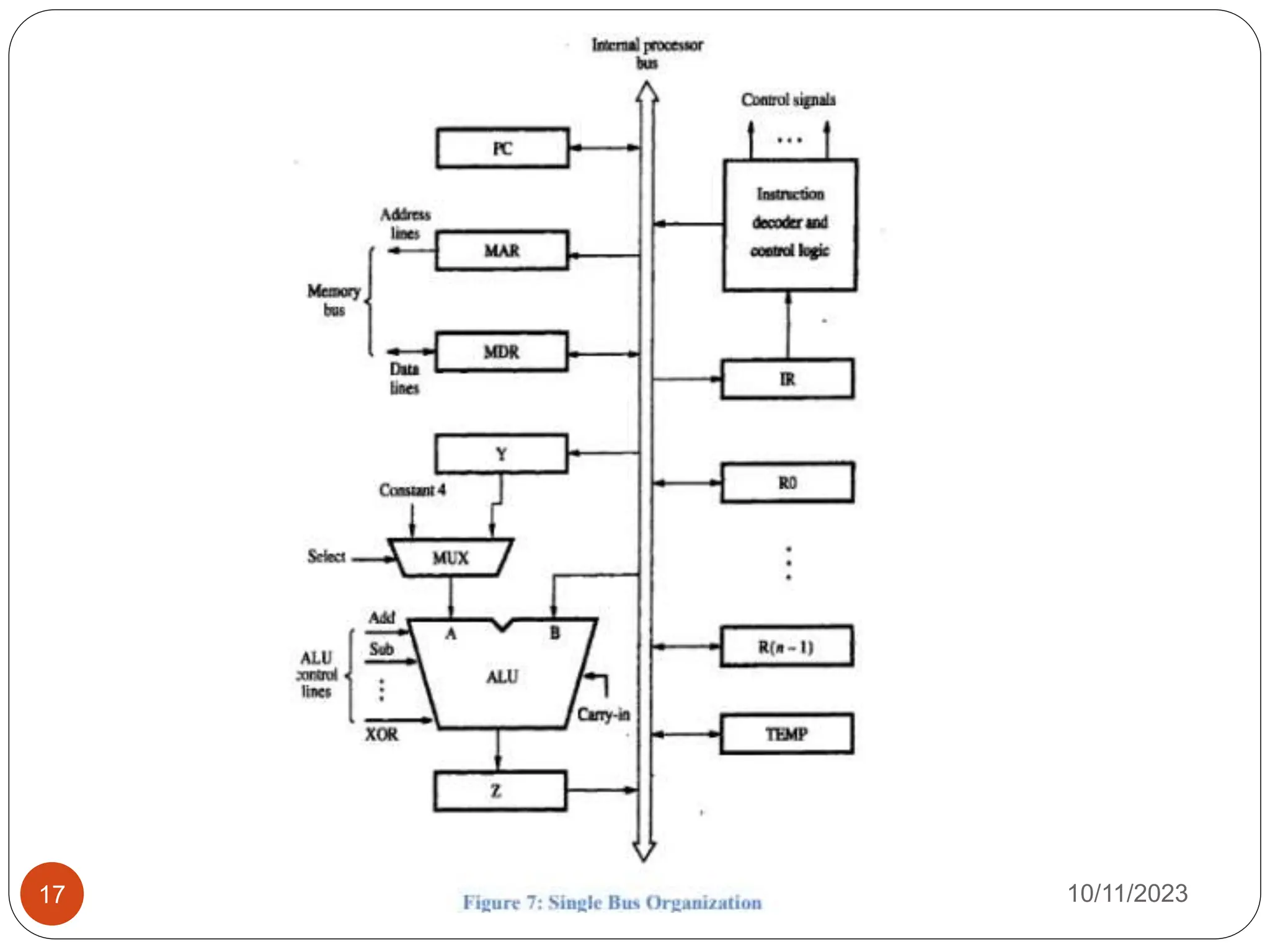

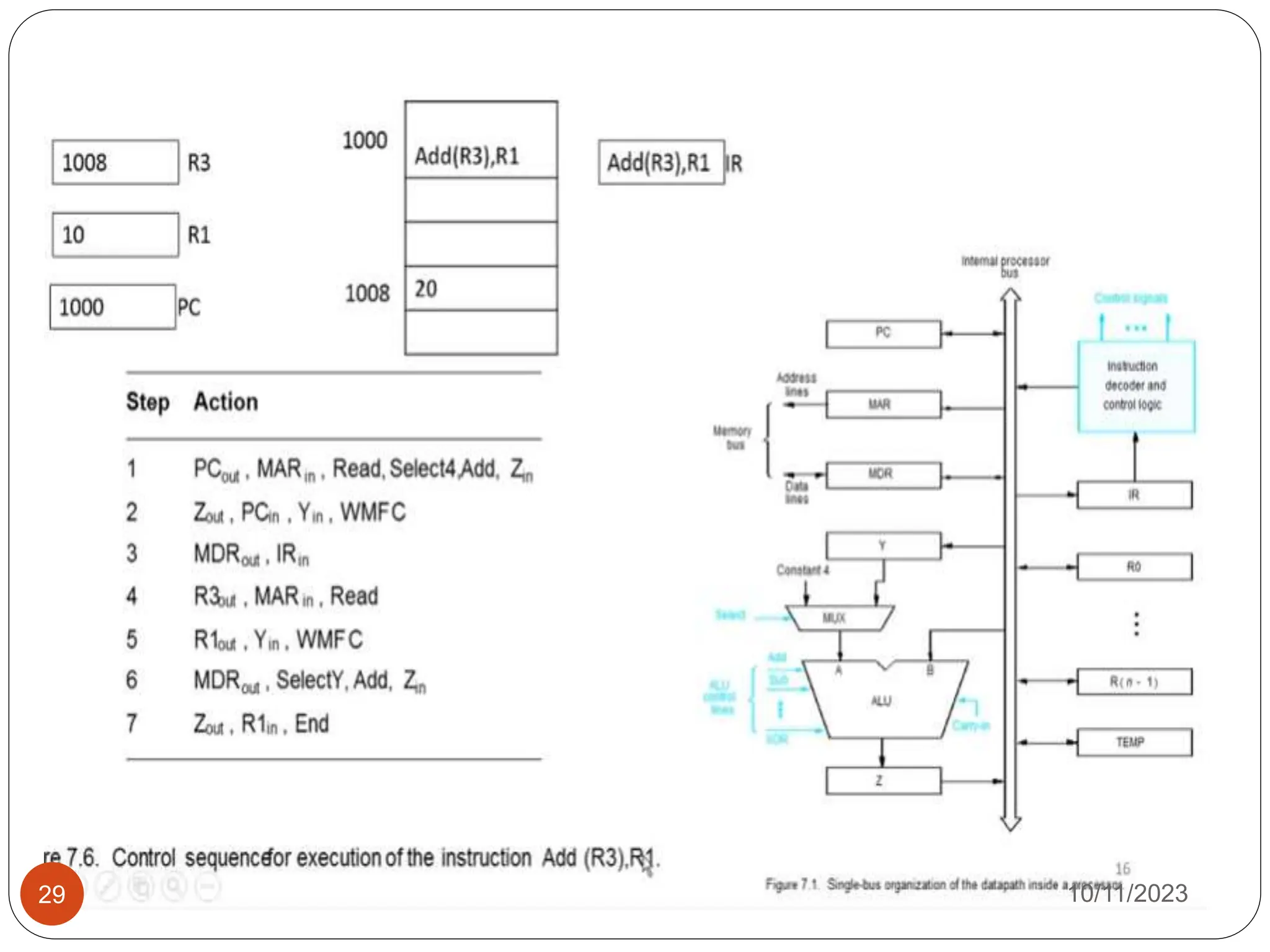

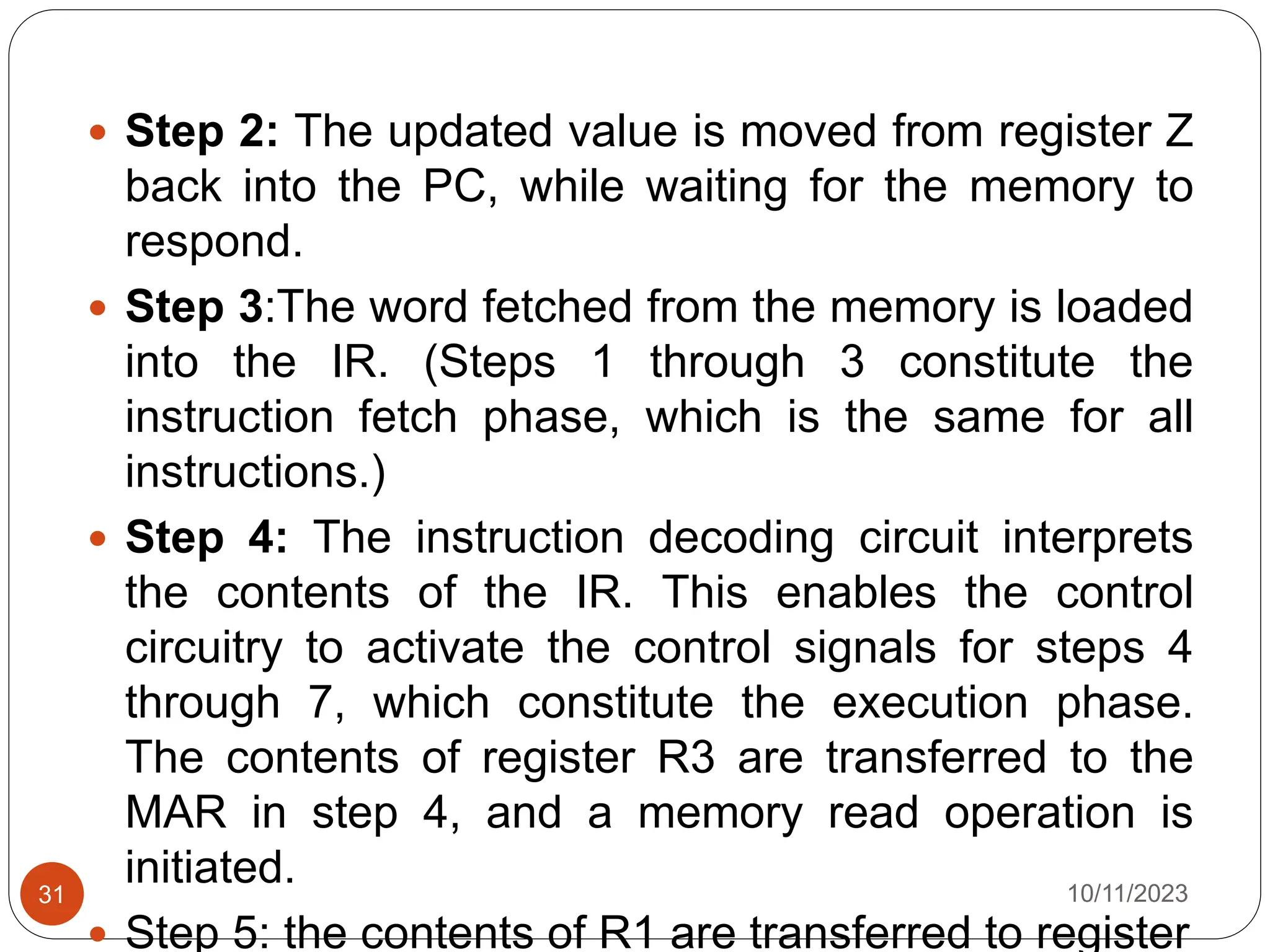

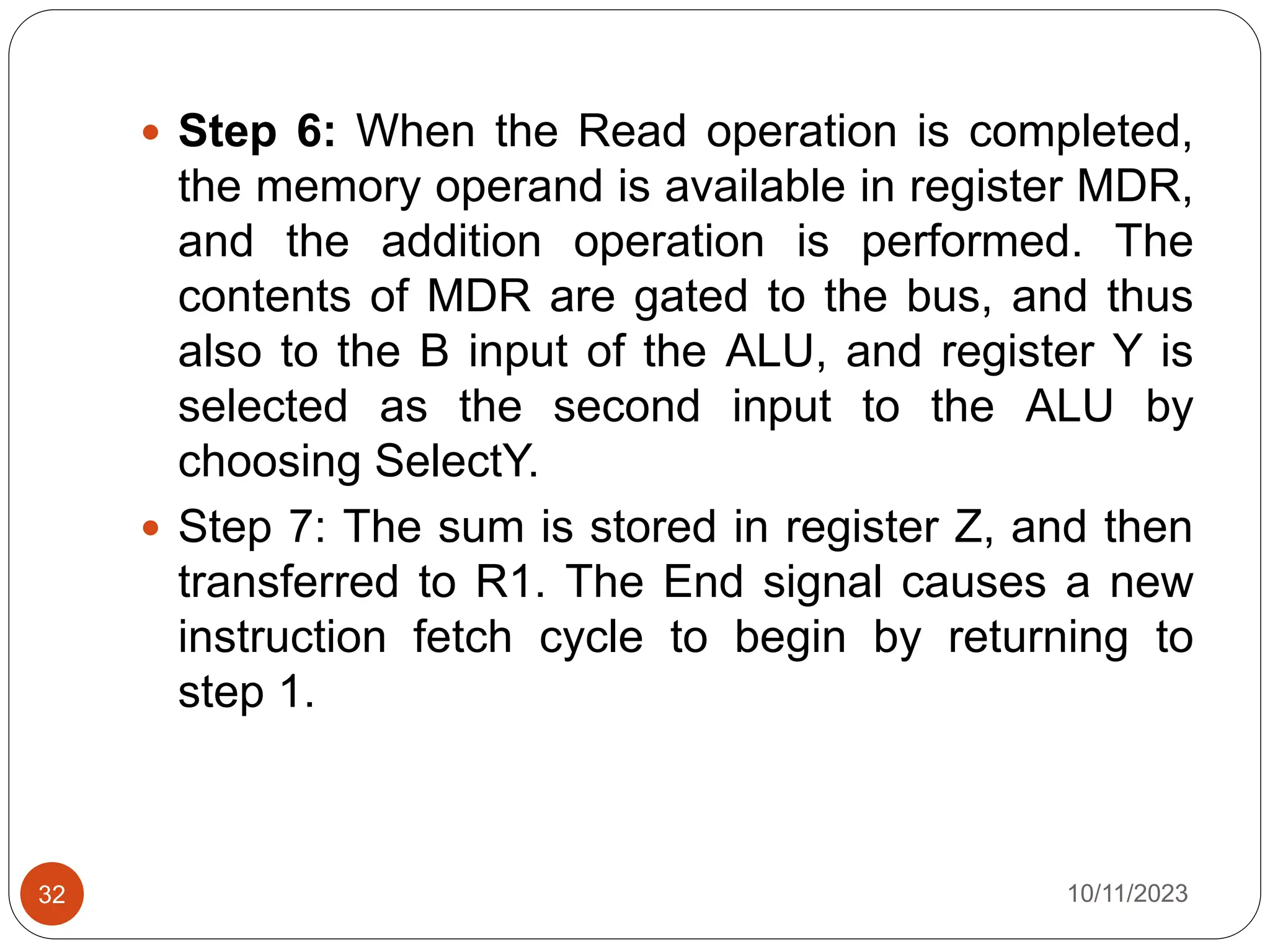

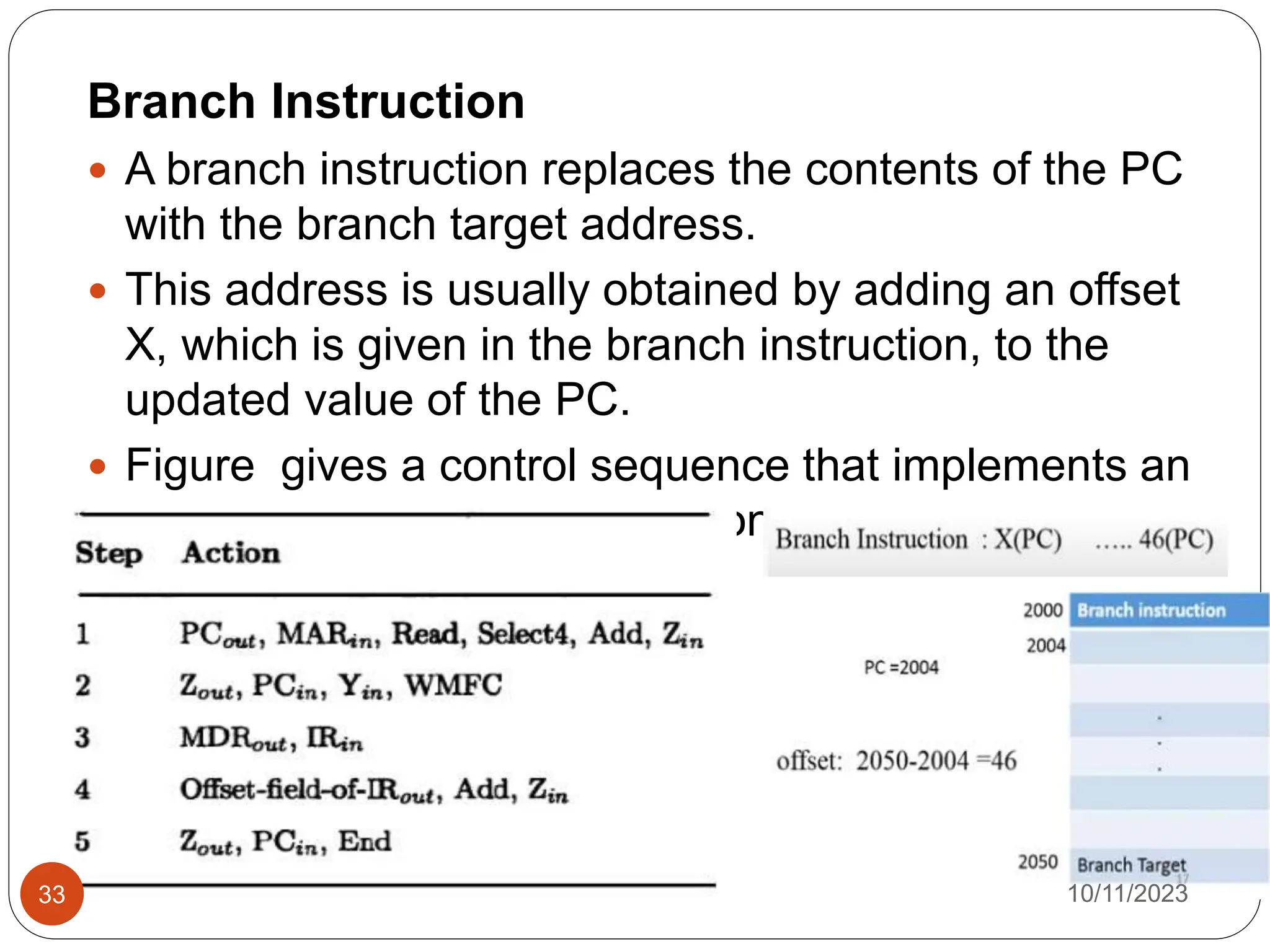

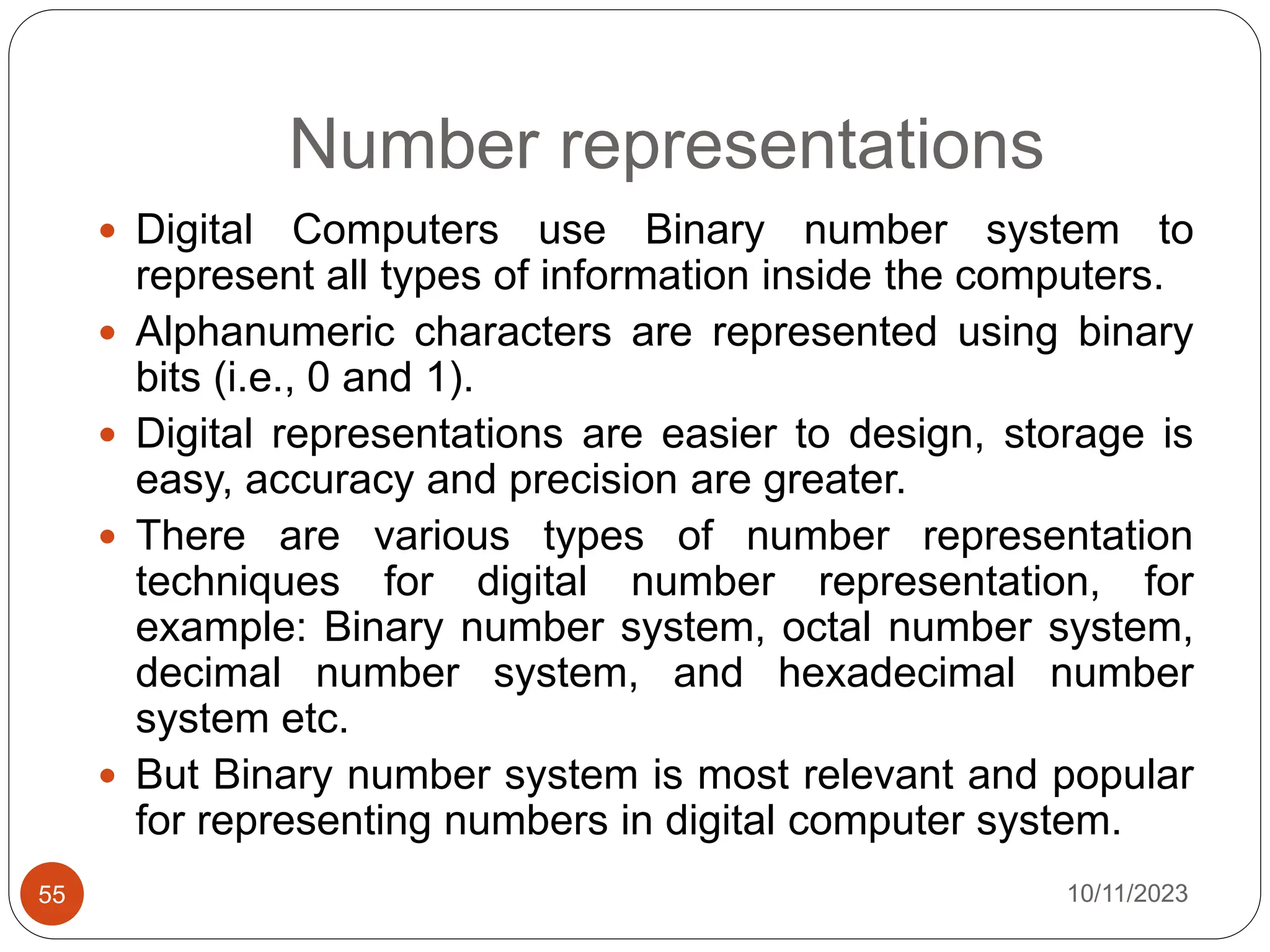

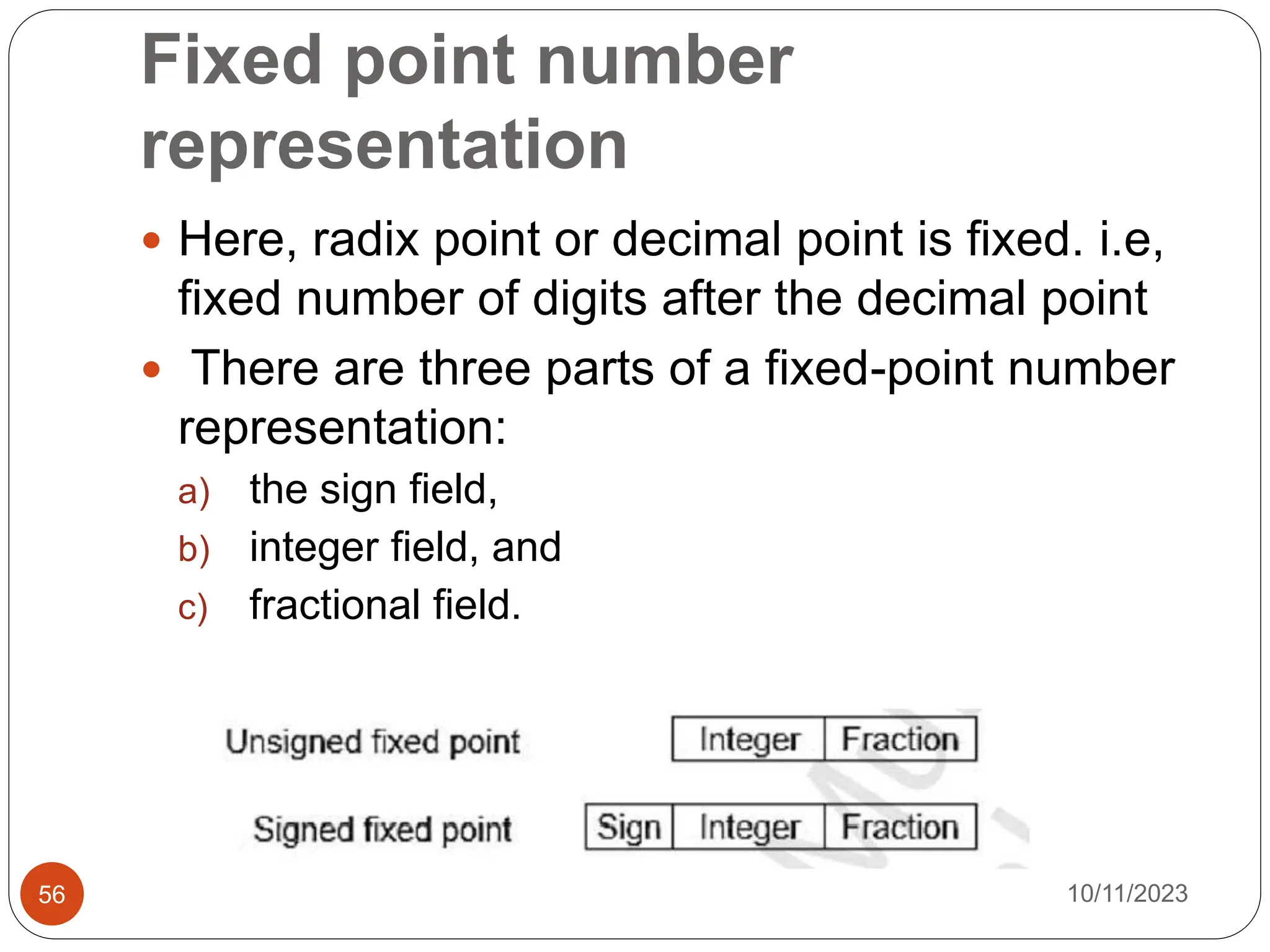

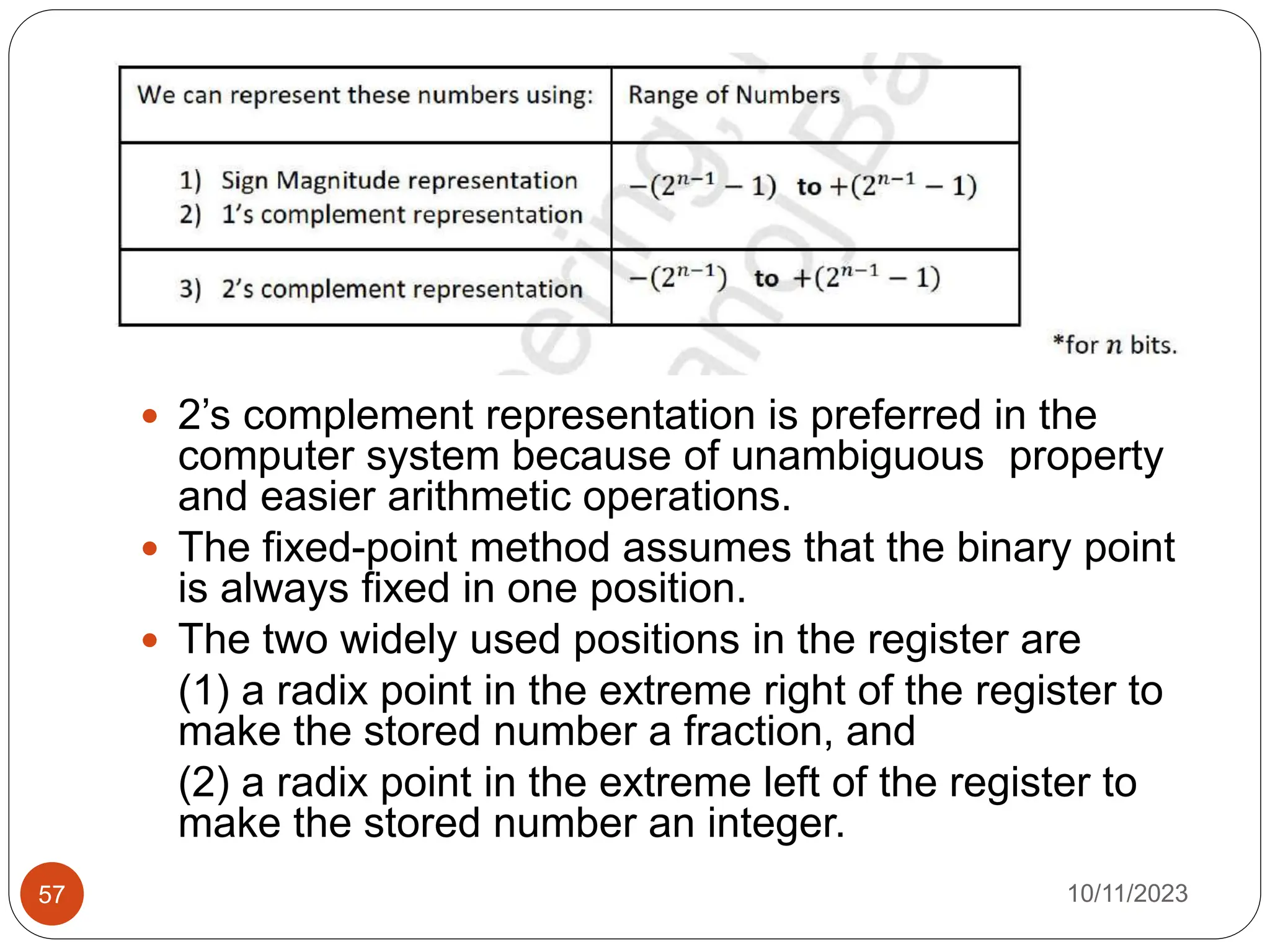

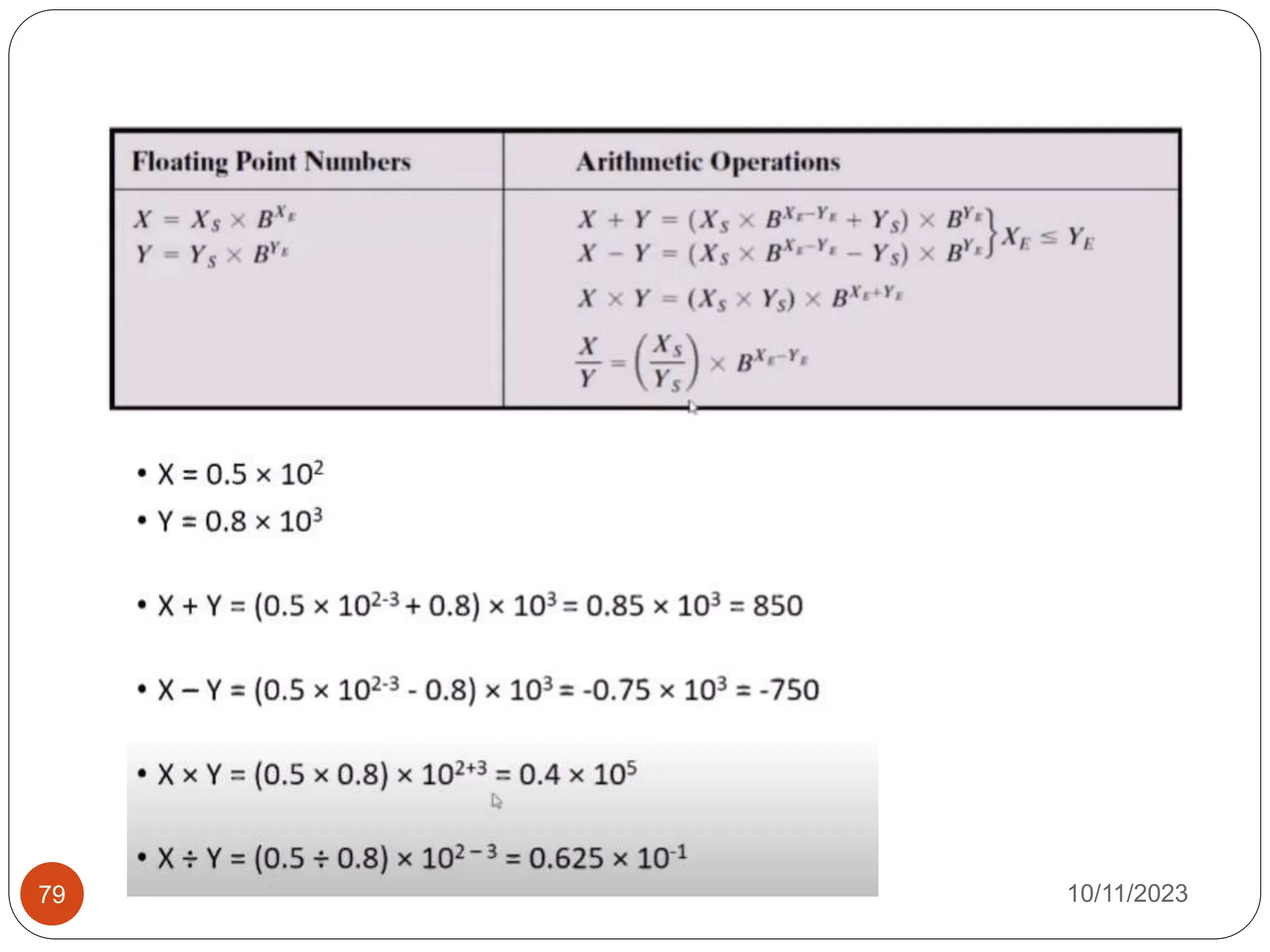

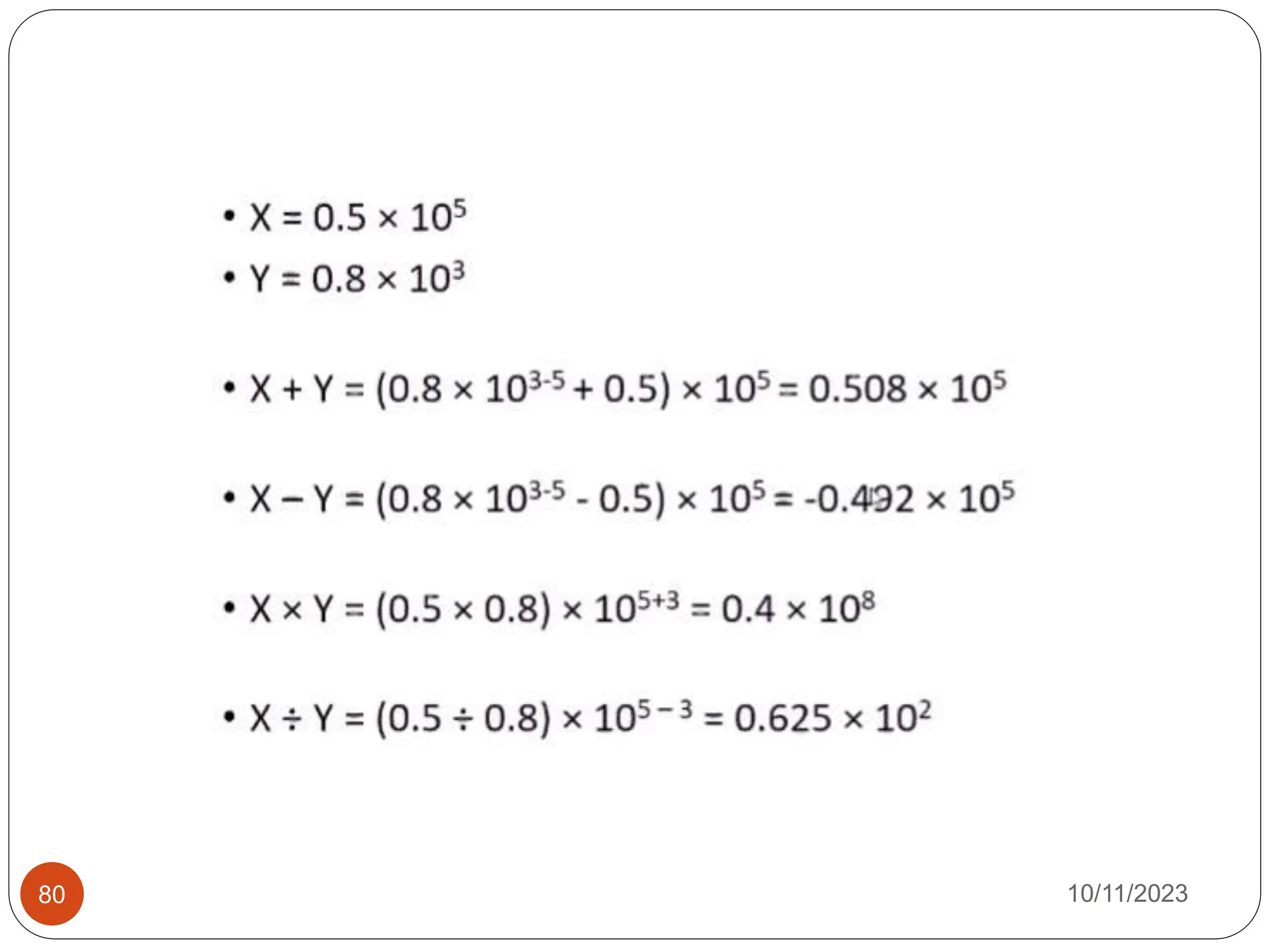

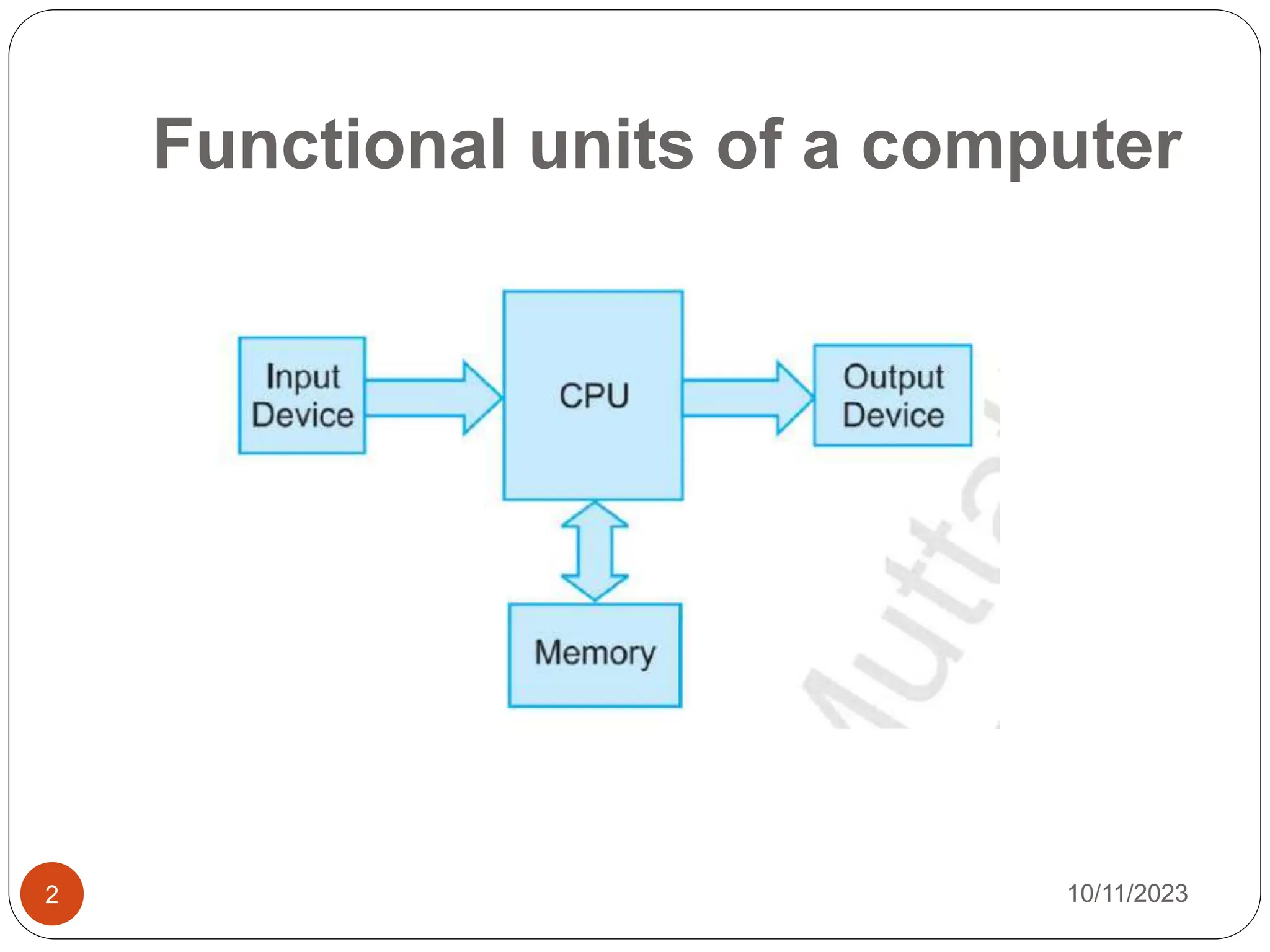

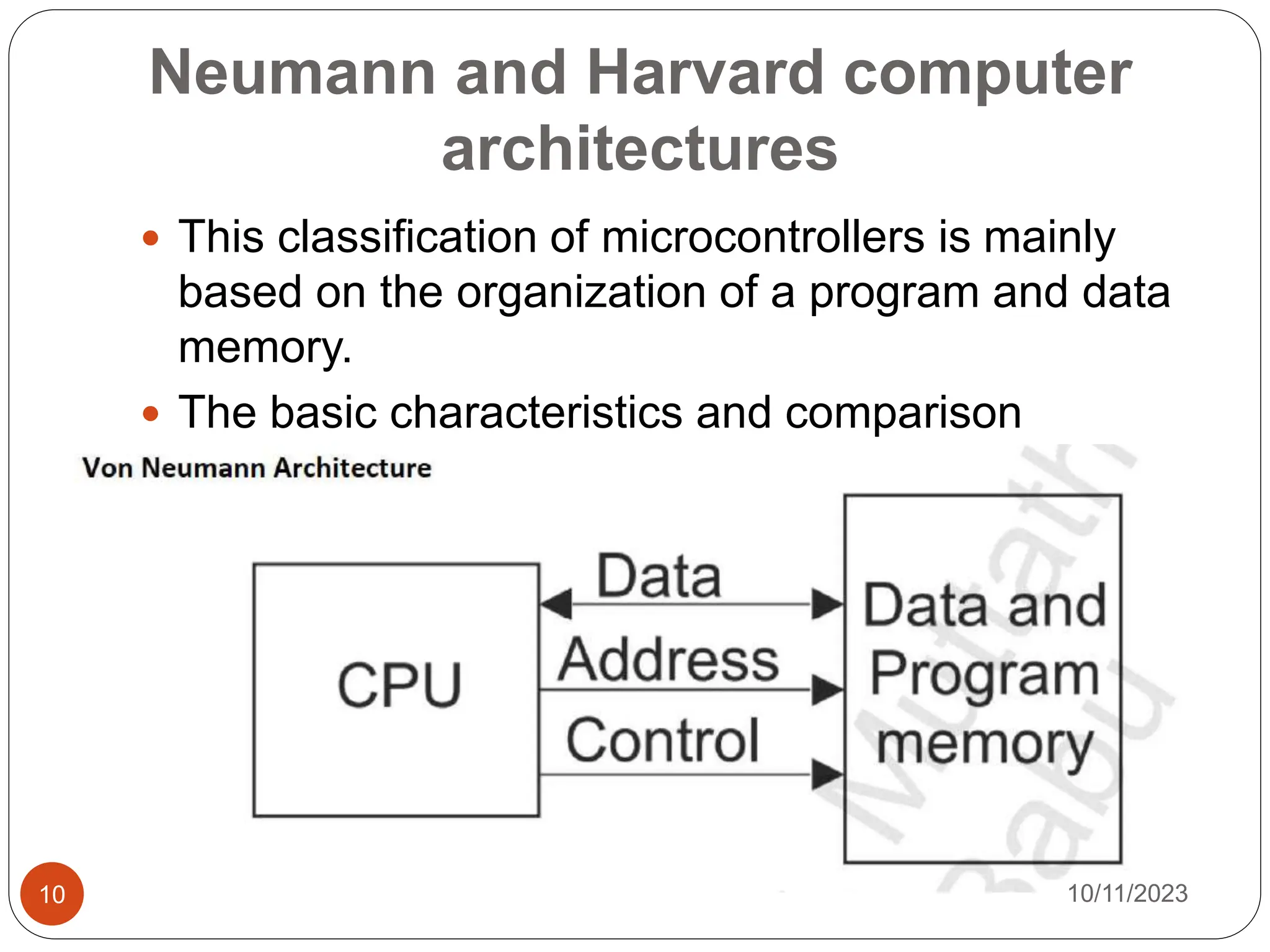

The document provides an in-depth overview of computer architecture, covering essential components like the CPU, memory (primary and secondary), I/O devices, and system buses. It explains key concepts including instruction execution, register functionality, data transfer, and the differences between von Neumann and Harvard architectures. Additionally, it details the process of fetching and storing data in memory and how instructions are executed in a sequence.

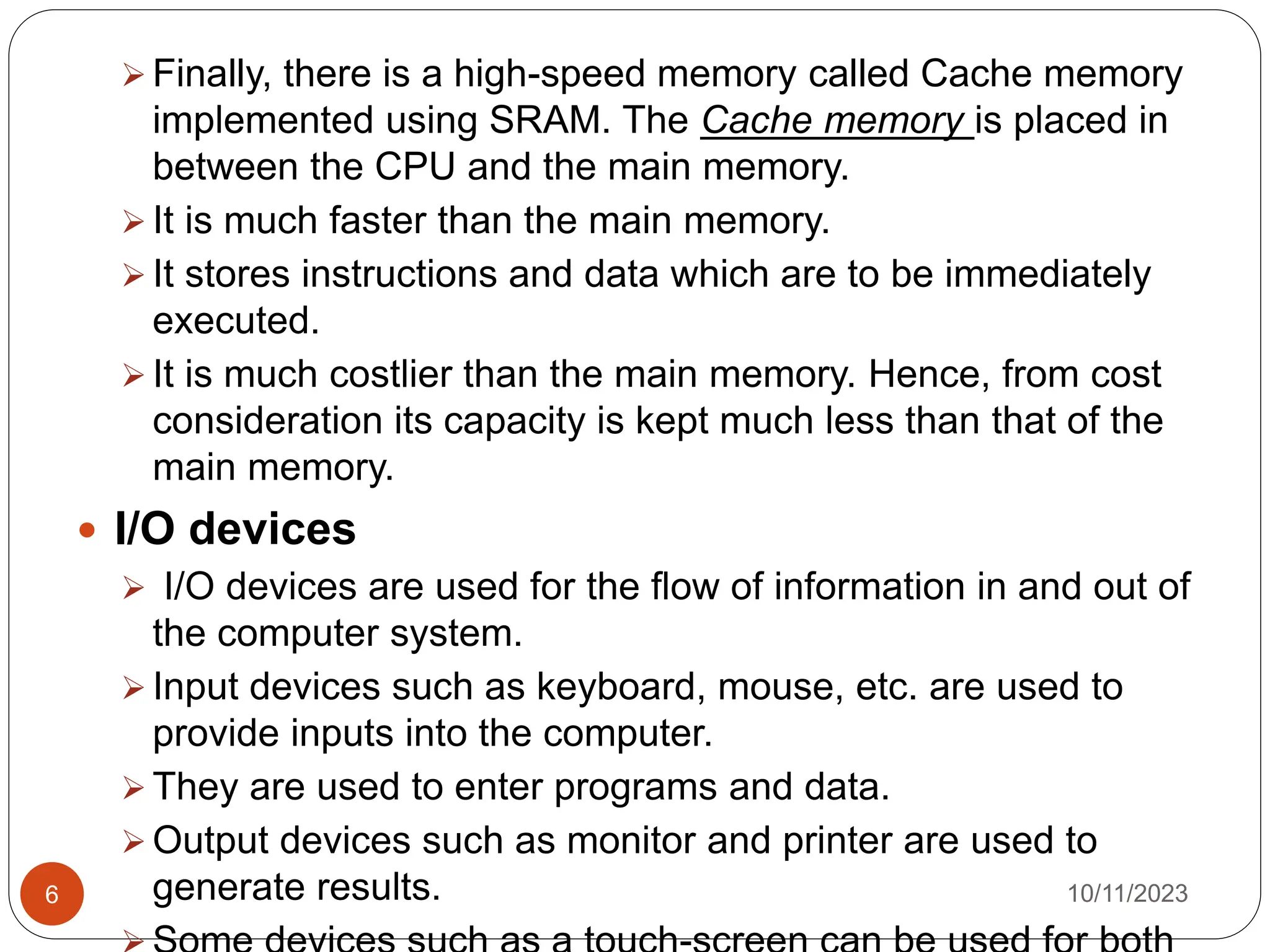

![ Suppose that each instruction comprises 4 bytes,

and that it is stored in one memory word. To

execute an instruction, the processor has to

perform the following three steps:

1. Fetch the contents of the memory location pointed

to by the PC. The contents of this location are

interpreted as an instruction to be executed.

Hence, they are loaded into the IR. Symbolically,

this can be written as IR ← [[PC]]

2. Assuming that the memory is byte addressable,

increment the contents of the PC by 4 (fetch

phase), that is, PC ← [PC]+ 4

3. Carry out the actions specified by the instruction

in the IR(execution phase).

10/11/2023

15](https://image.slidesharecdn.com/module1-231011164322-6592aecc/75/Computer-Arithmetic-and-Processor-Basics-15-2048.jpg)