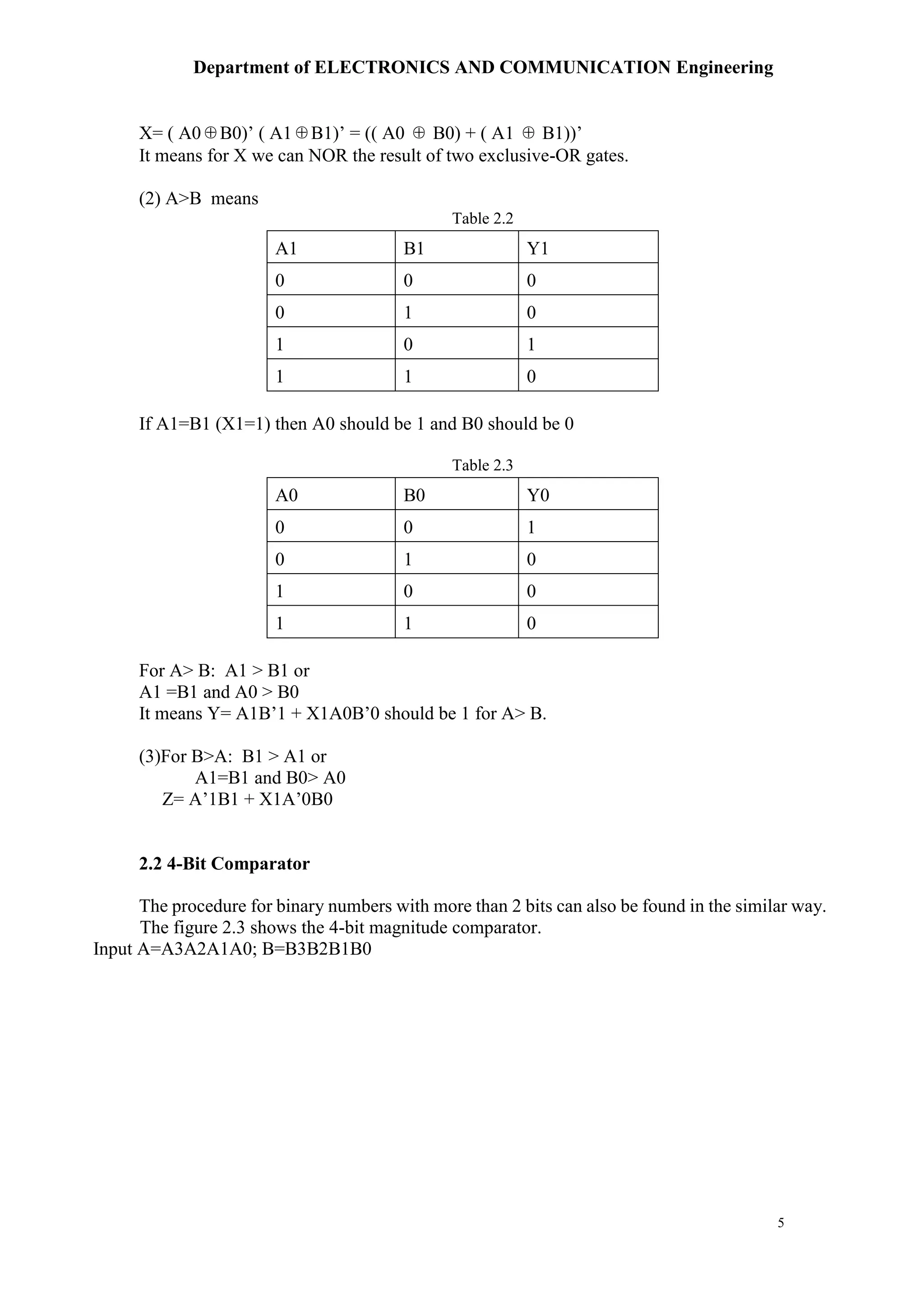

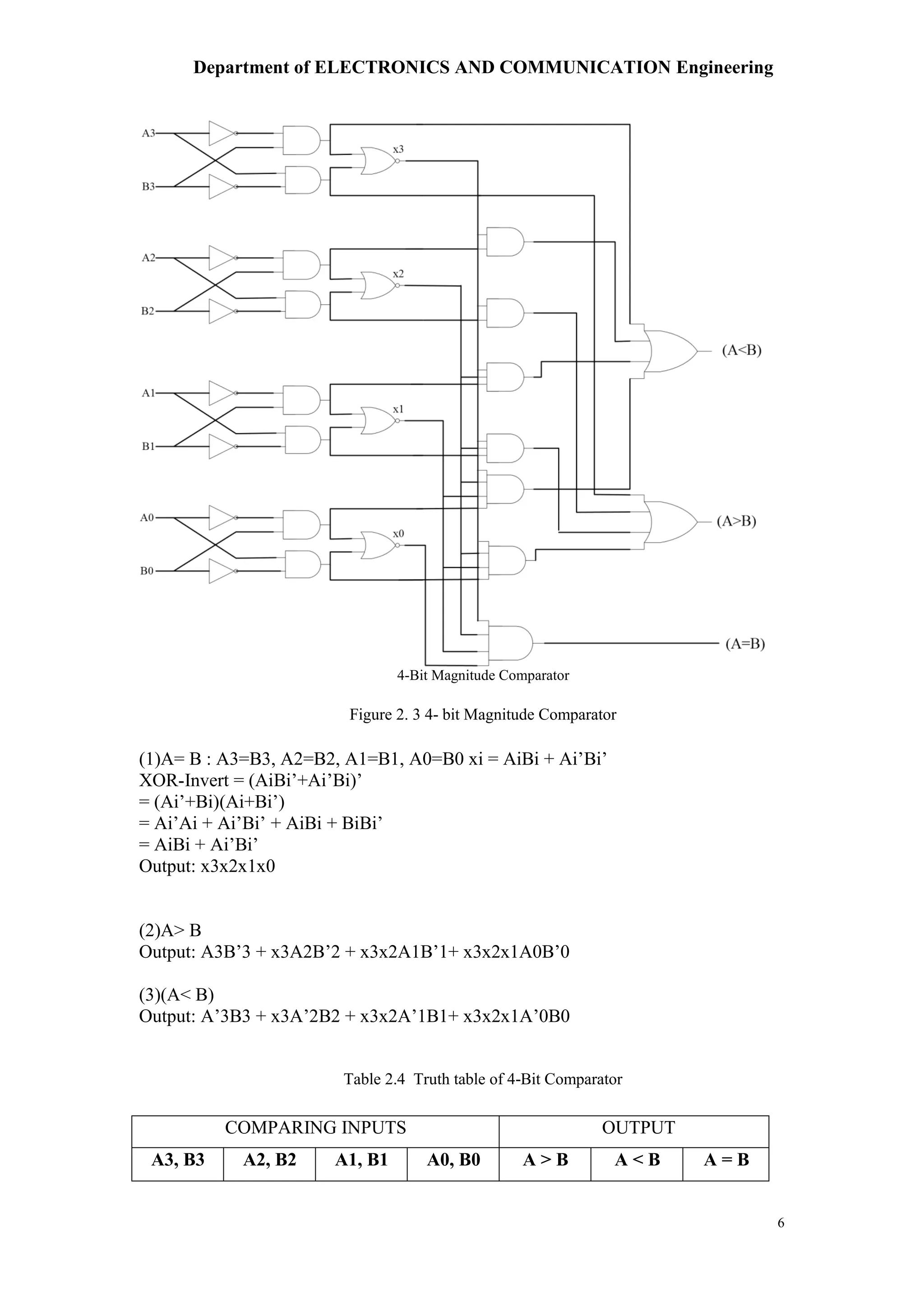

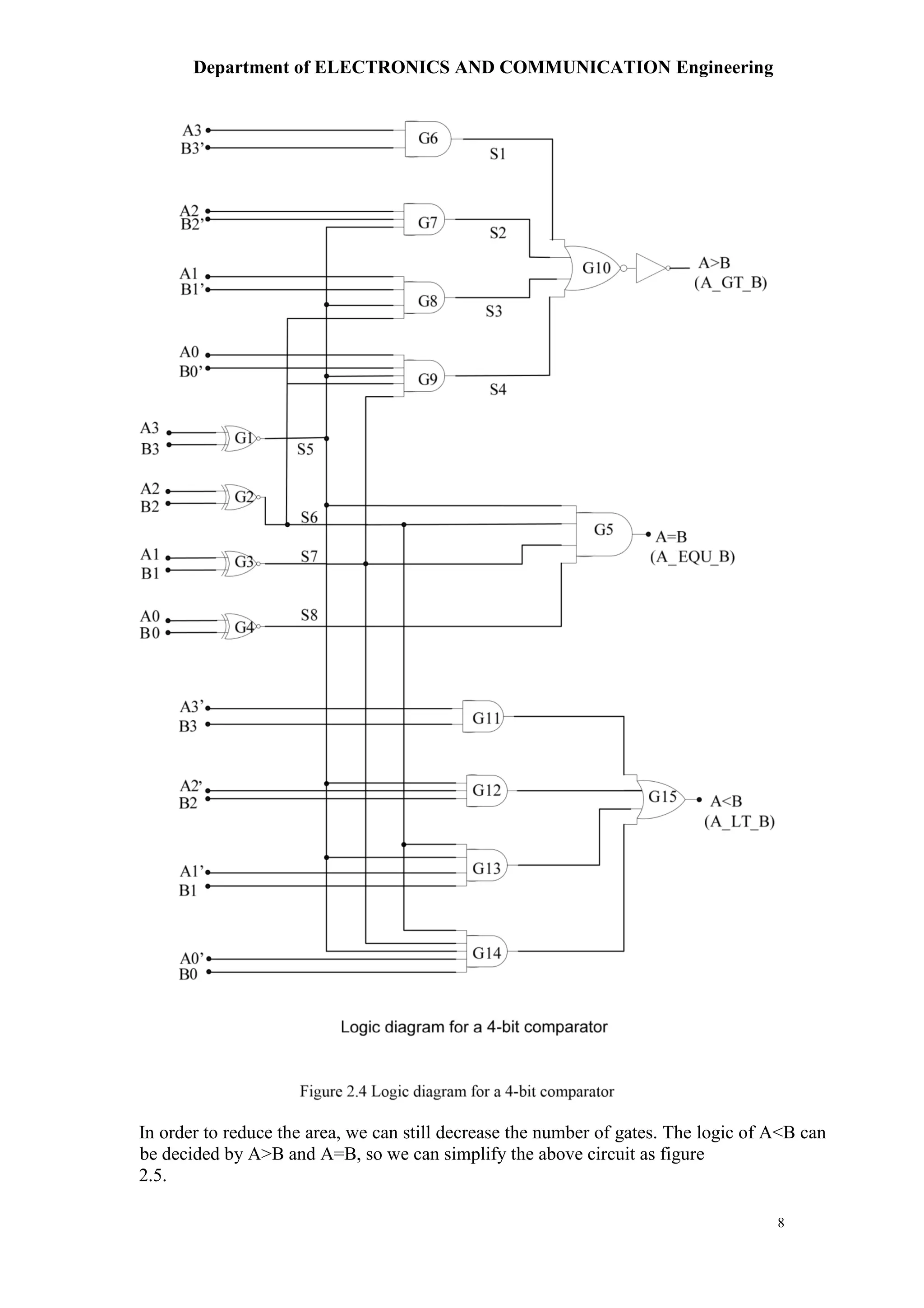

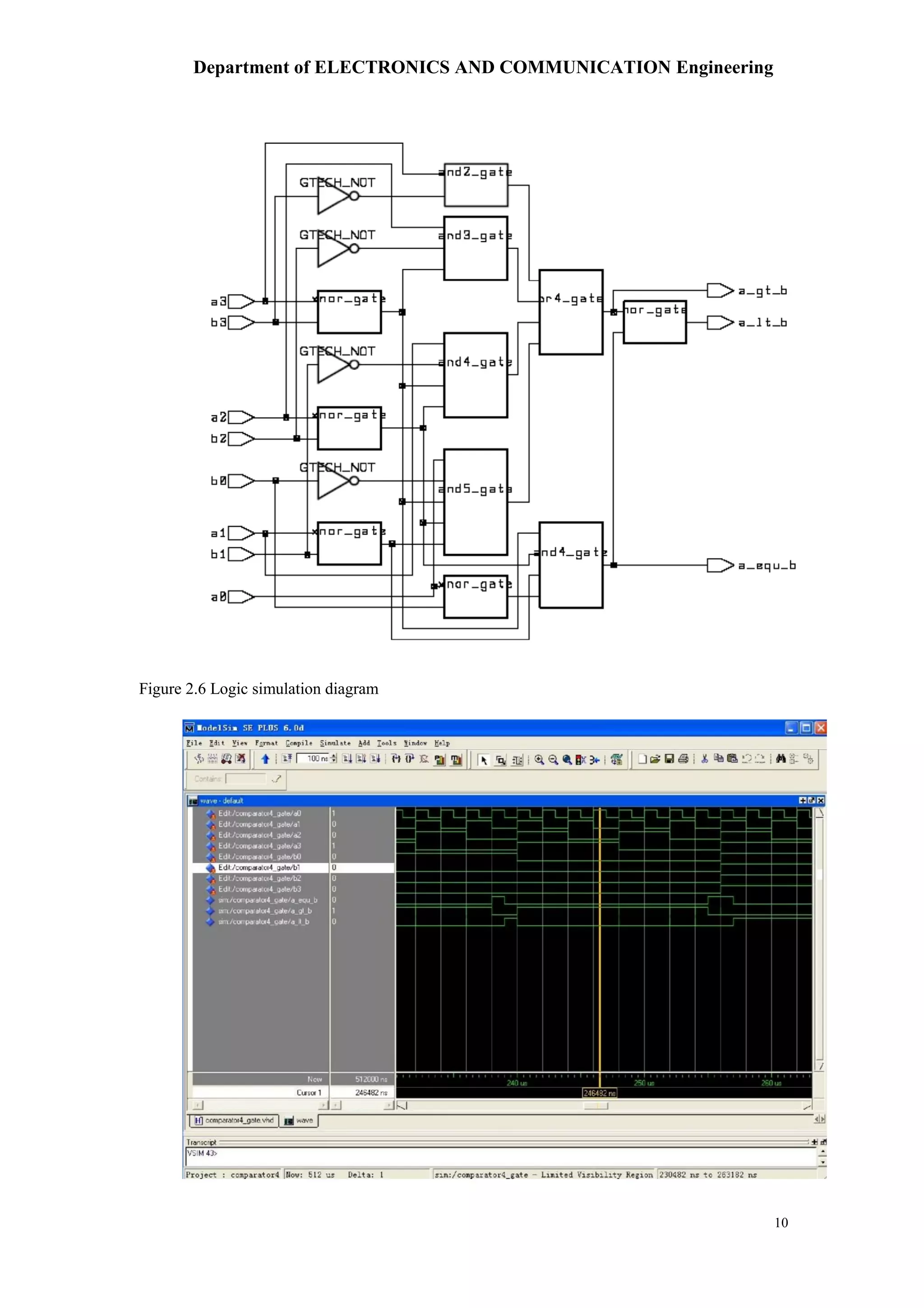

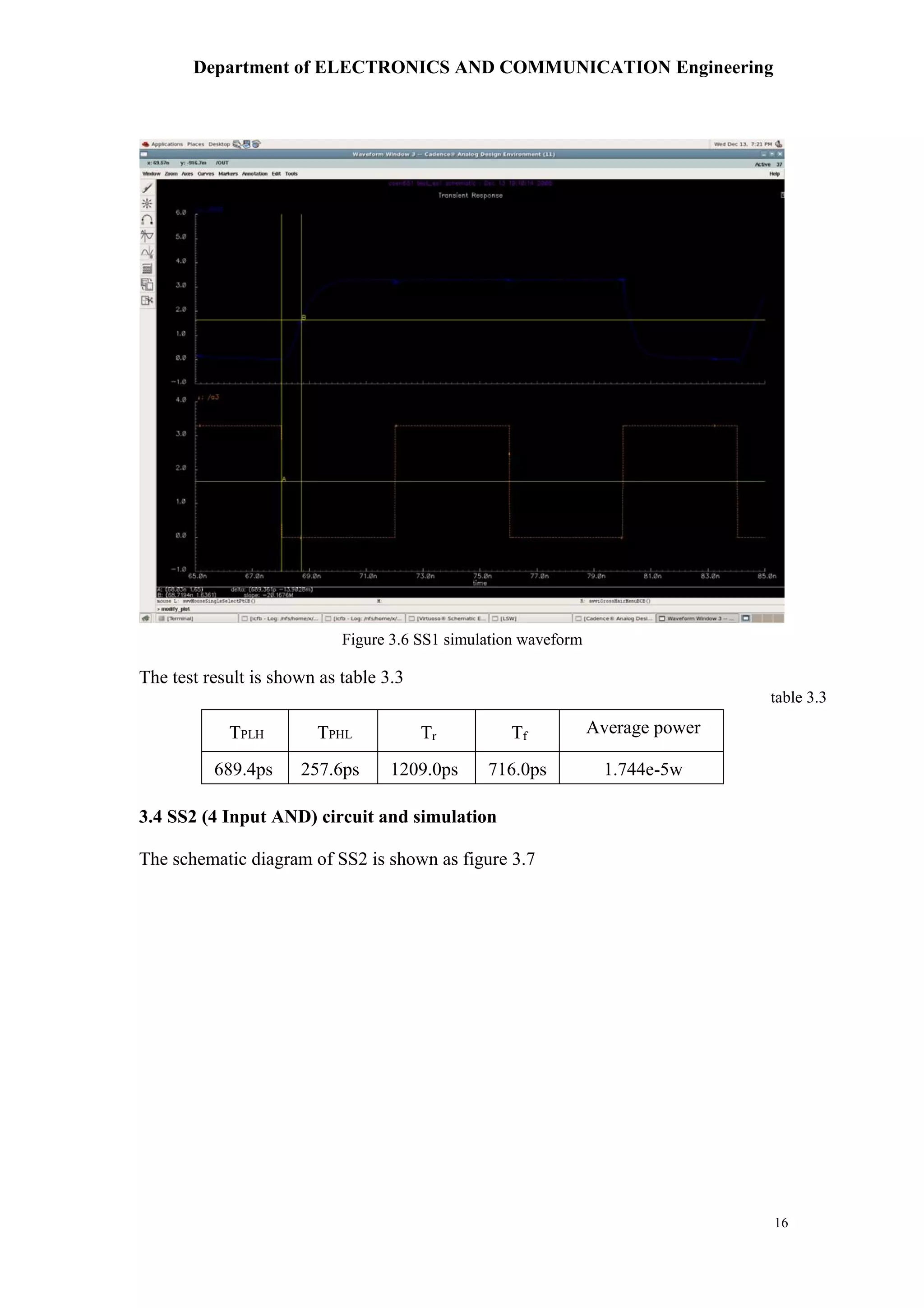

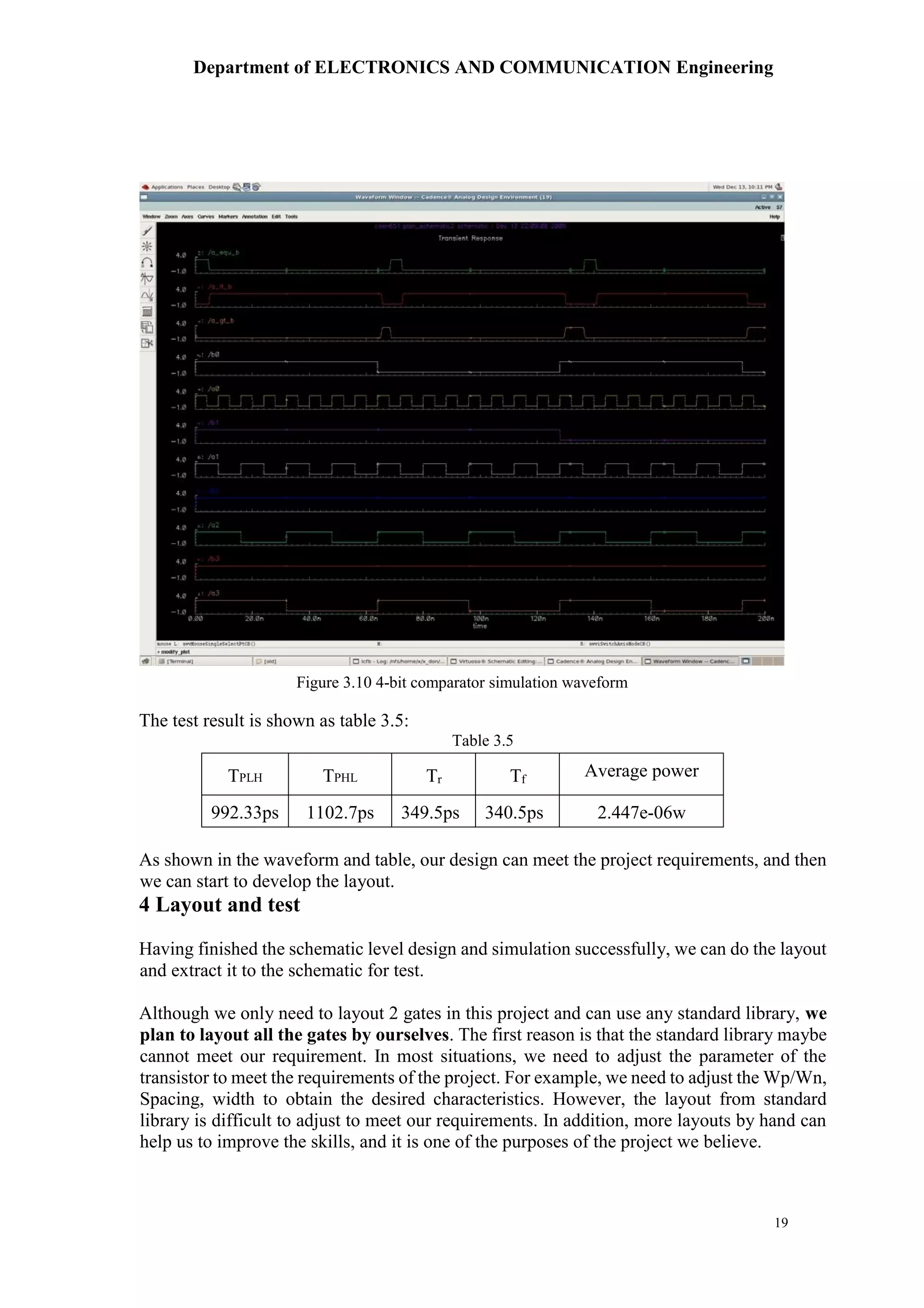

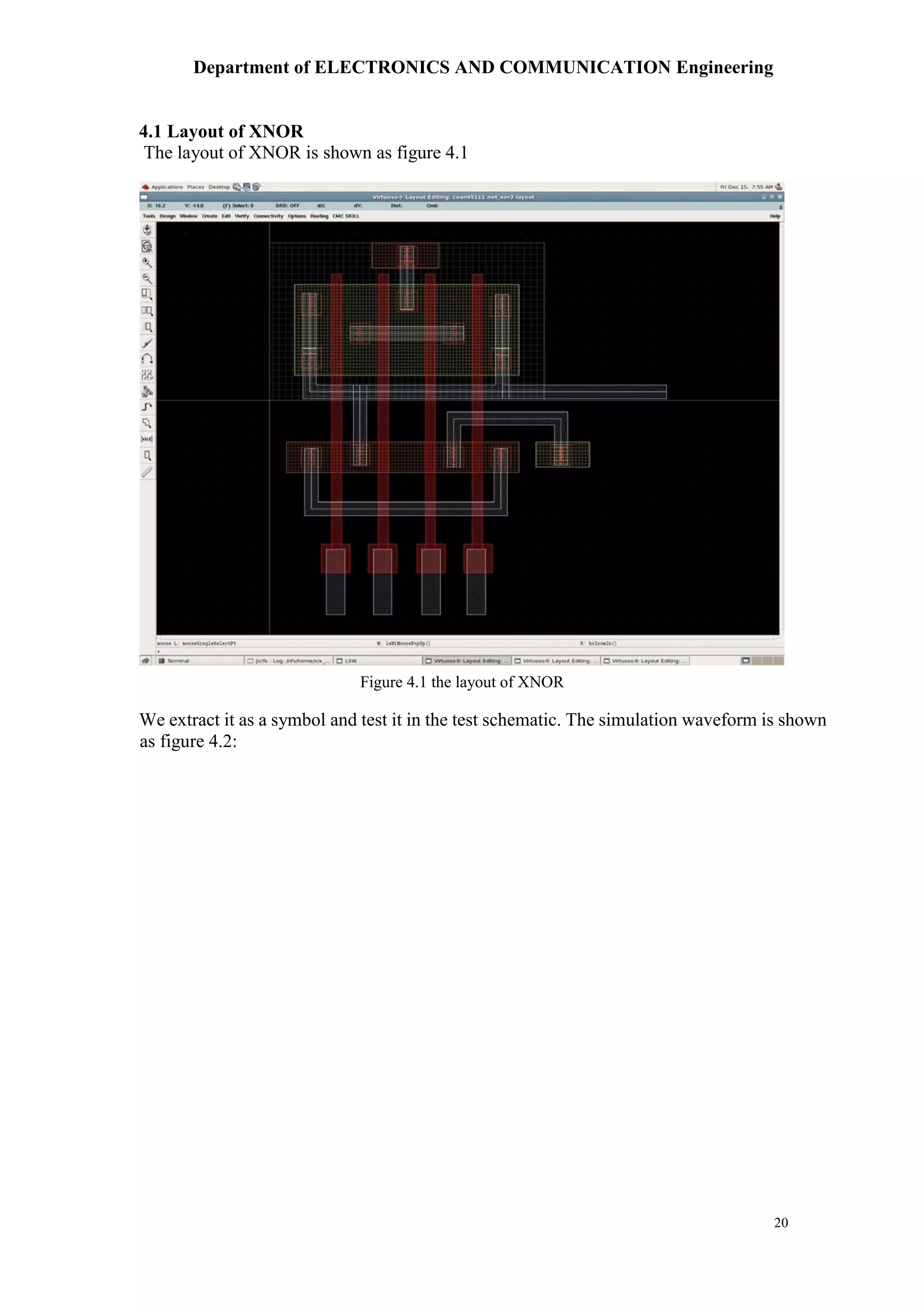

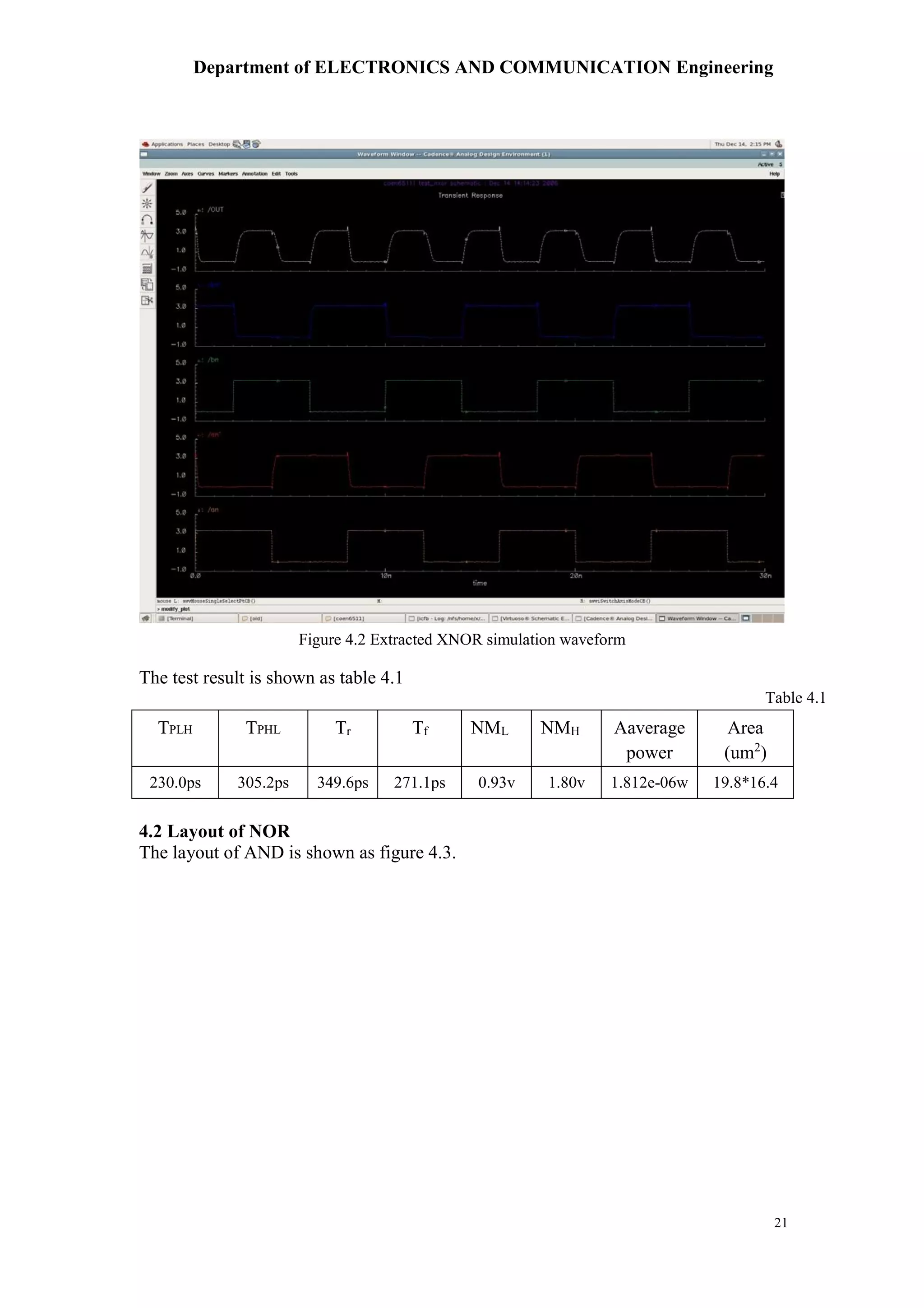

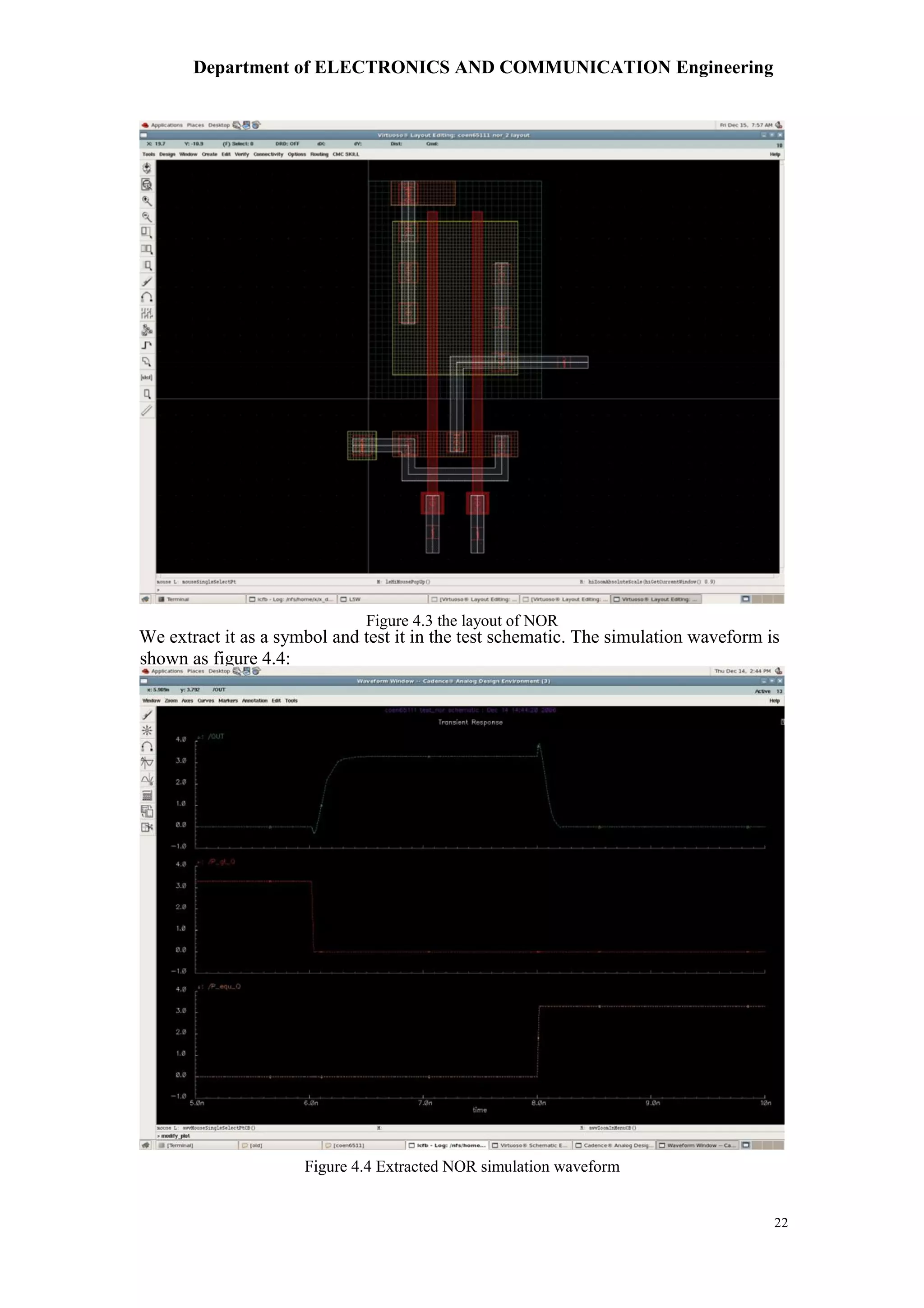

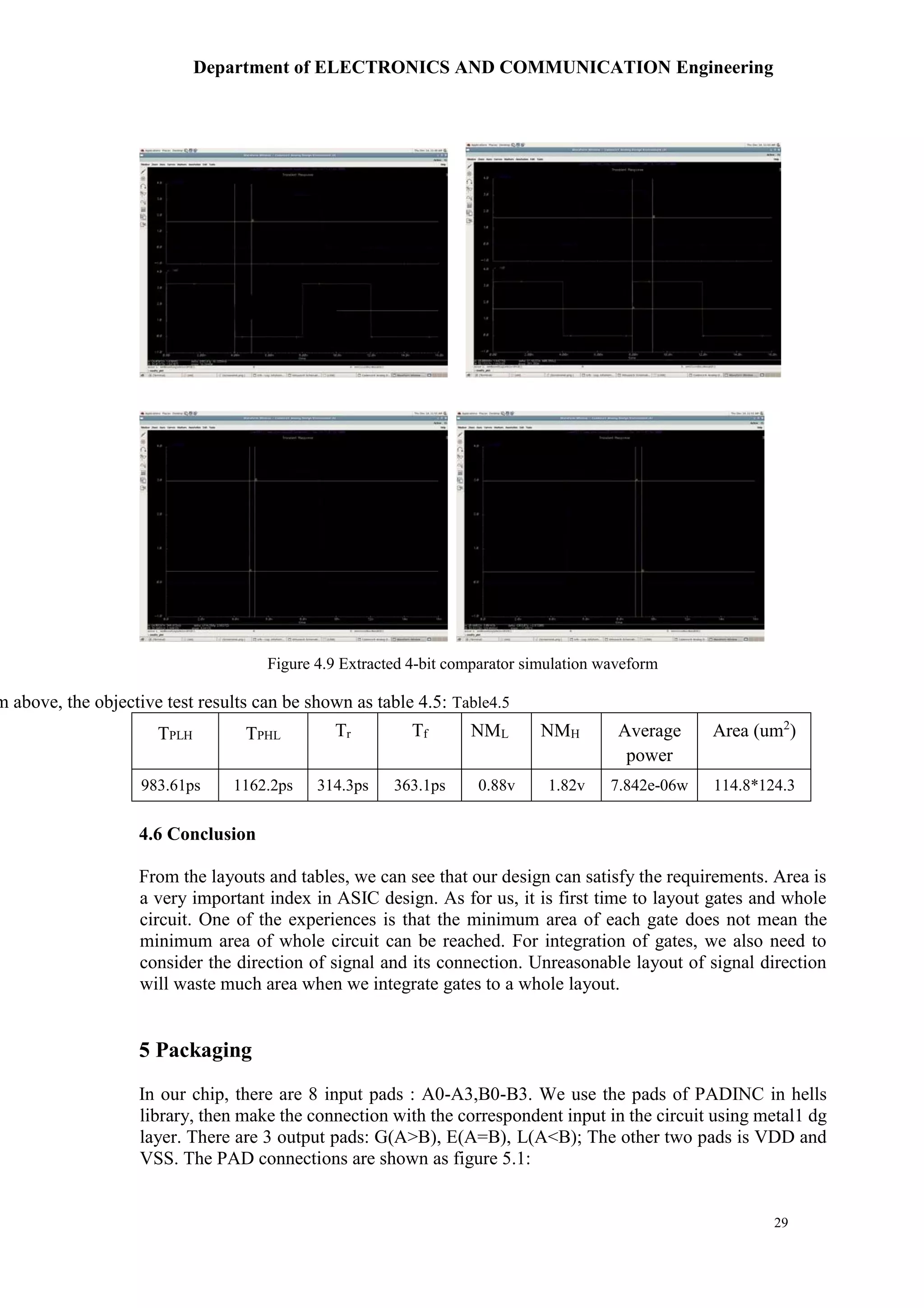

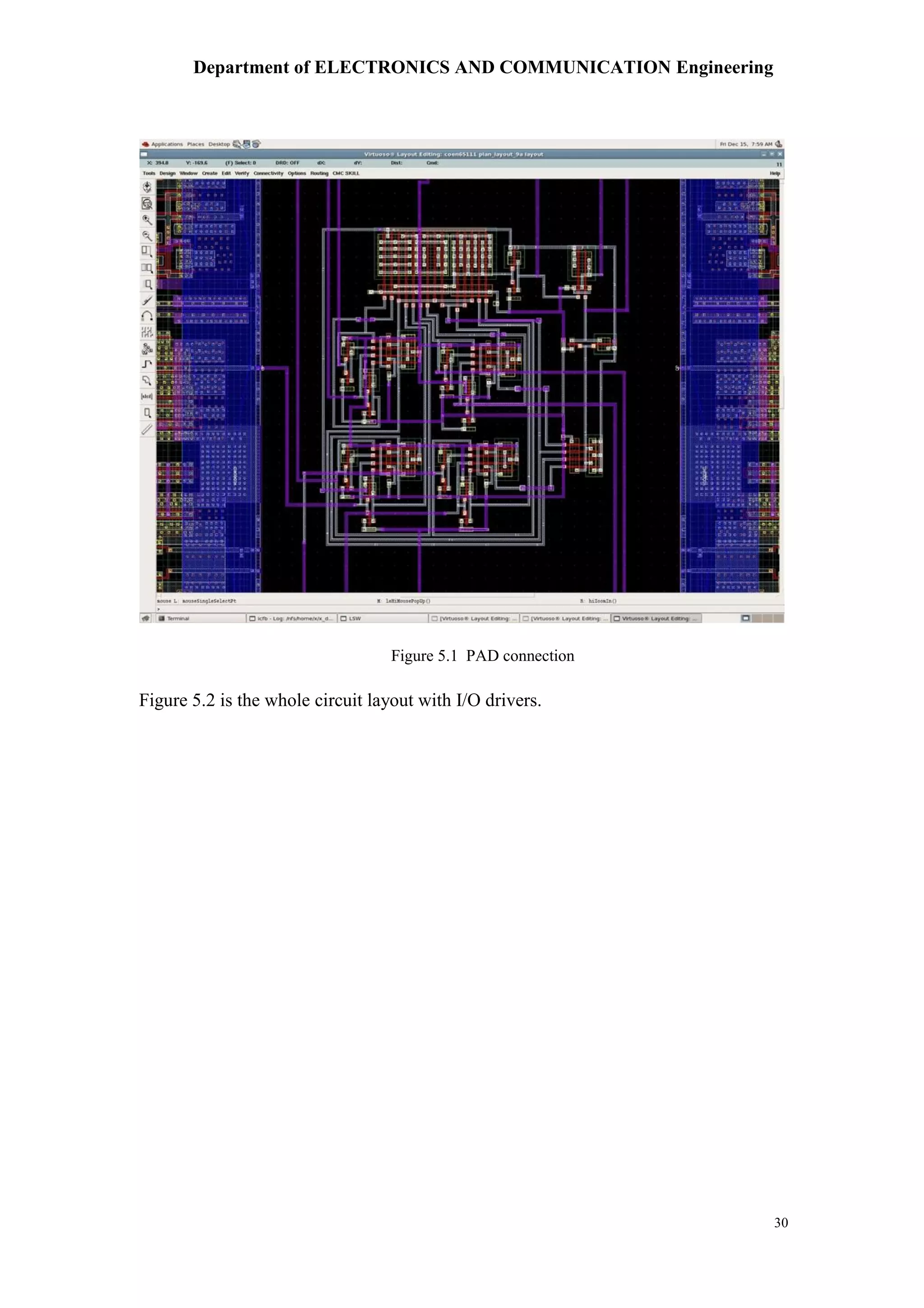

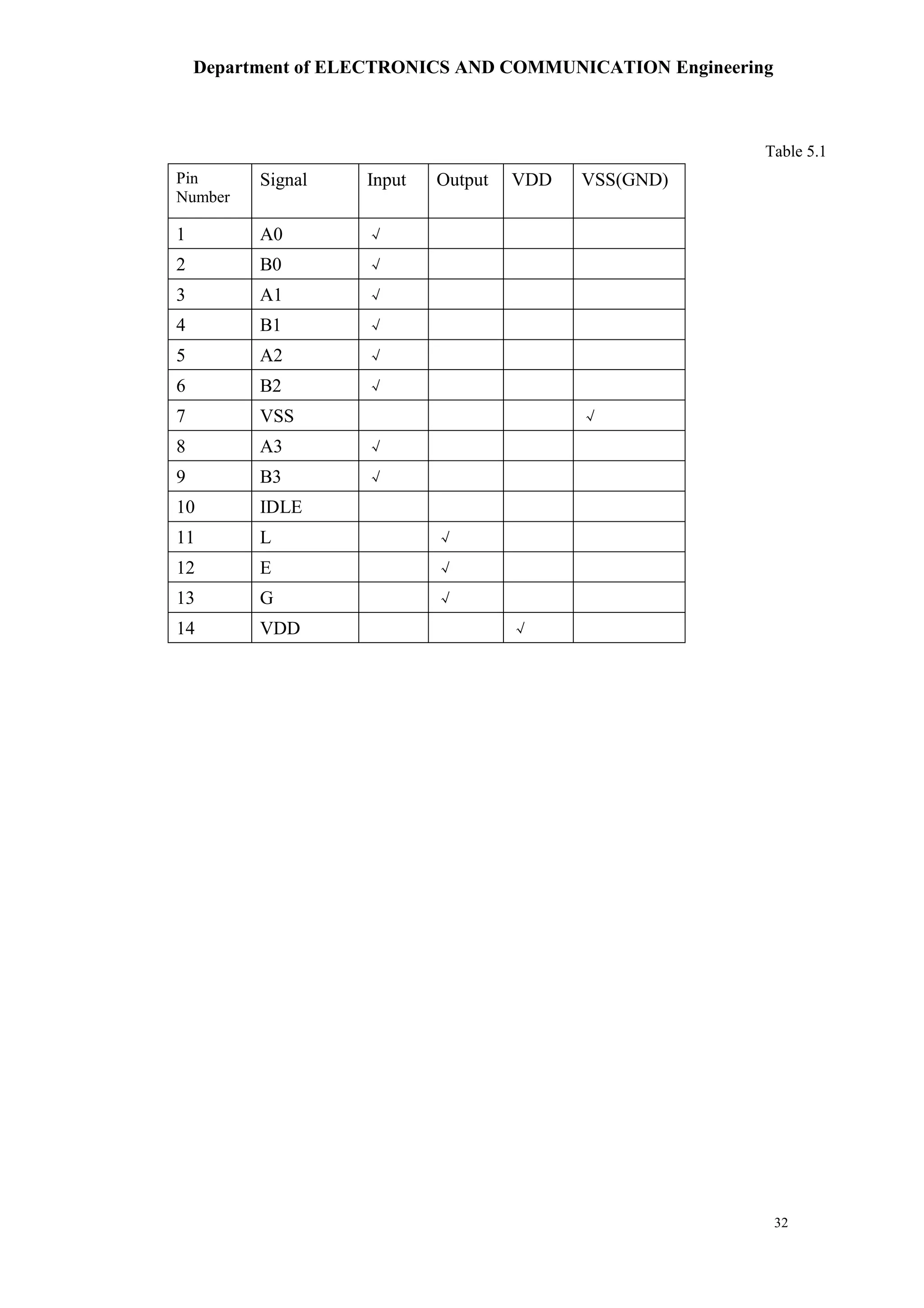

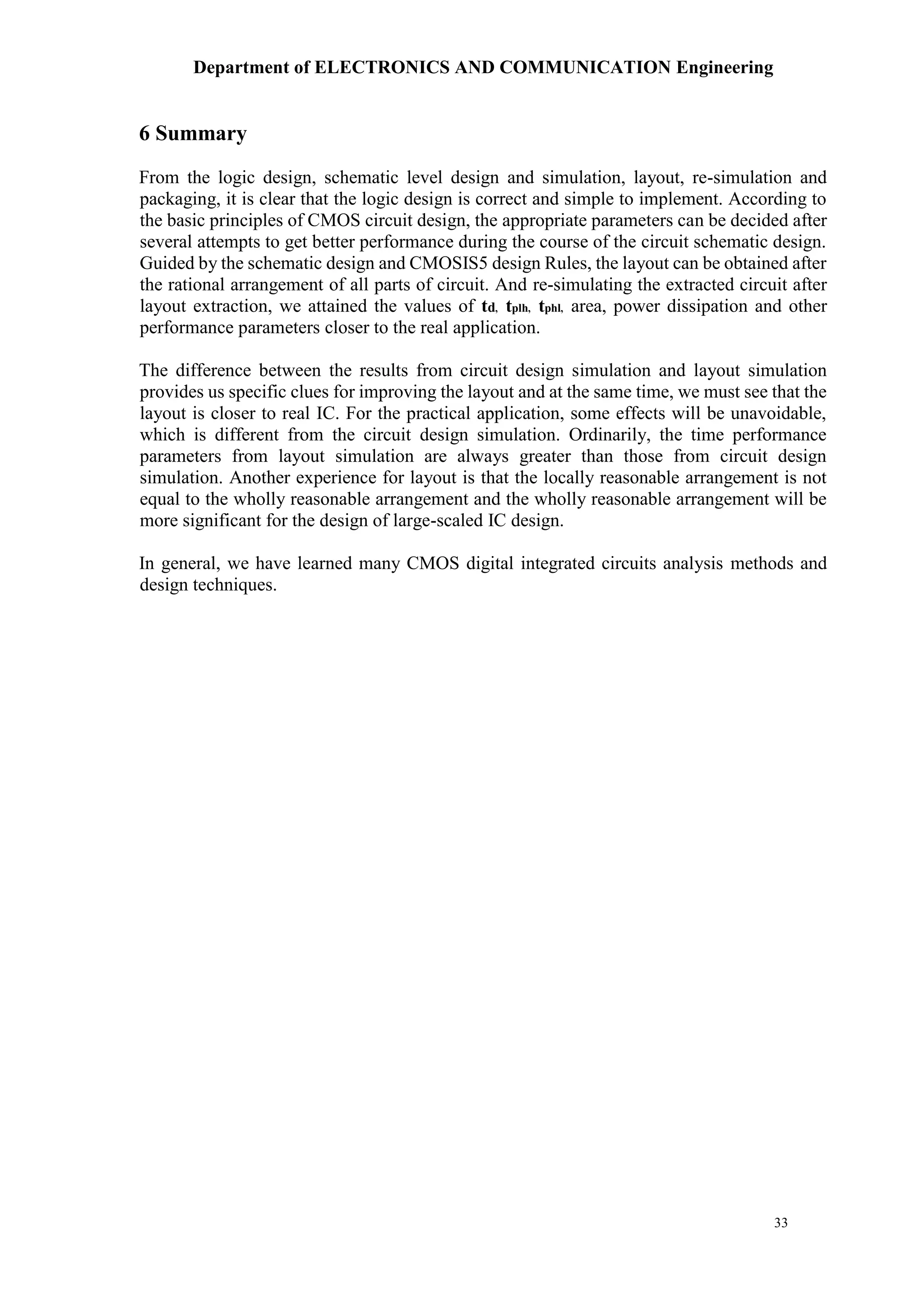

This project report details the design of a 4-bit comparator as part of the course COEN 6511, covering aspects such as logic design, circuit implementation, schematic simulation, and layout formation using the CMOS technology. Performance measures considered include area, power, and propagation delay, with satisfactory test results to confirm the logic design accuracy. The layout of the comparator followed the schematic design and was verified through simulation, ensuring that the project meets specified requirements.