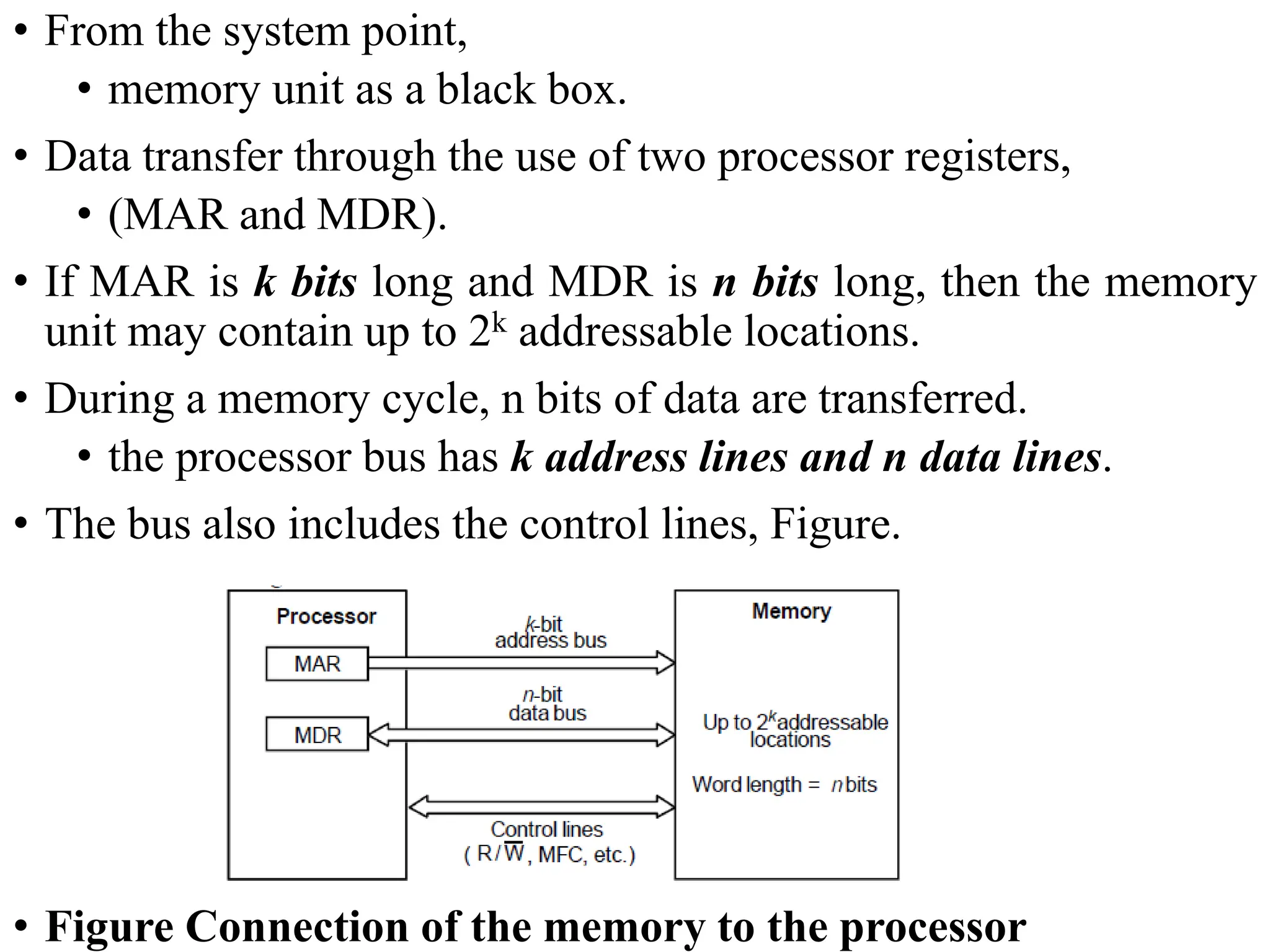

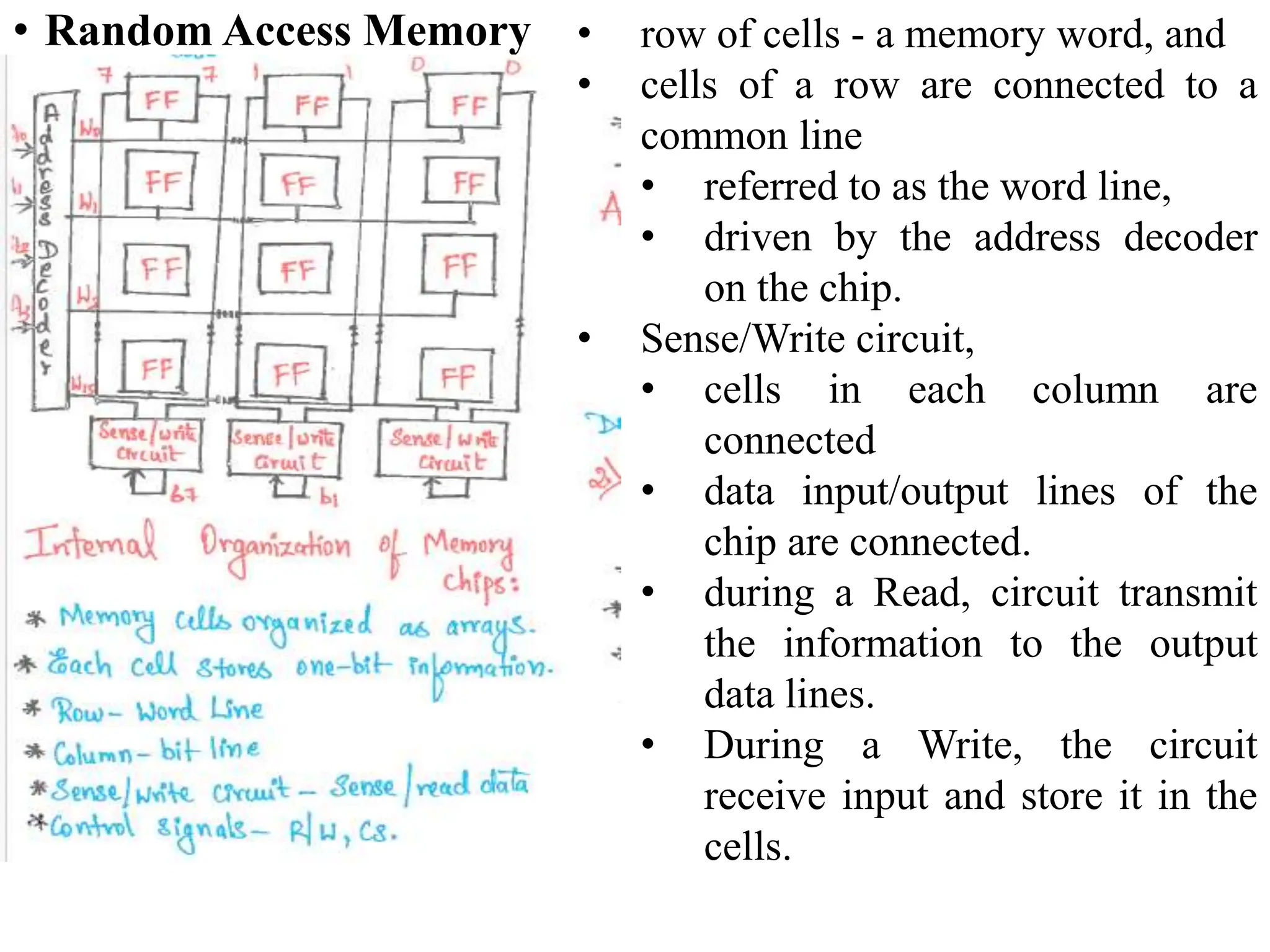

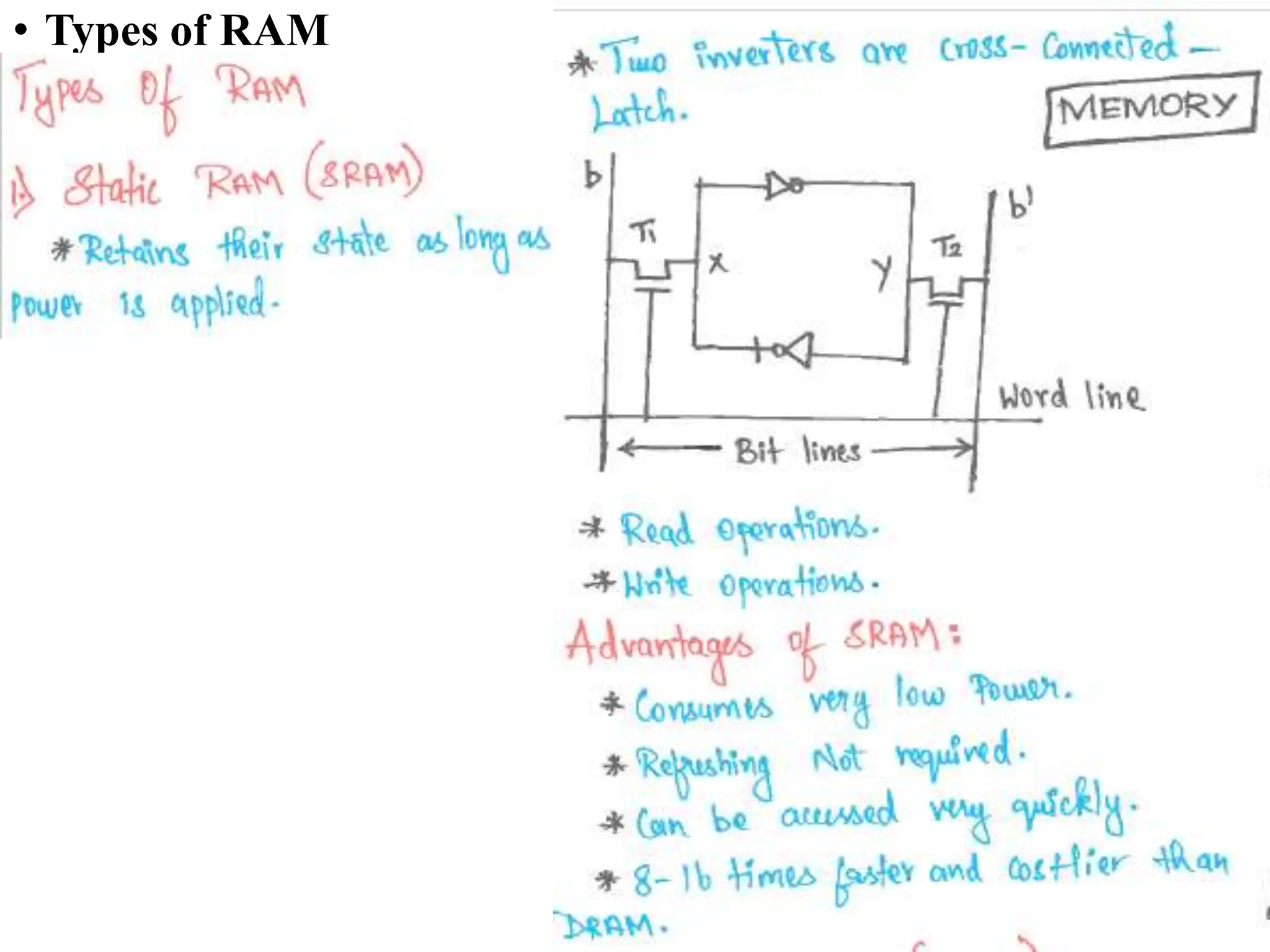

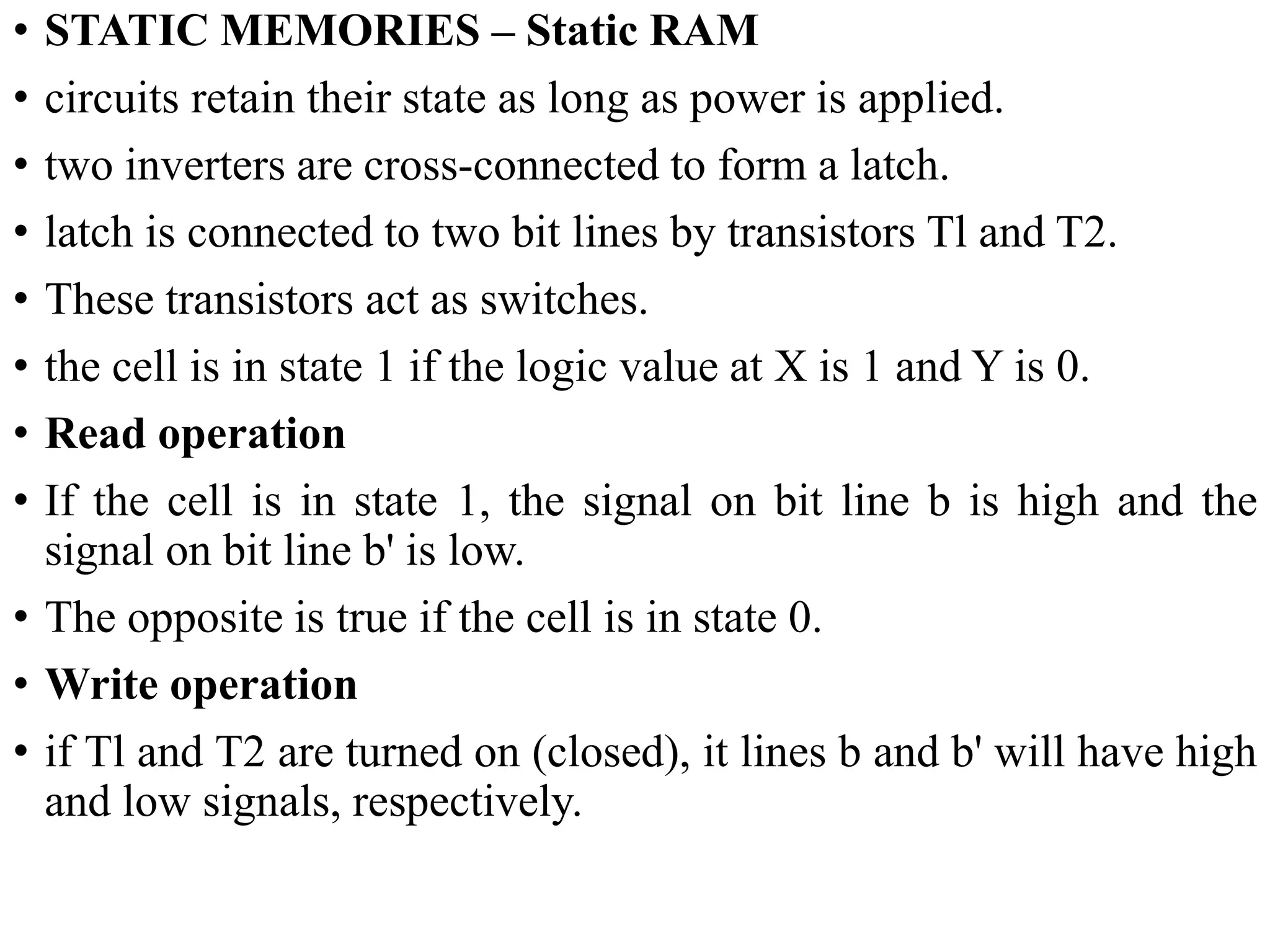

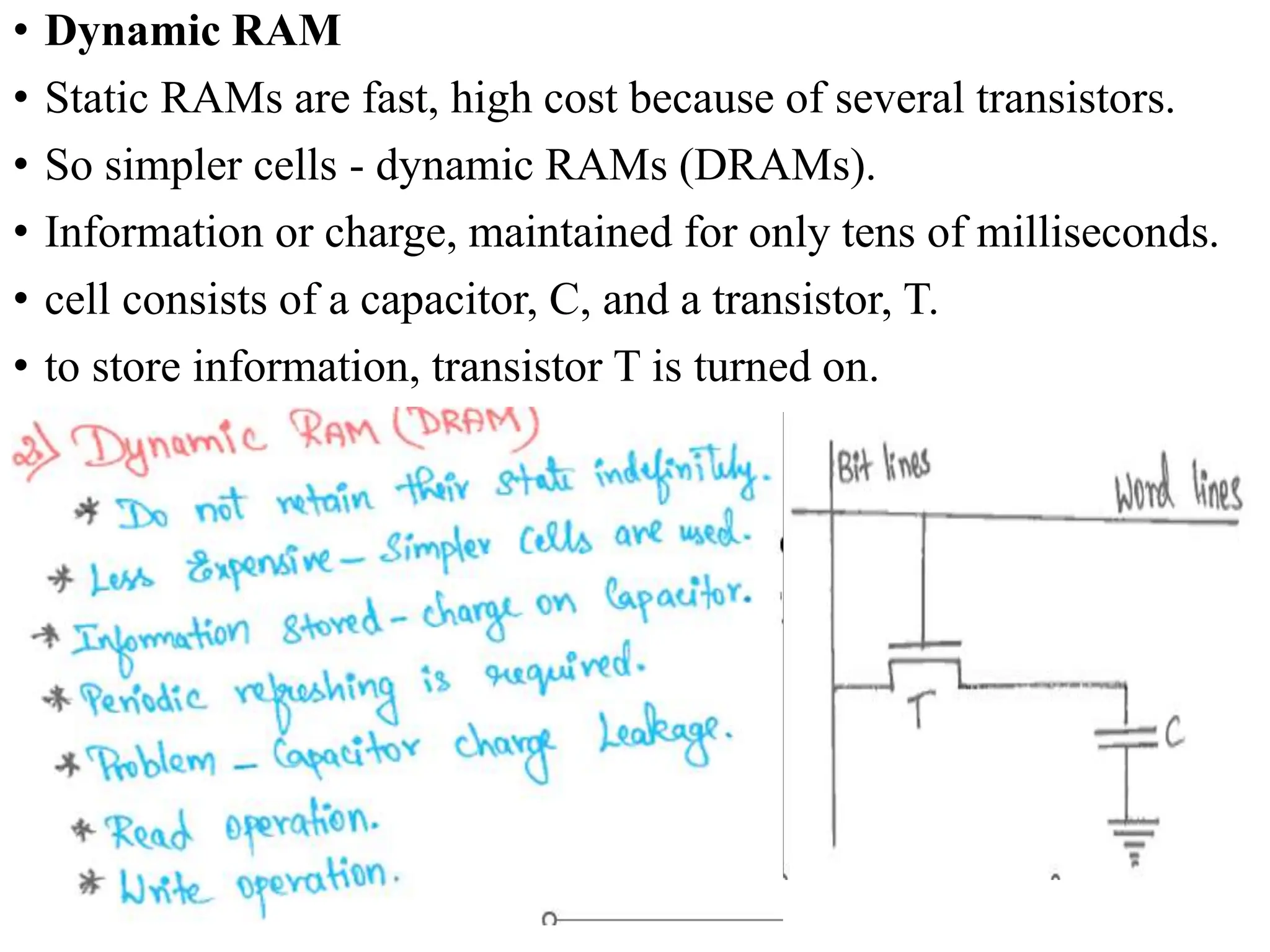

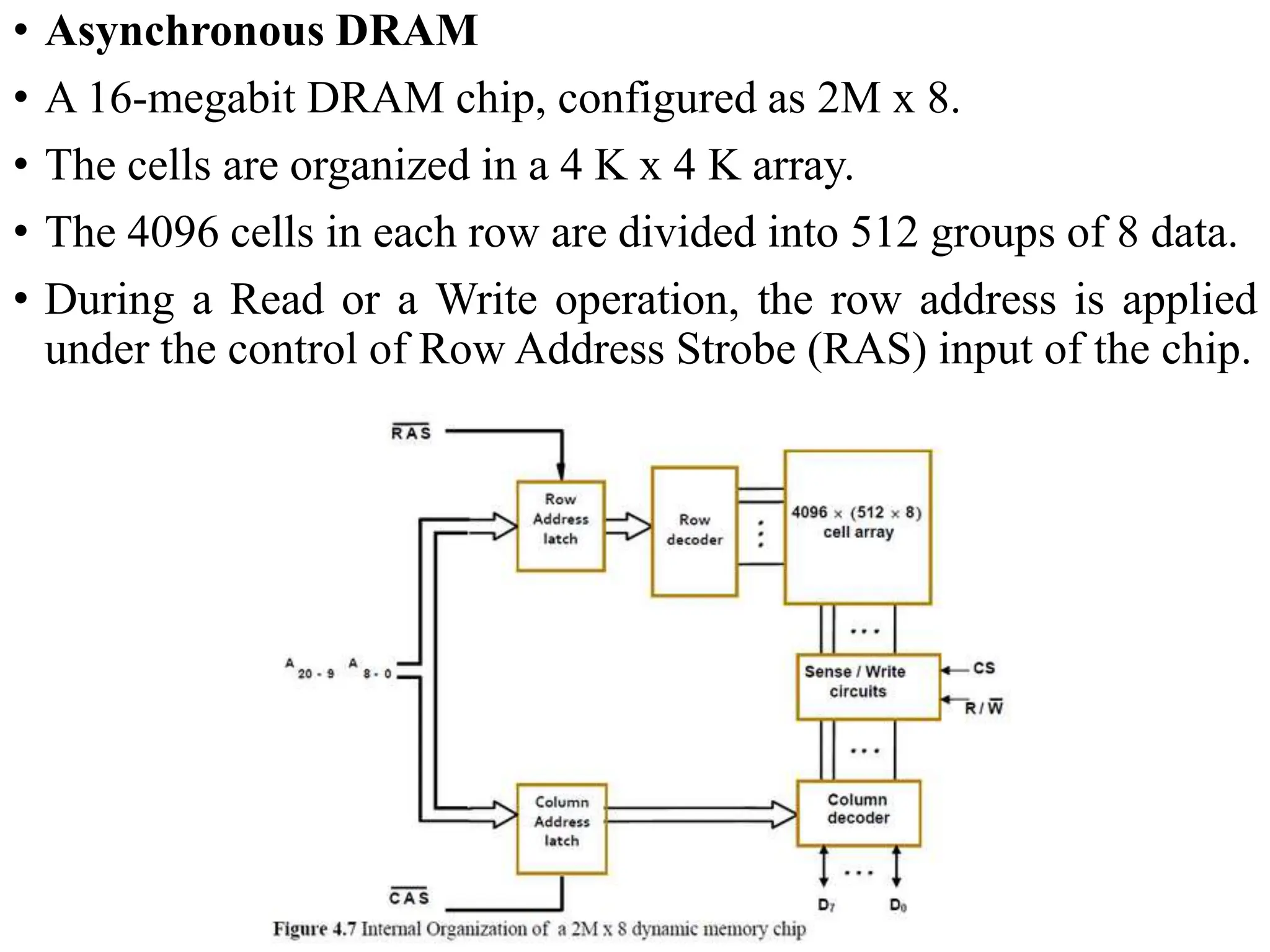

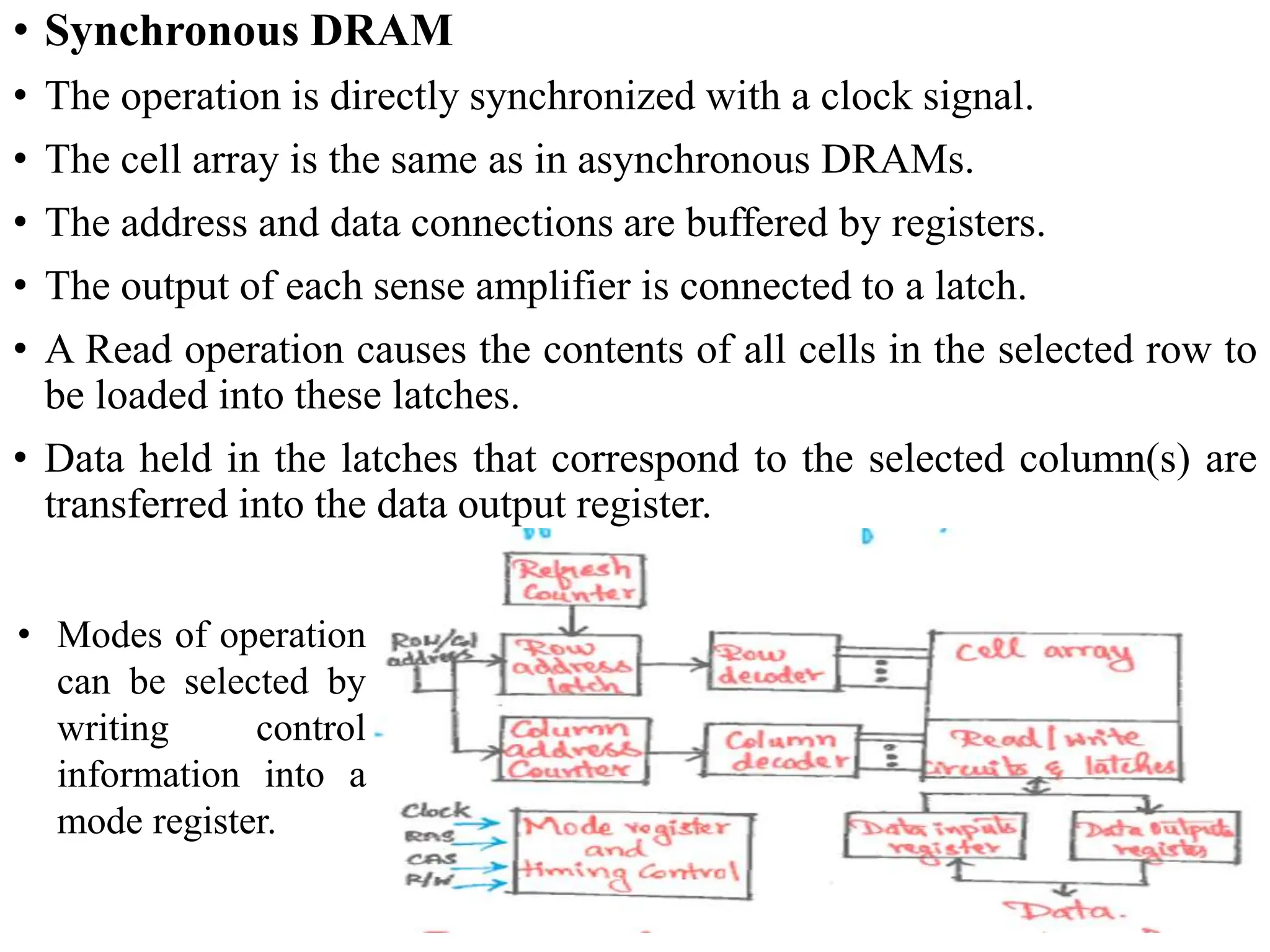

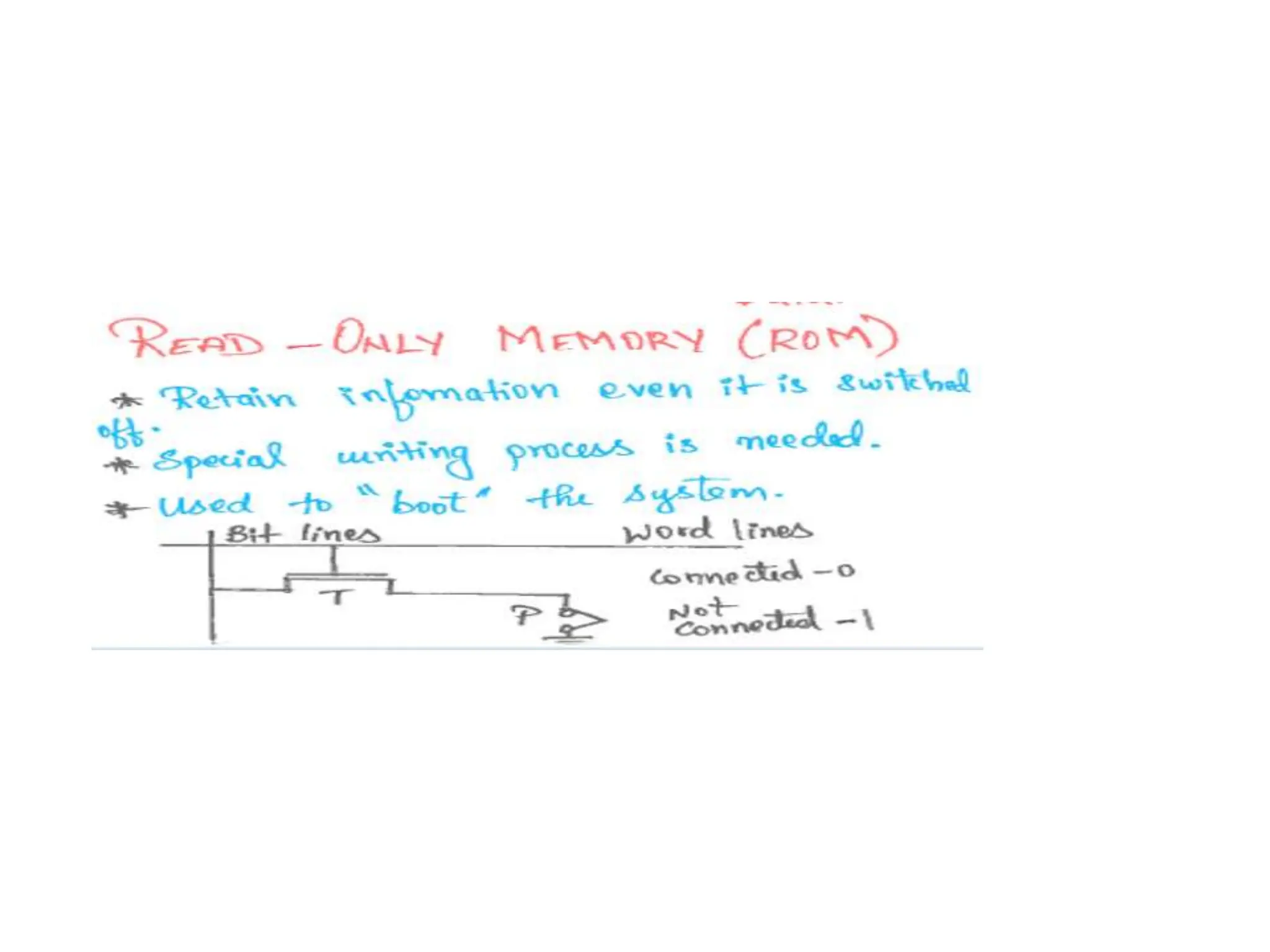

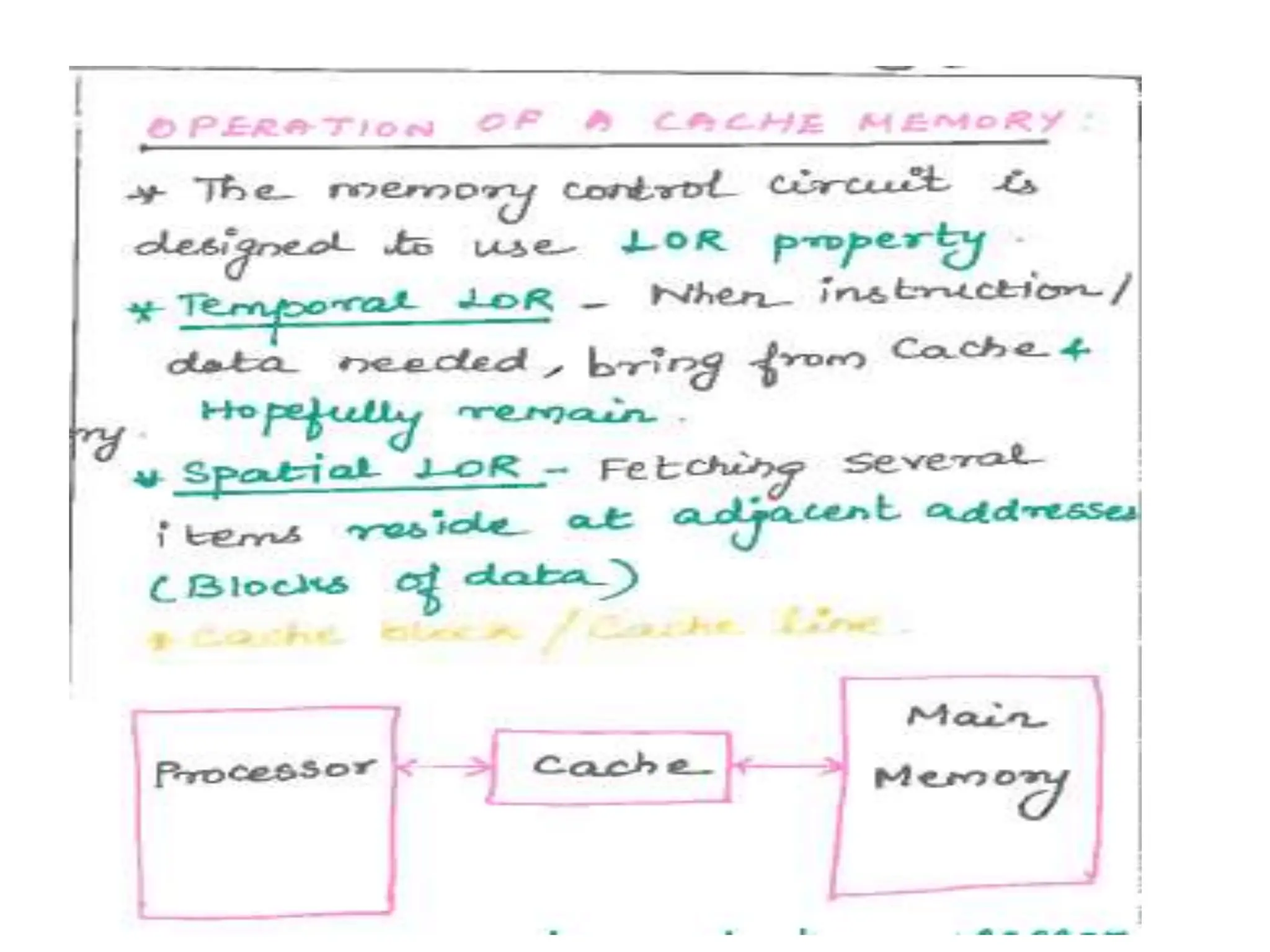

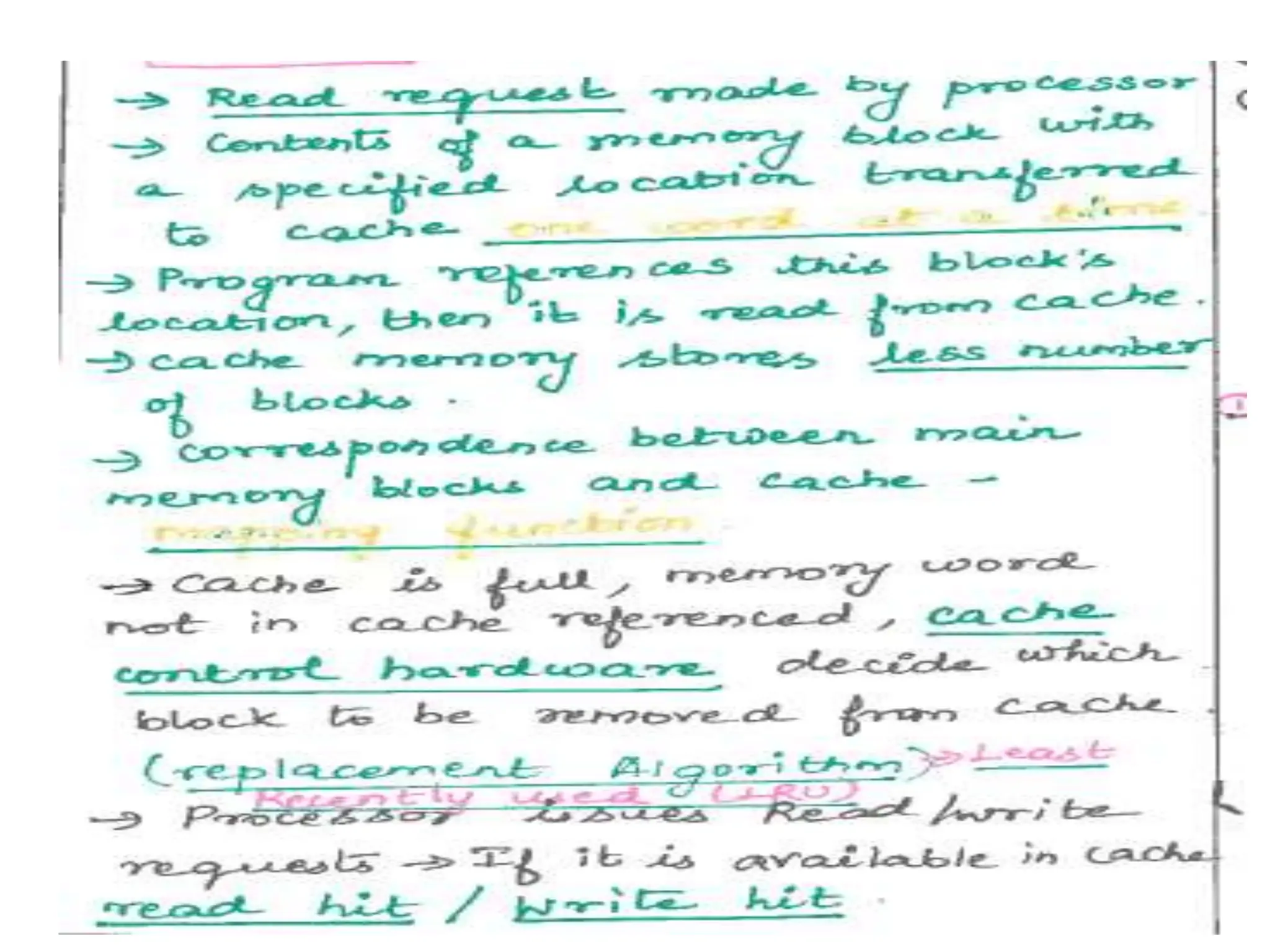

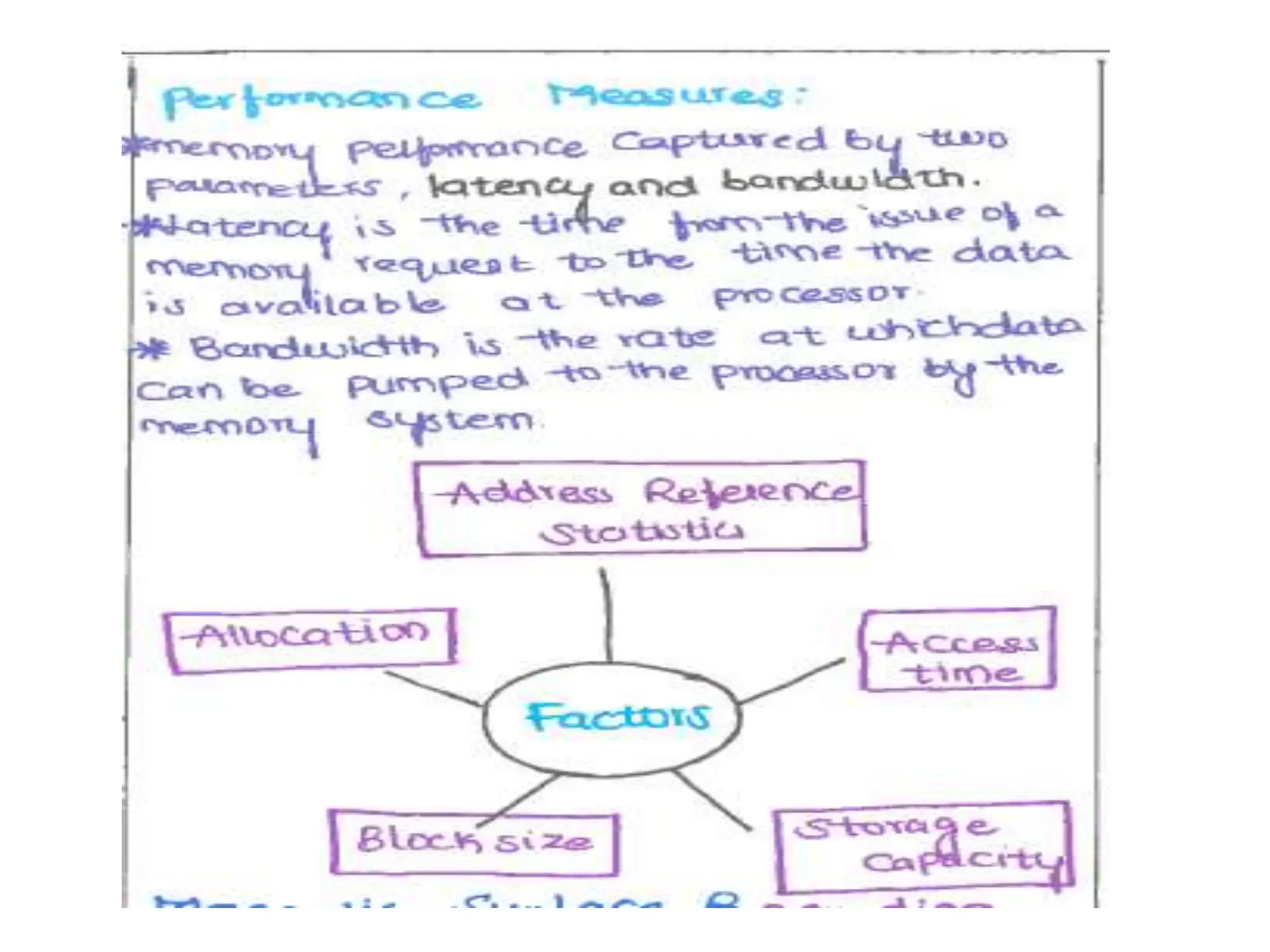

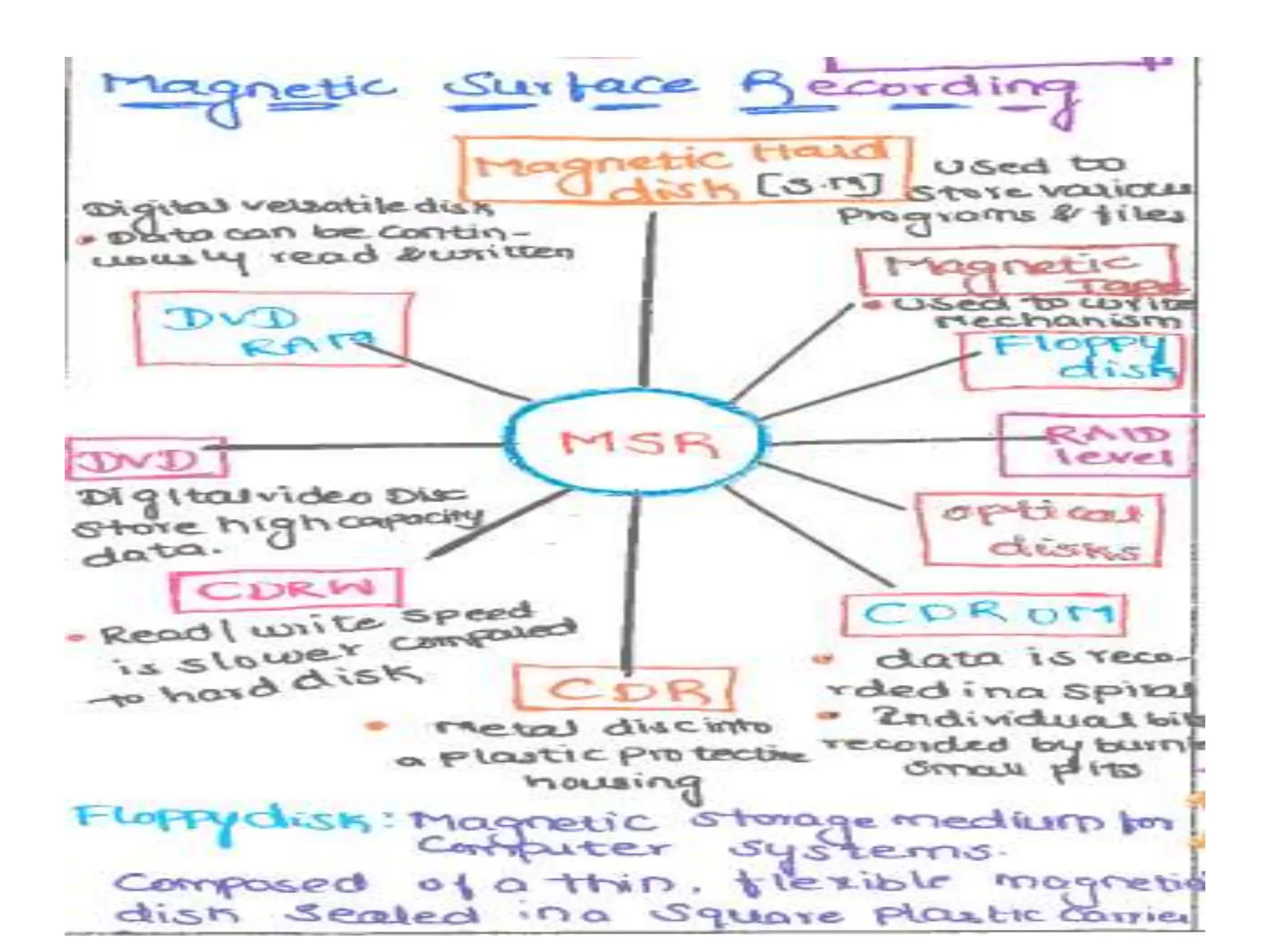

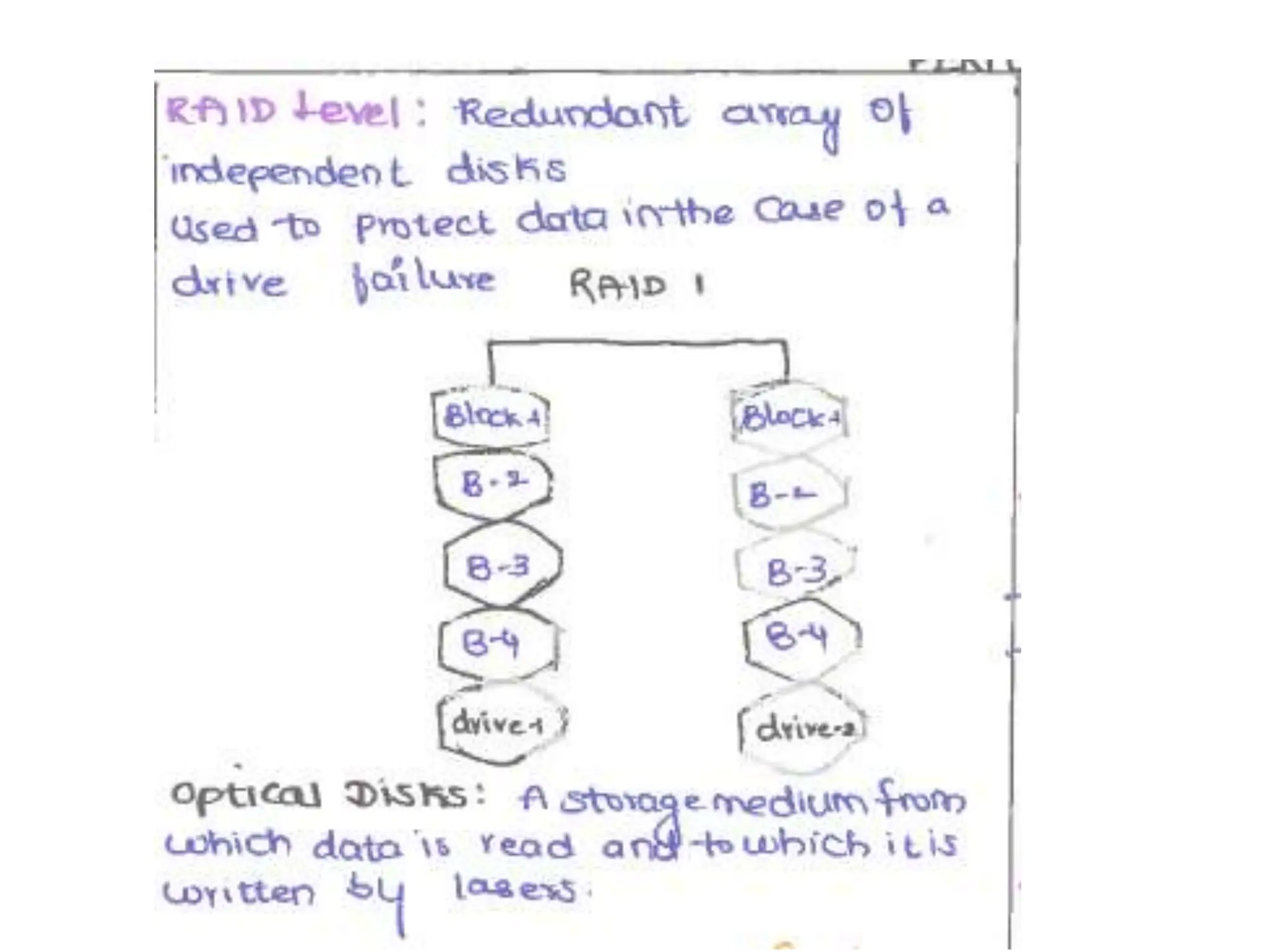

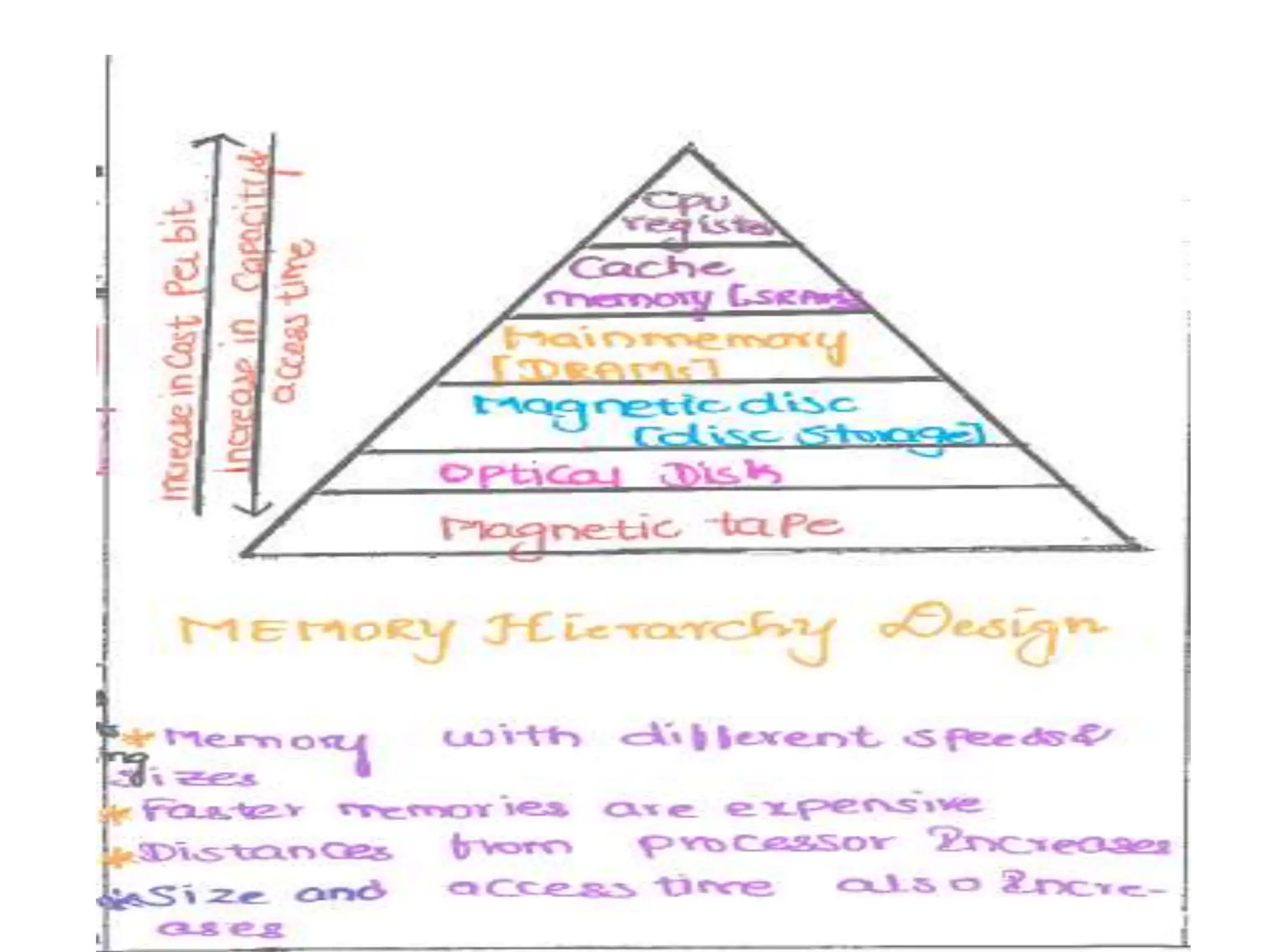

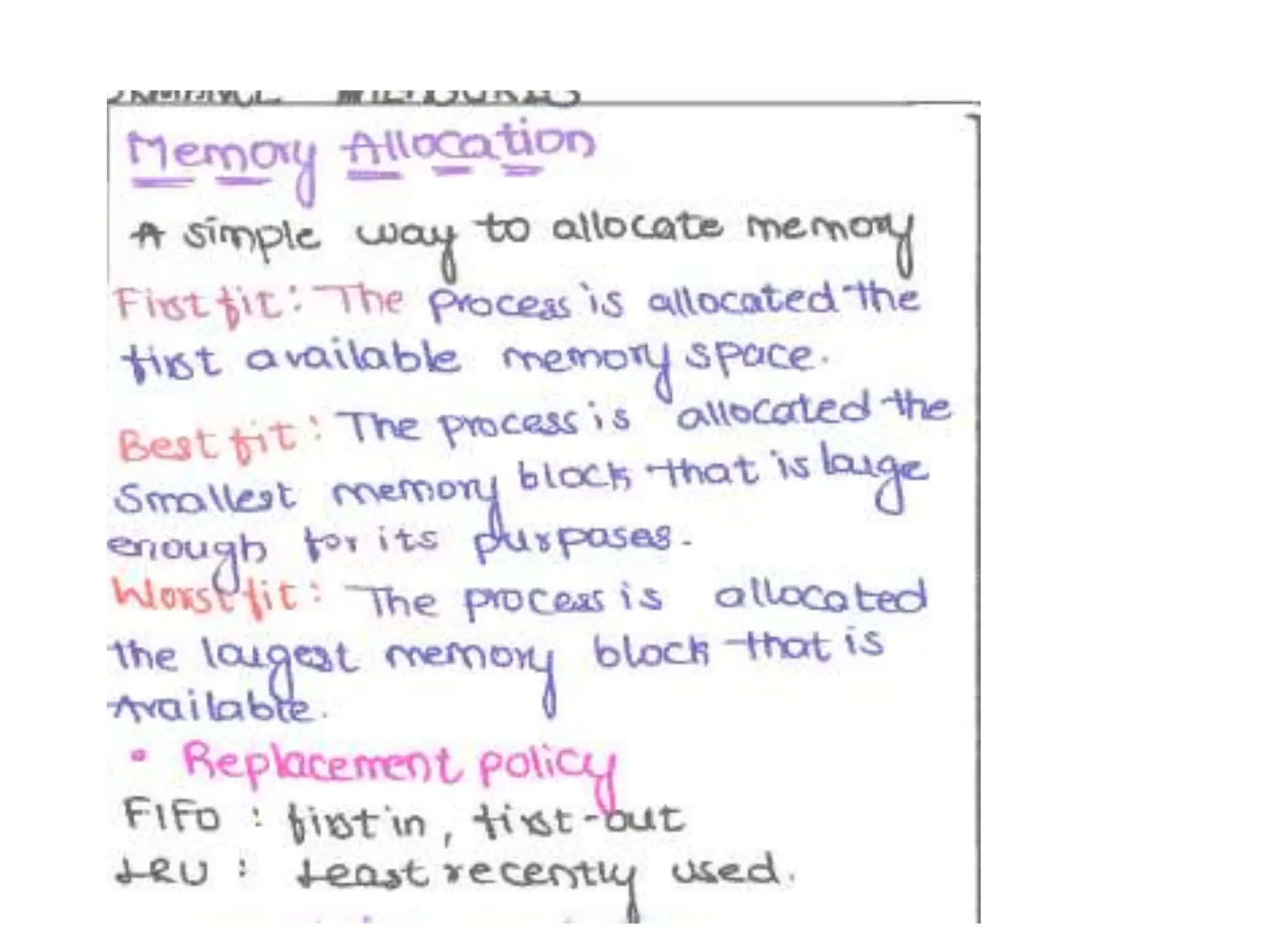

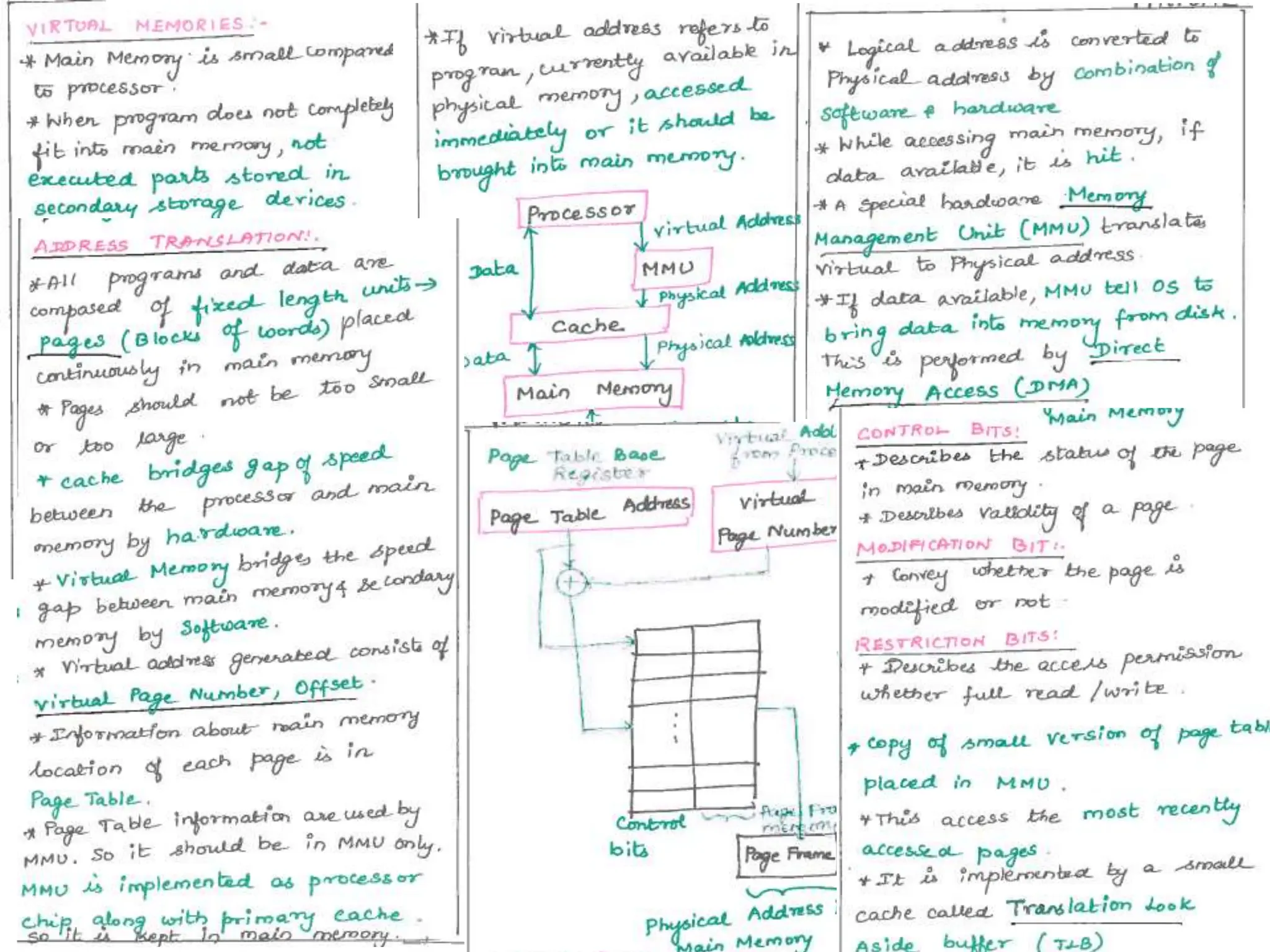

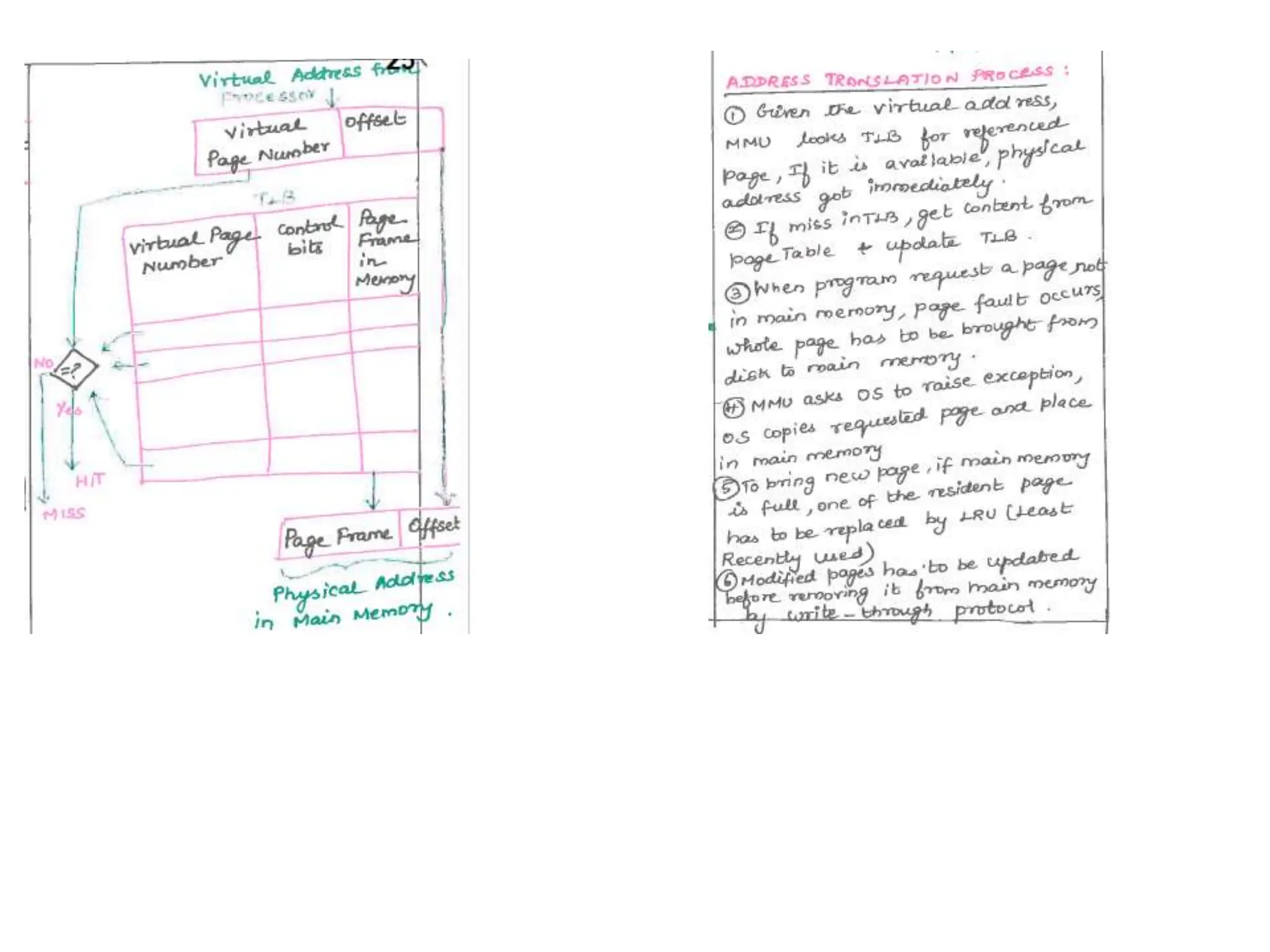

The document discusses different types of computer memory. It begins by introducing random access memory (RAM) and read-only memory (ROM). It then discusses performance measures of memory and requirements for memory management. The document outlines cache memory and virtual memory. It describes various memory technologies like magnetic, optical, and multilevel memories. It provides details on RAM, including static and dynamic RAM. It explains the organization and operation of different types of DRAM like asynchronous and synchronous DRAM.