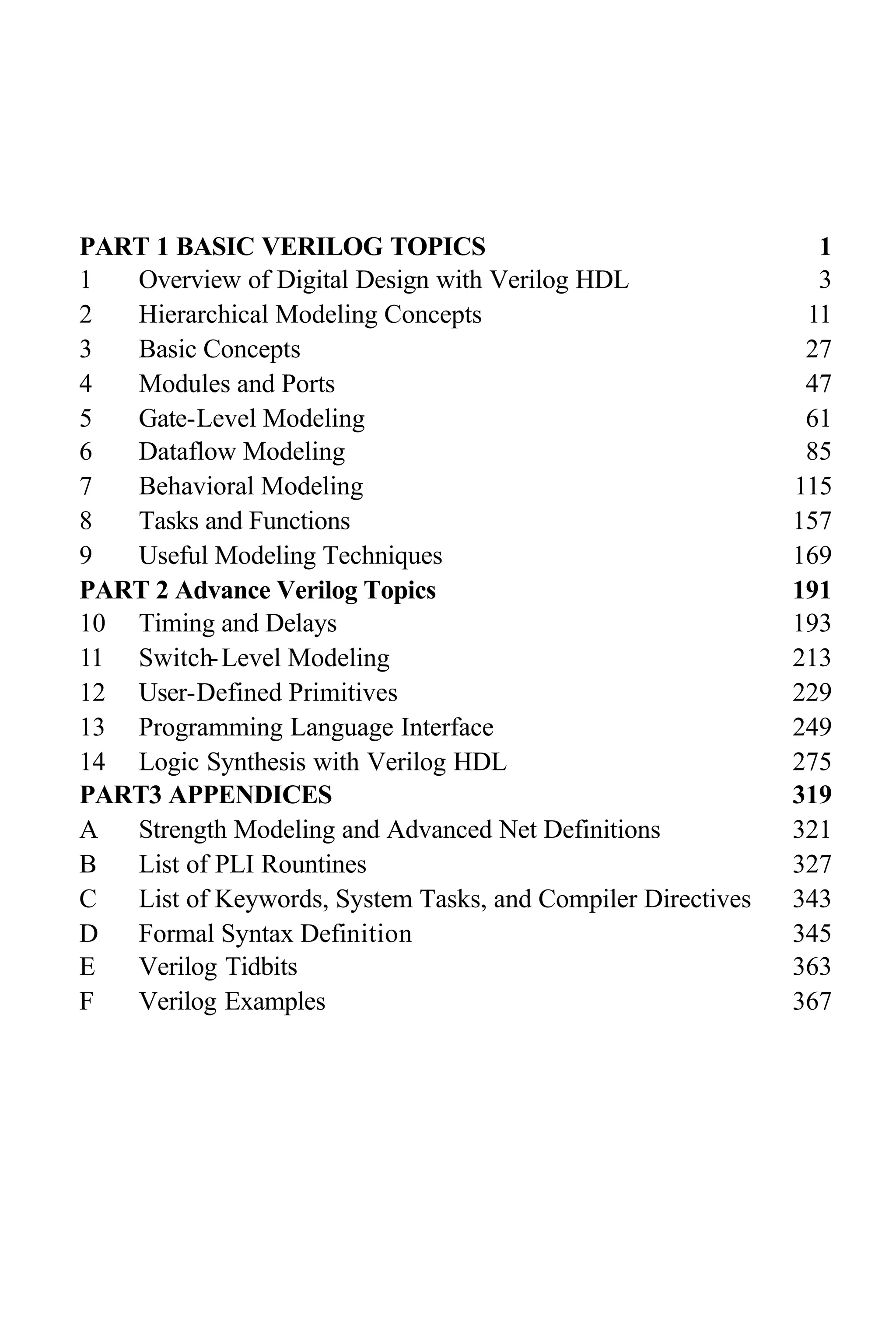

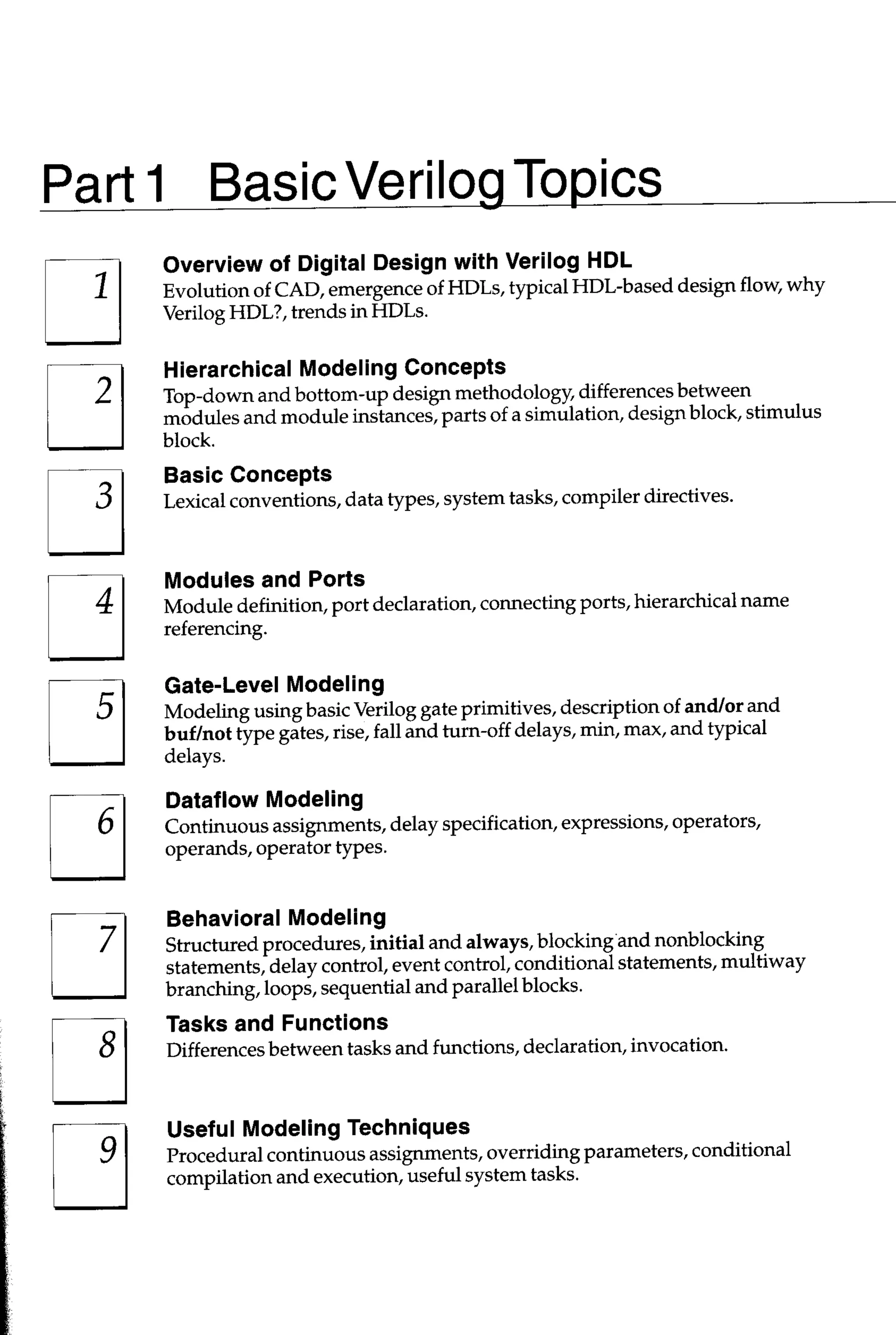

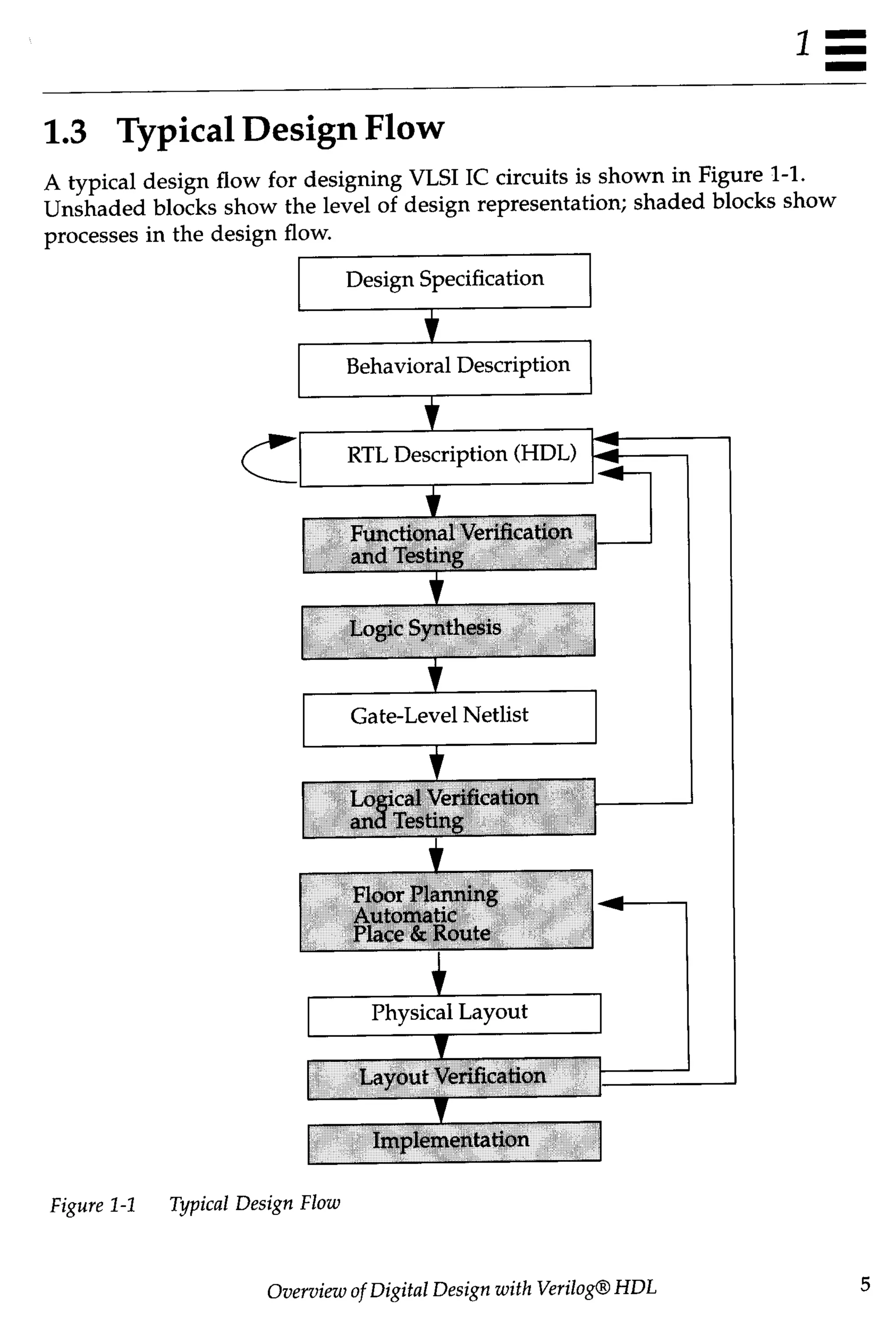

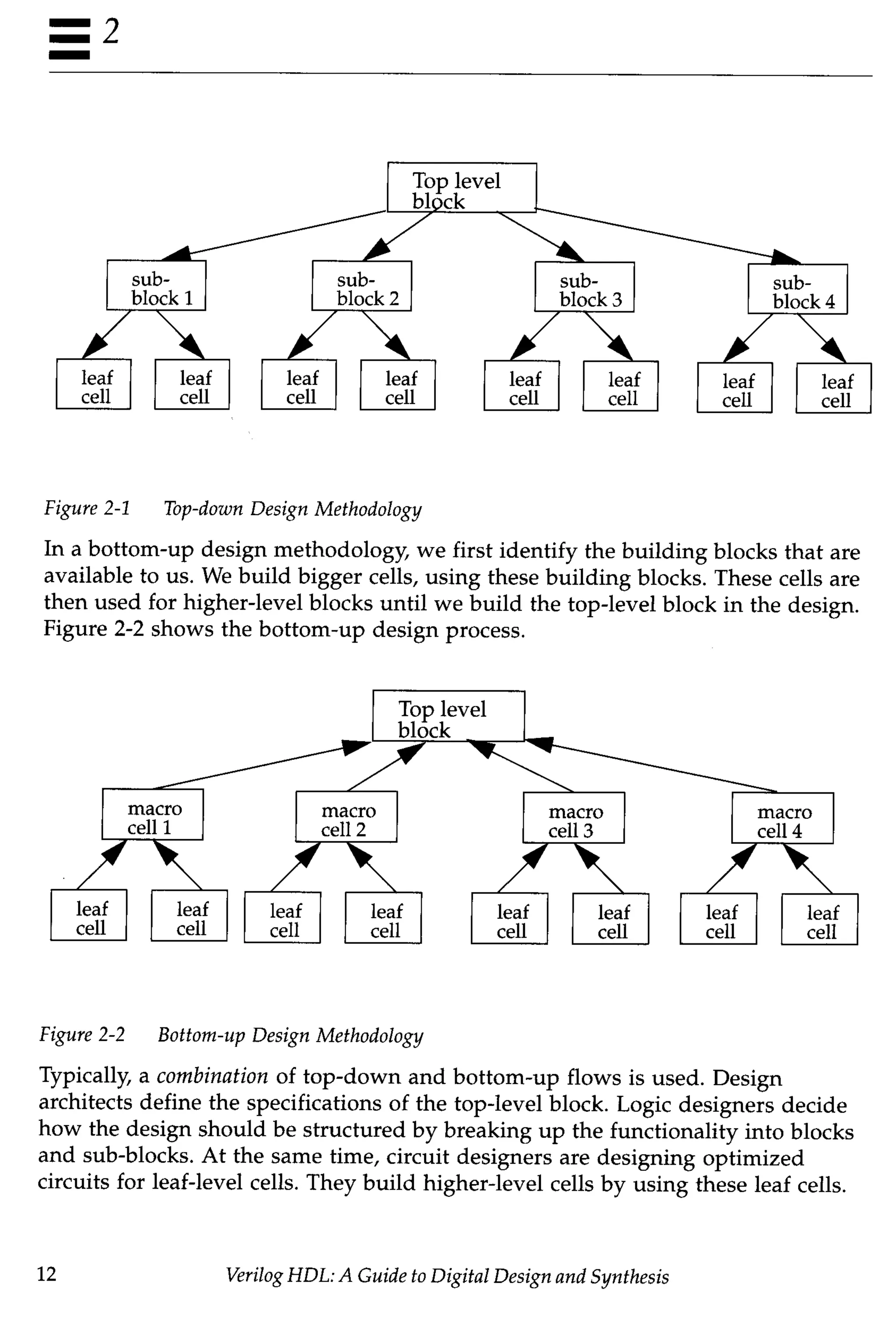

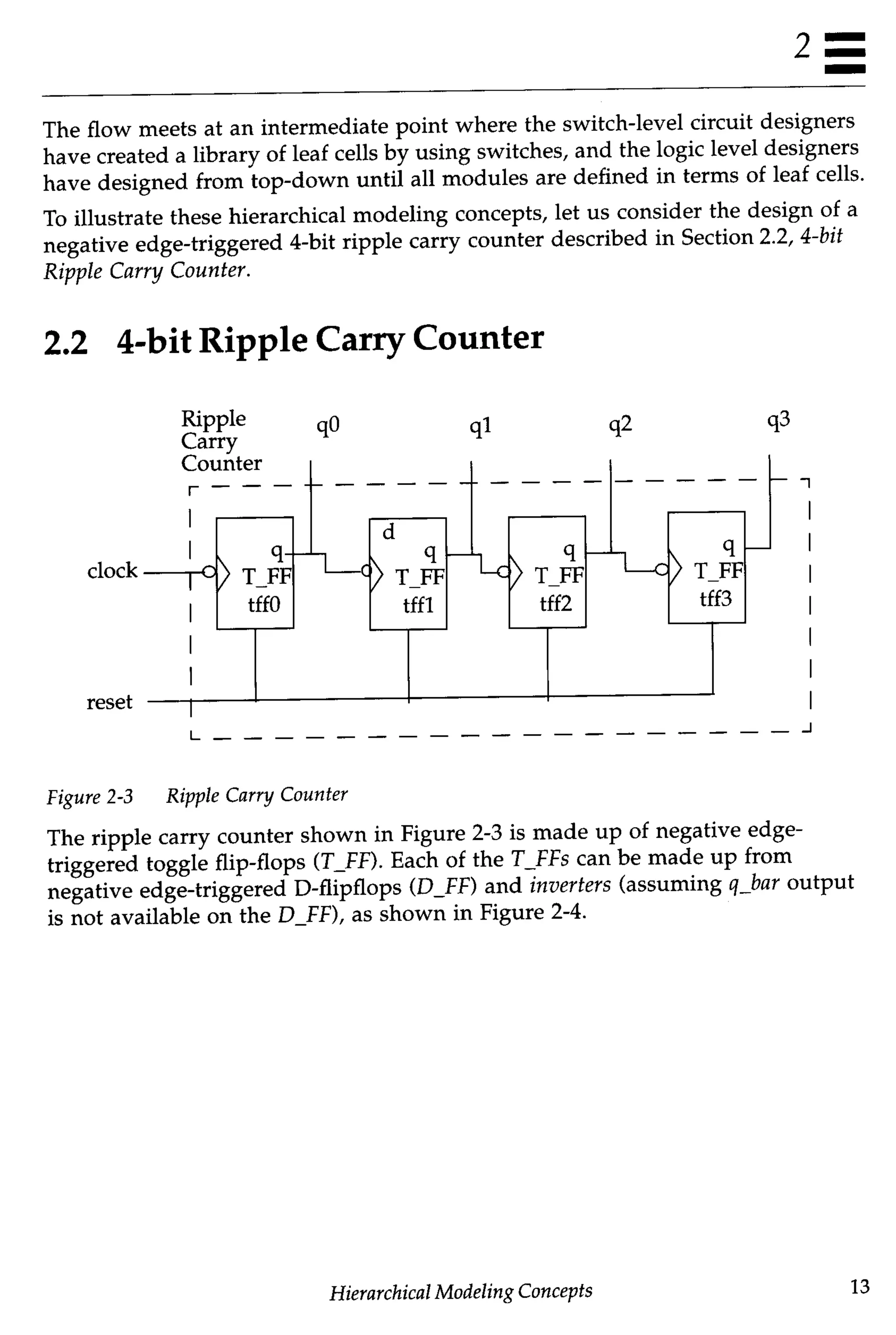

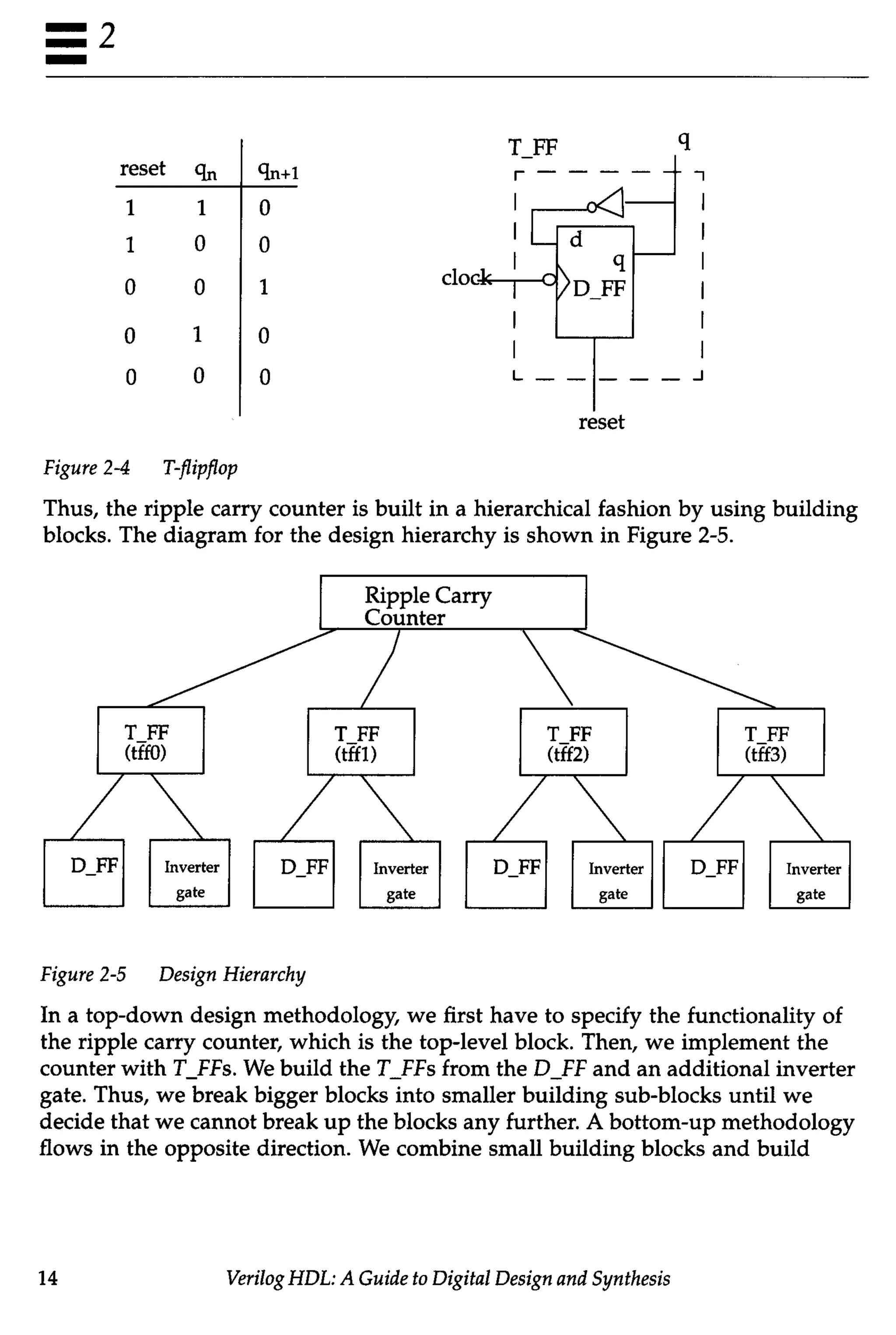

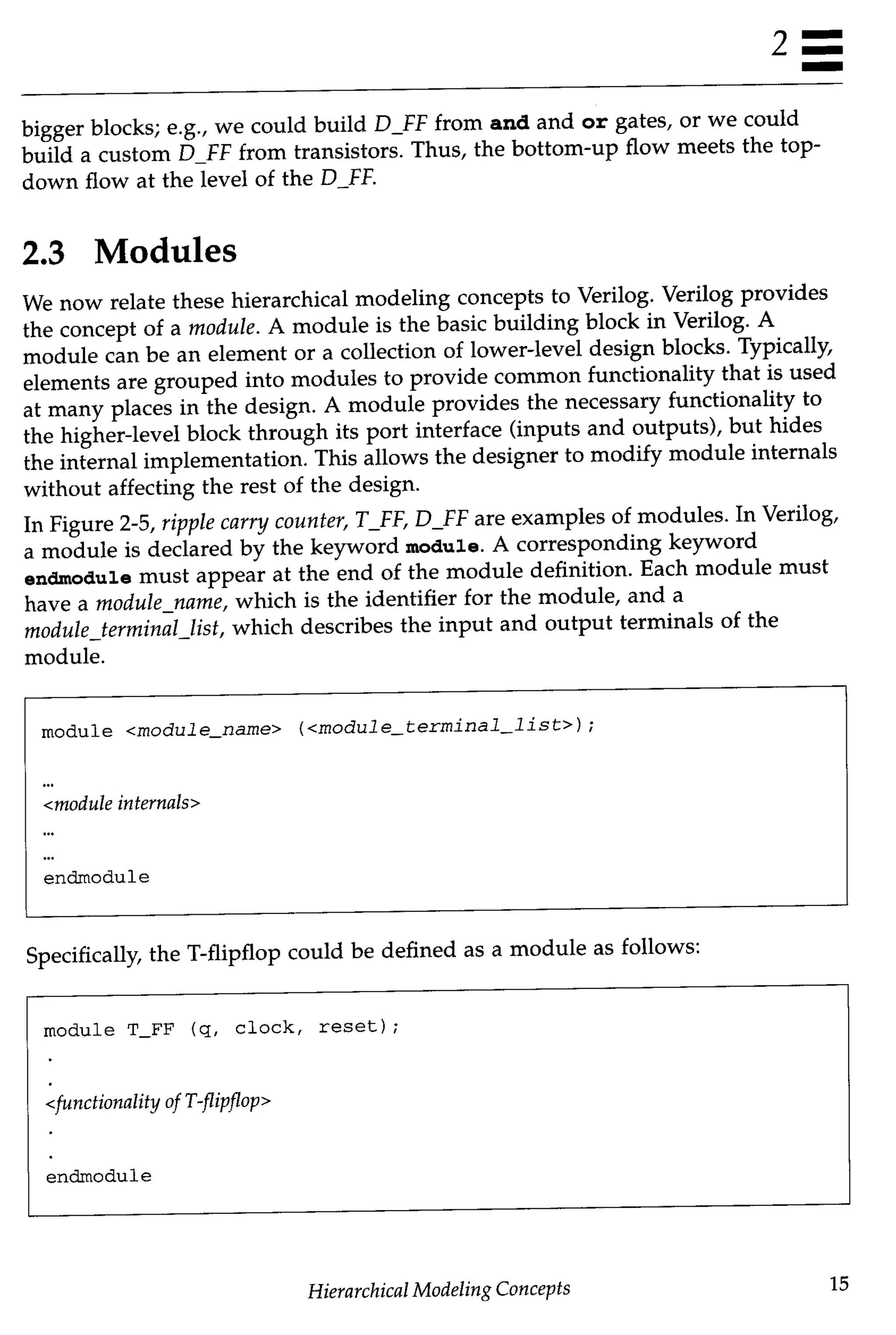

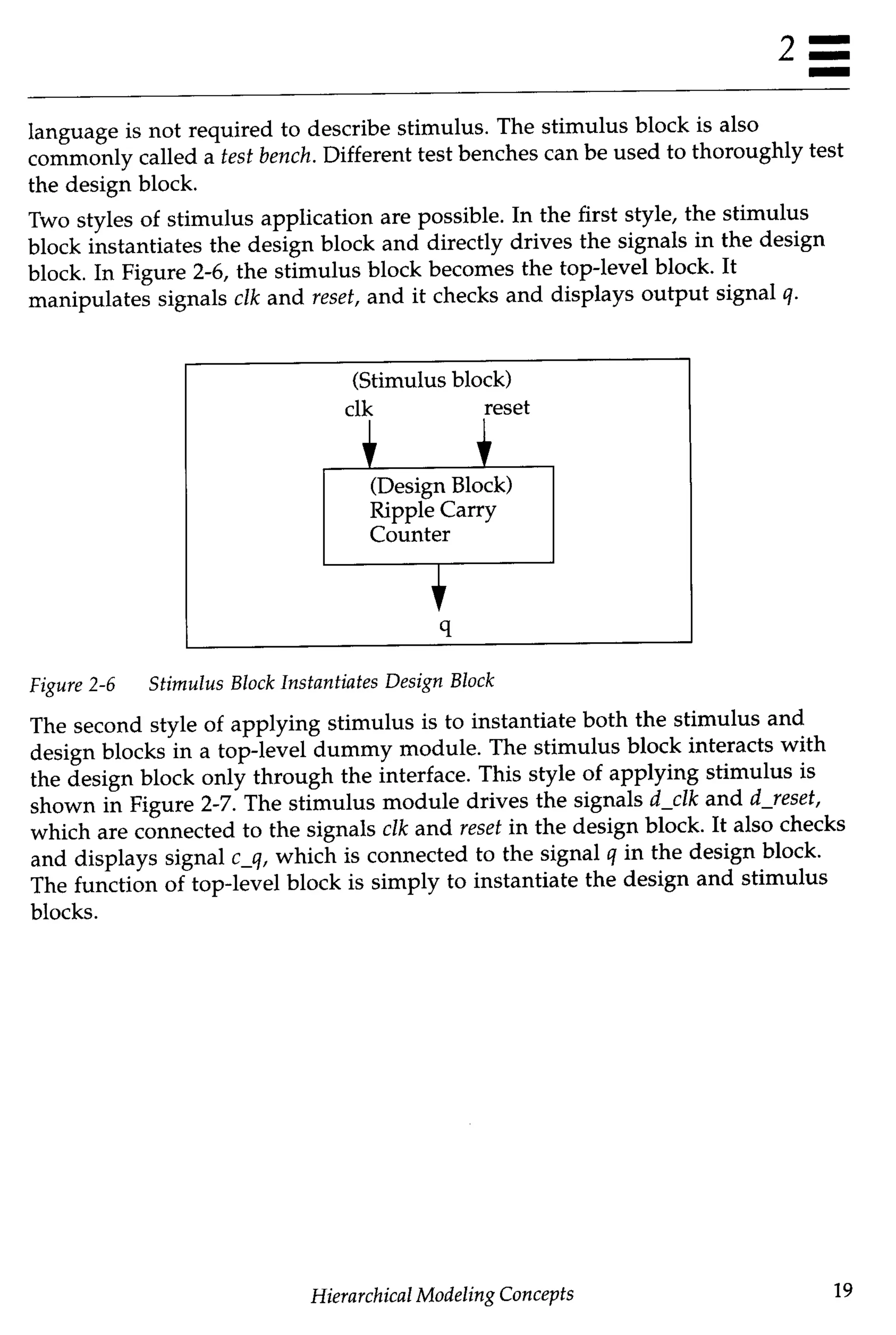

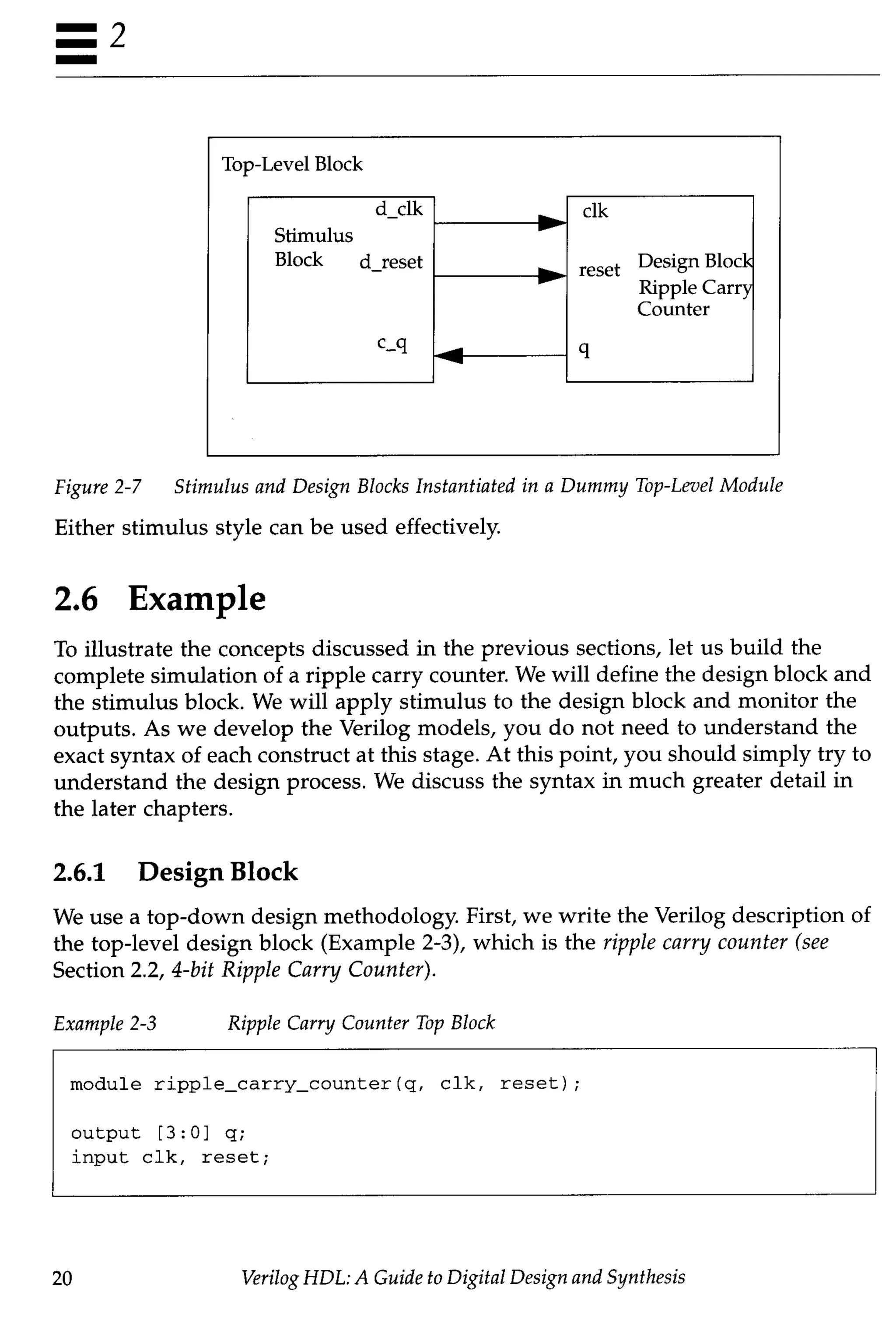

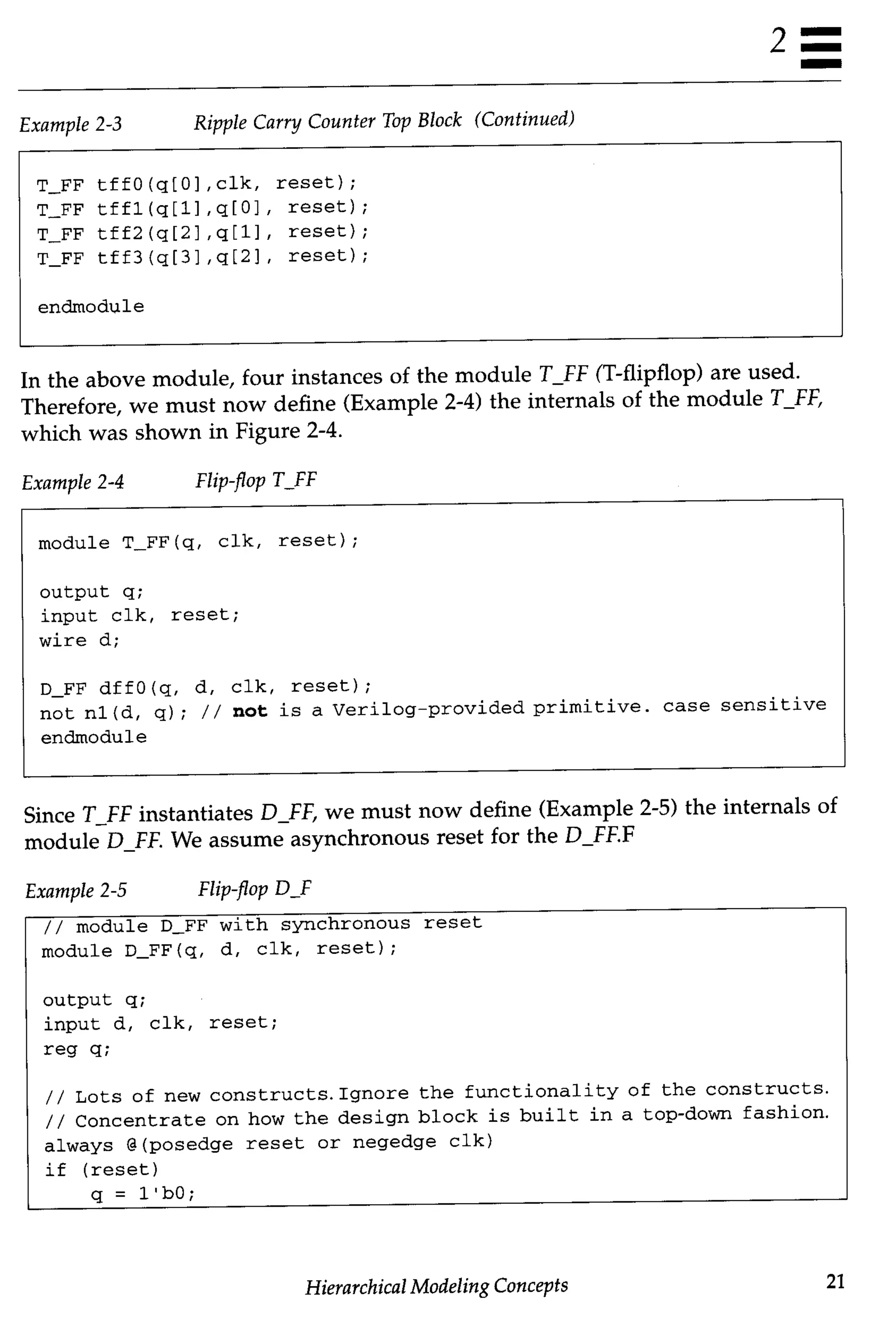

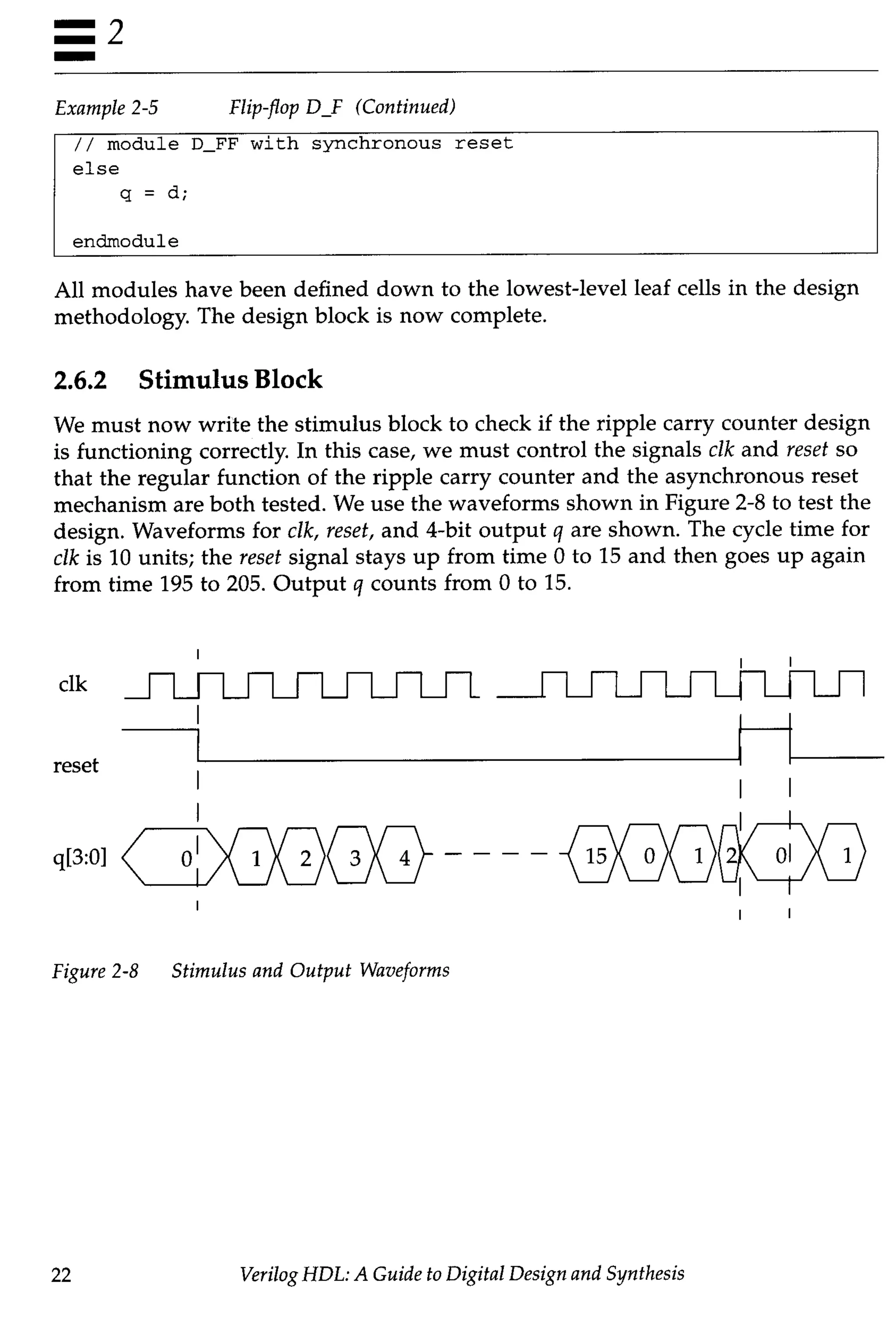

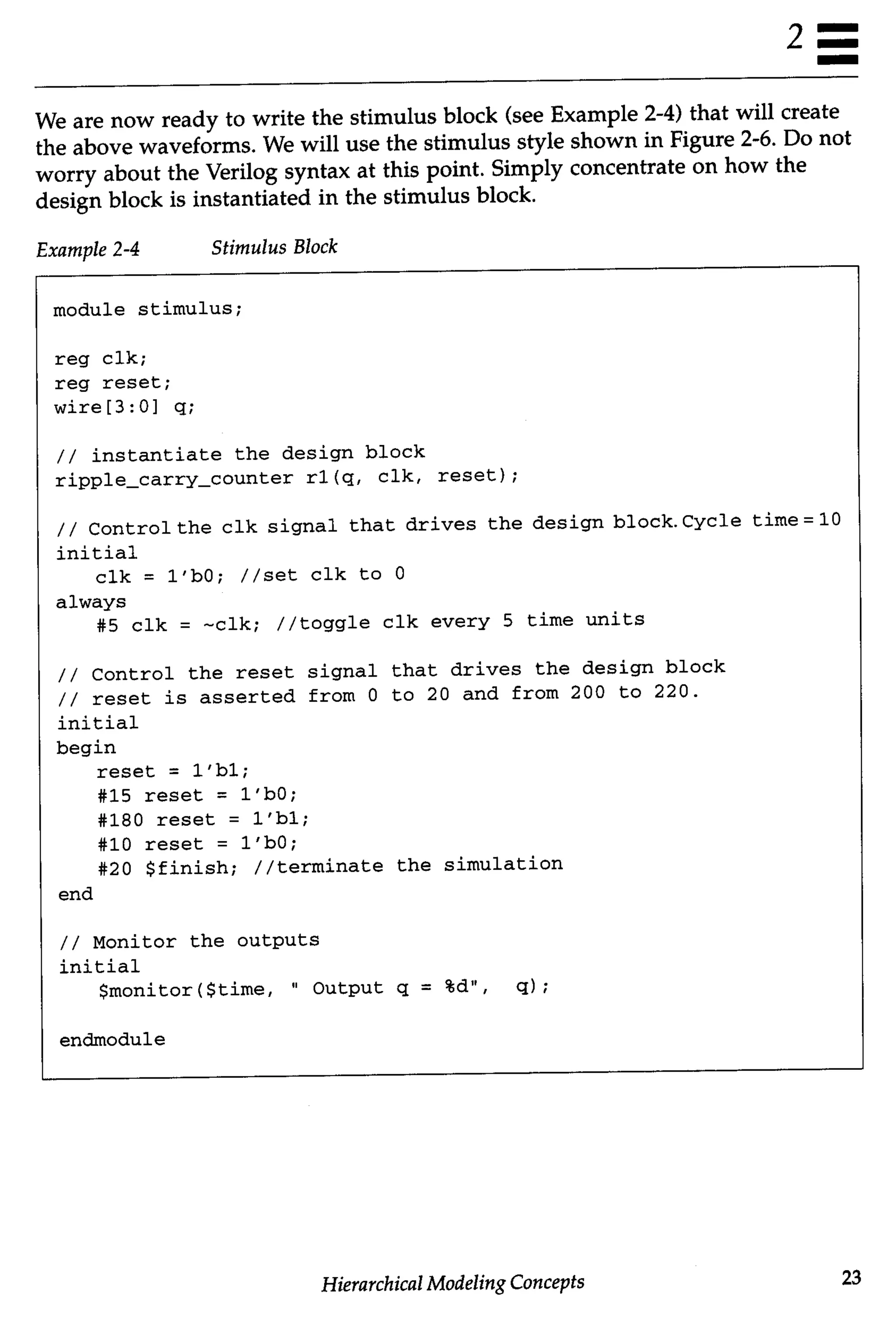

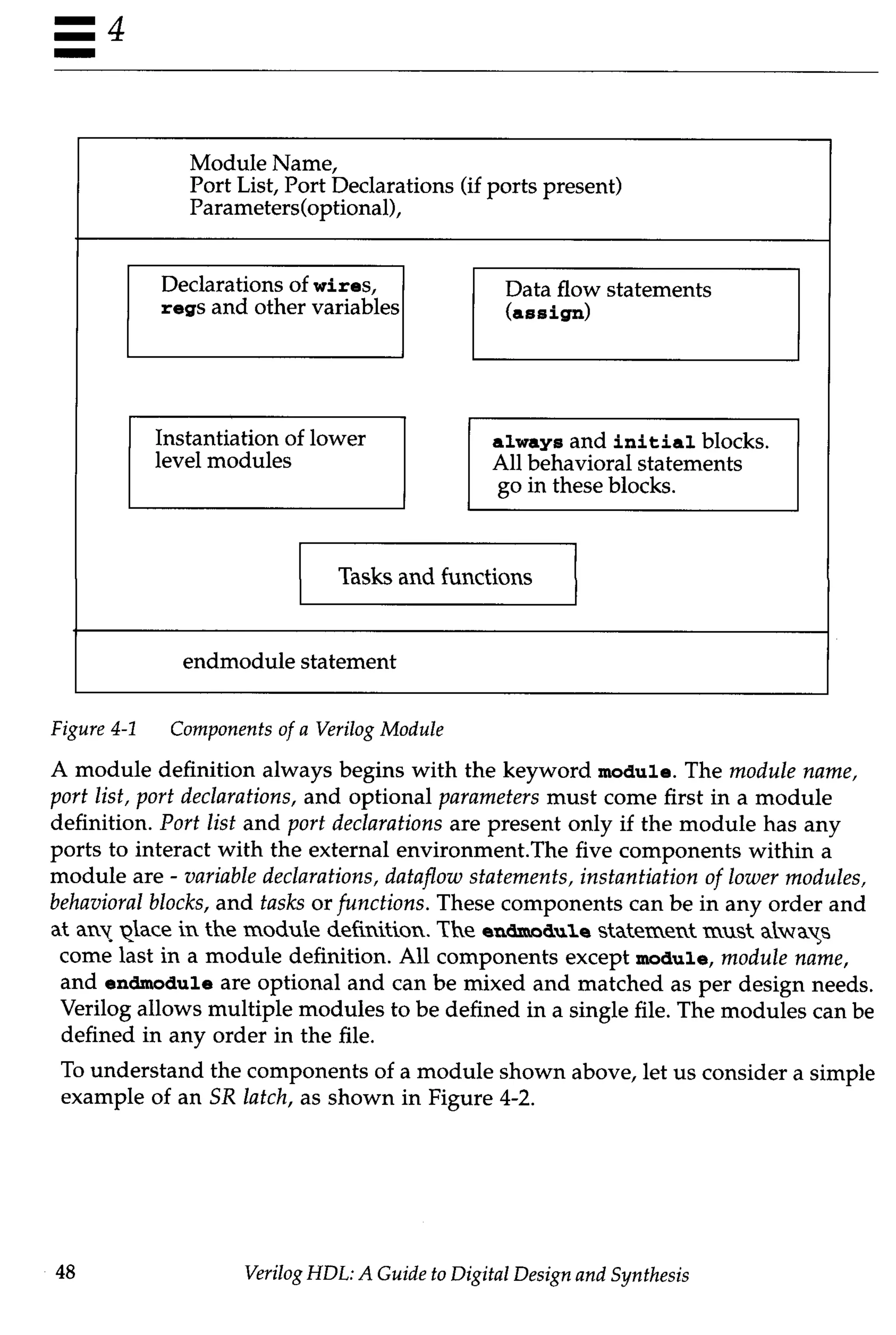

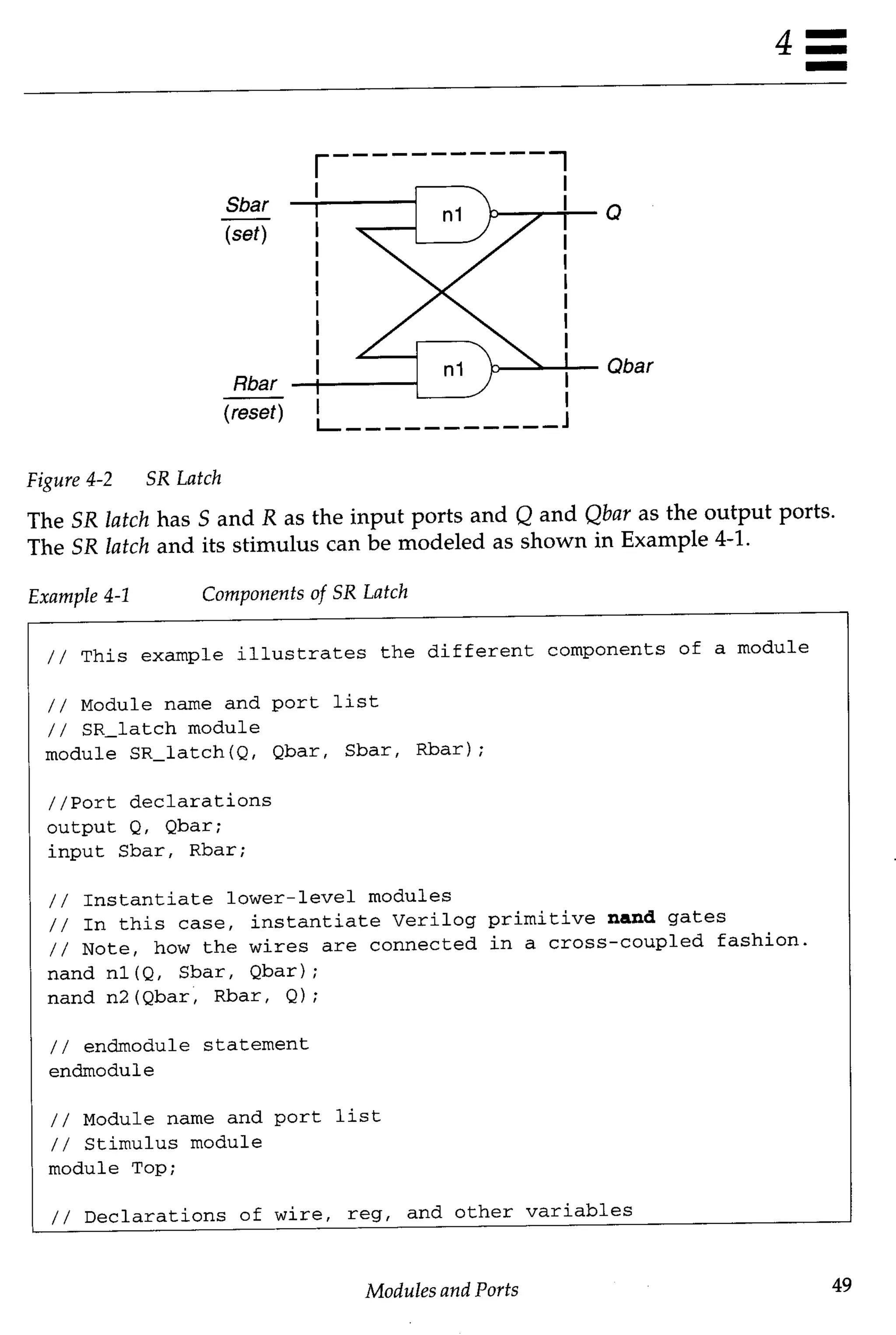

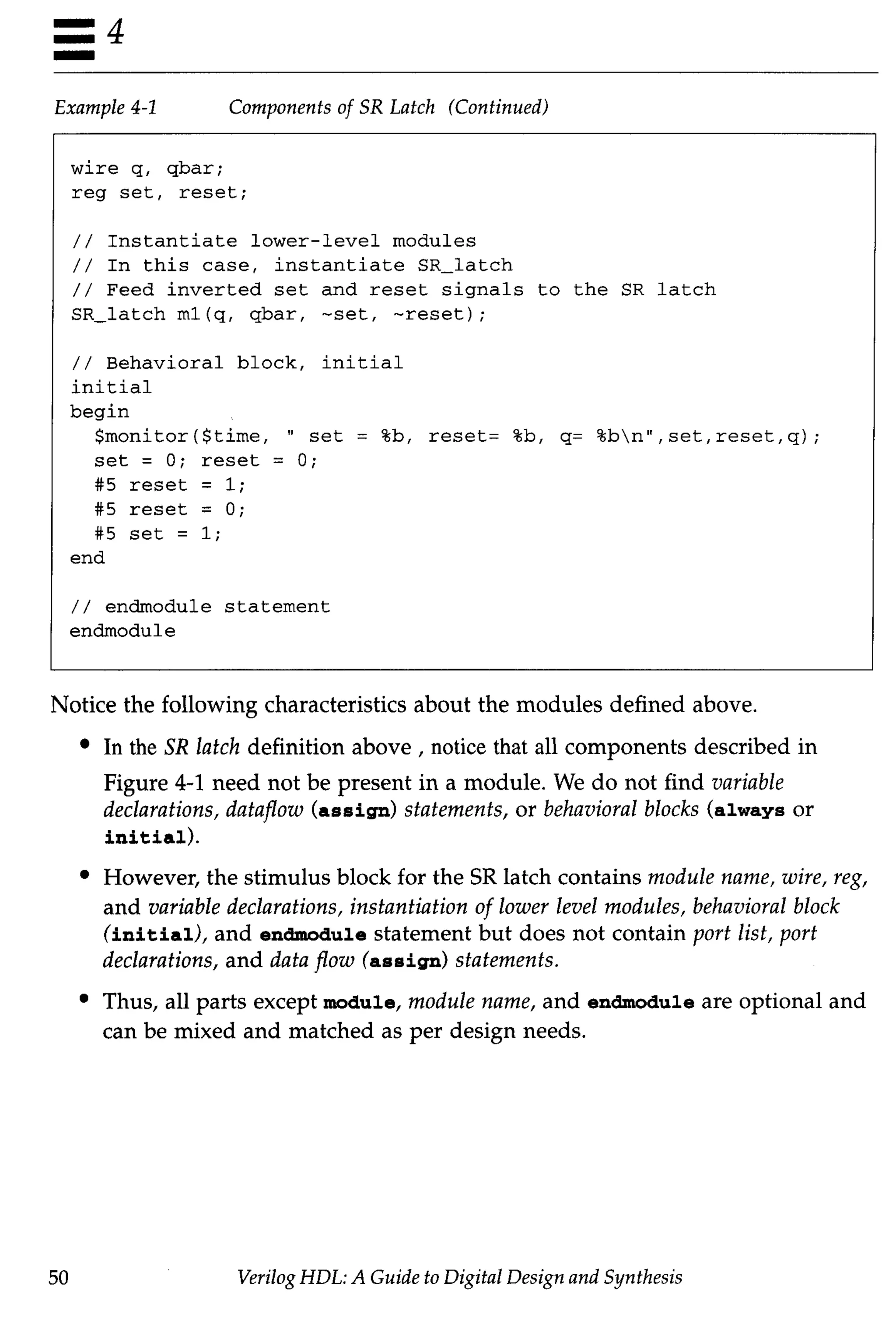

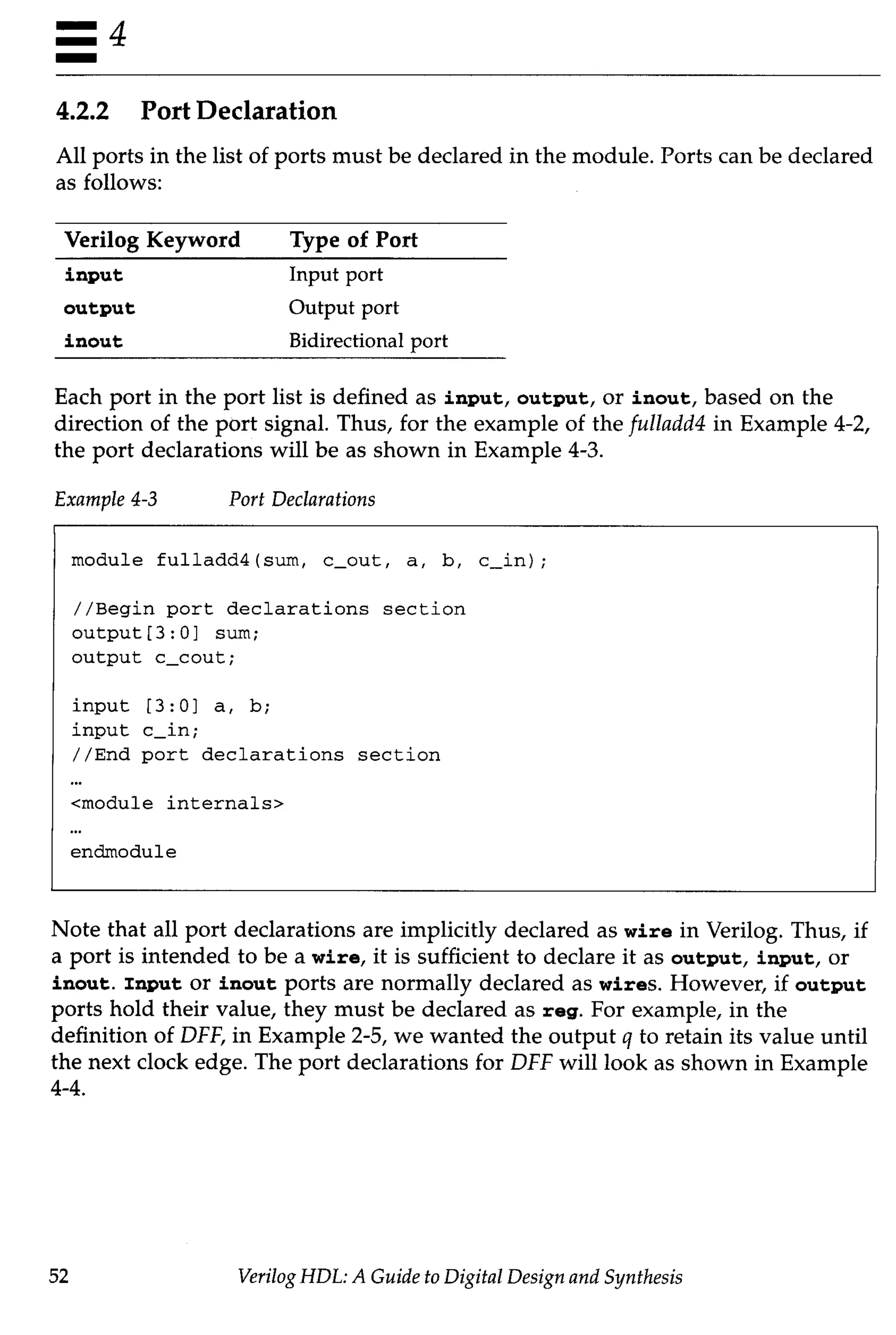

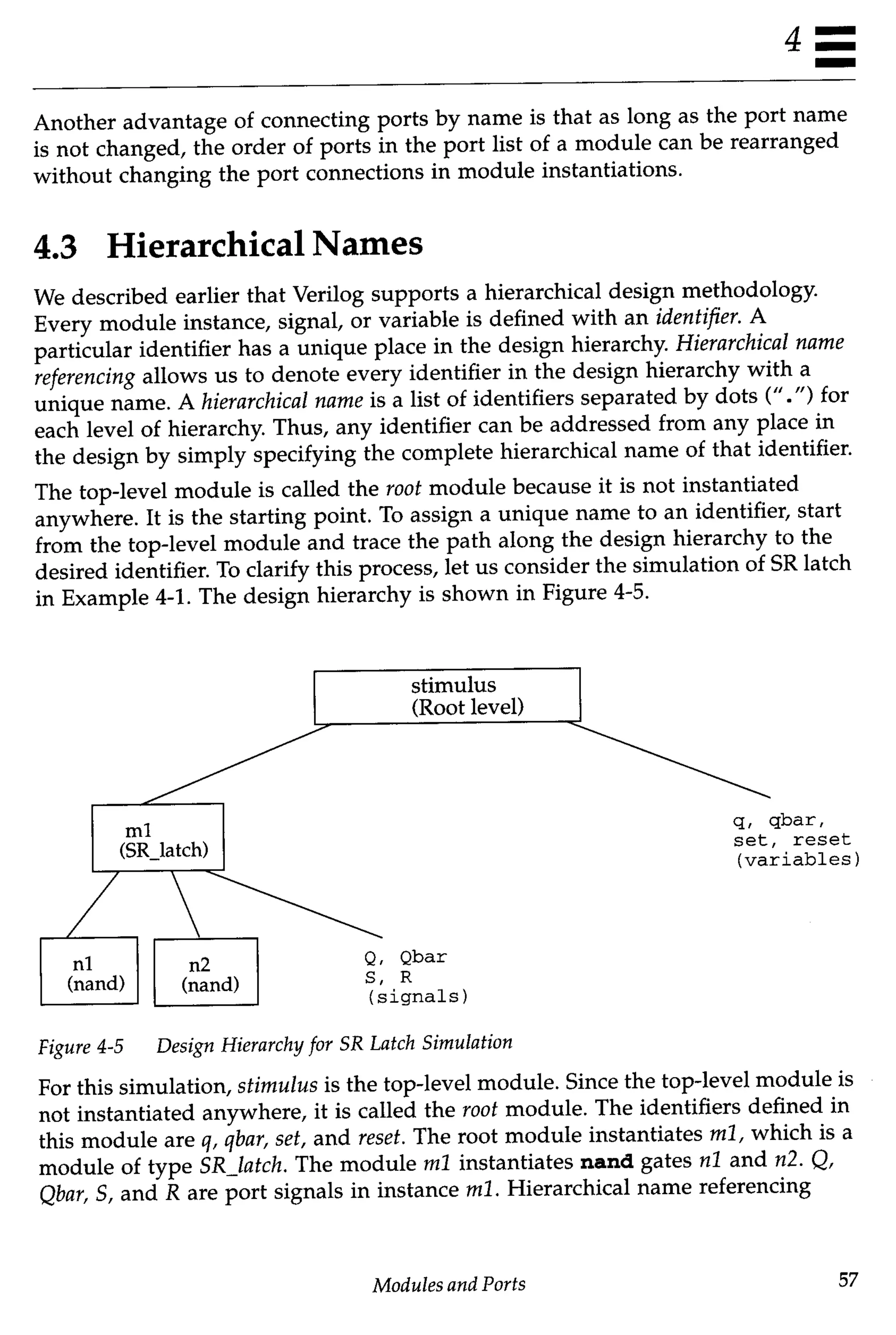

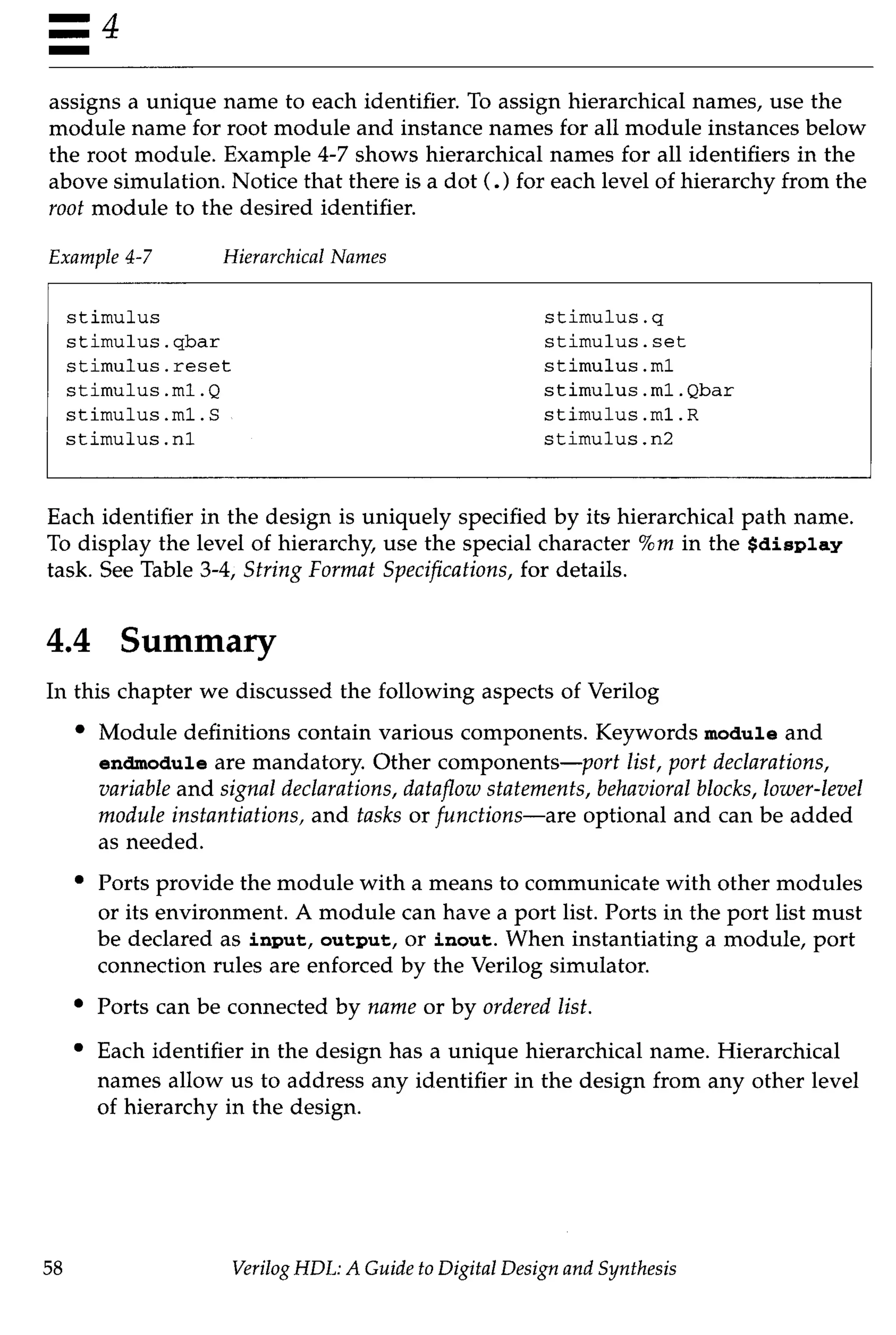

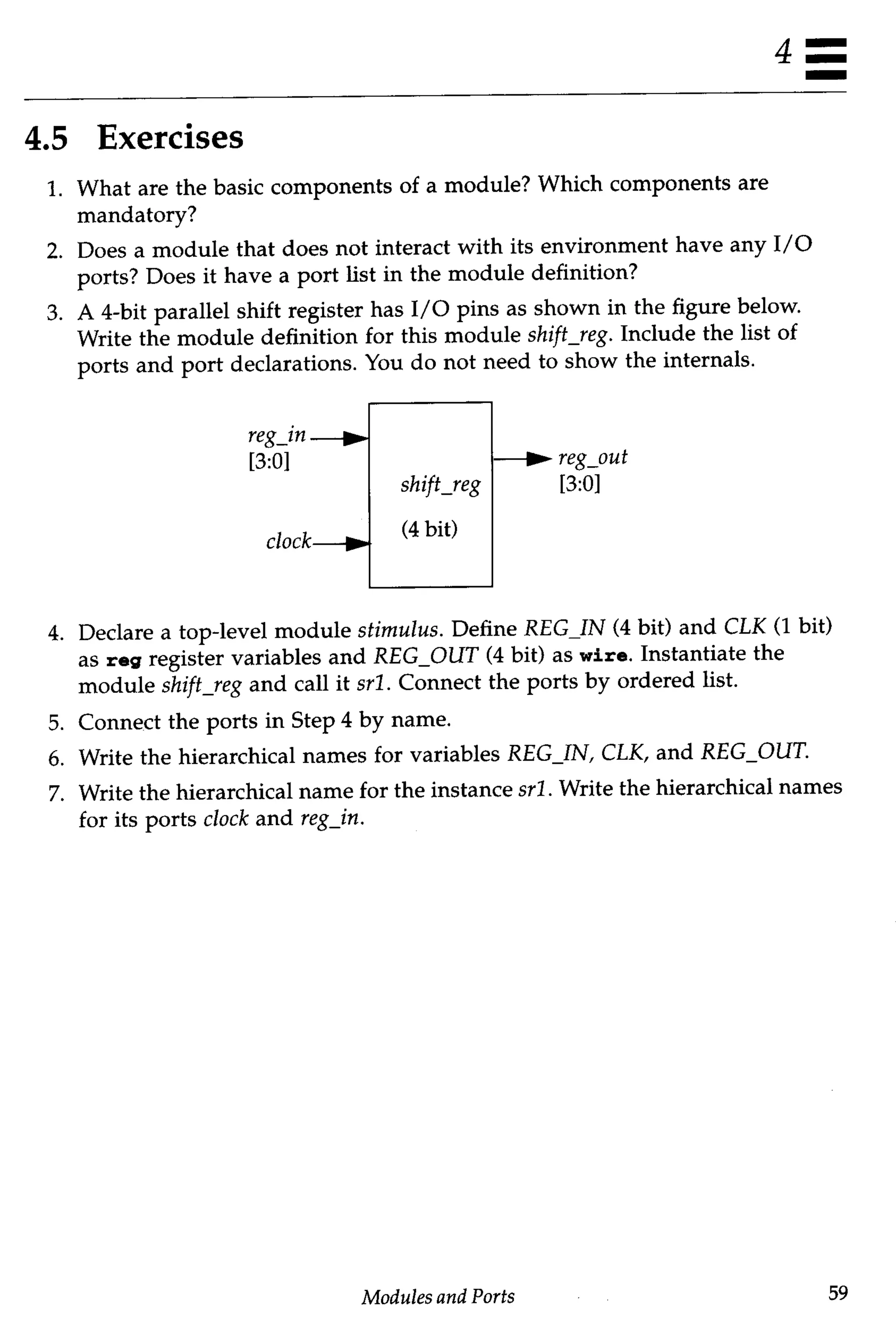

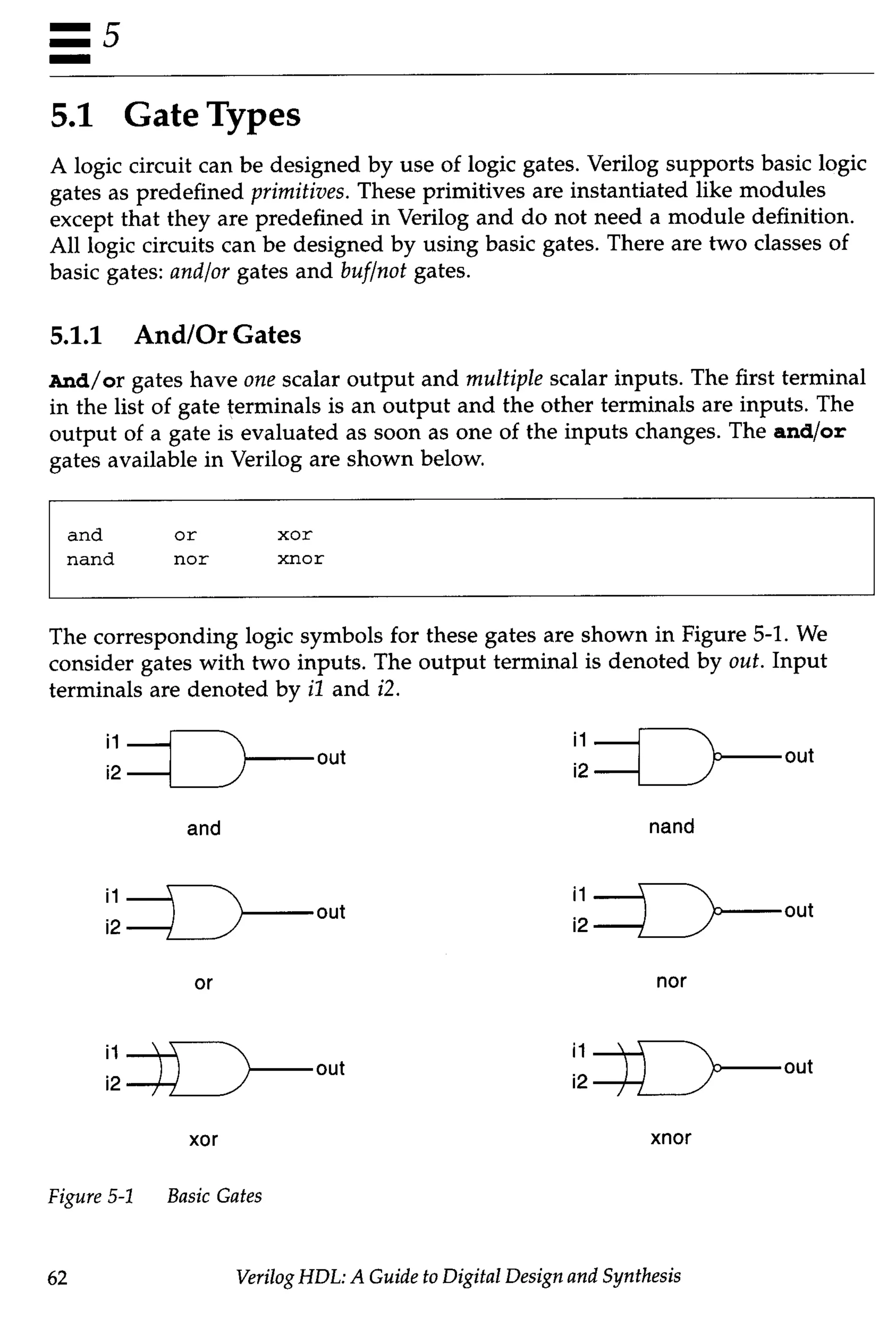

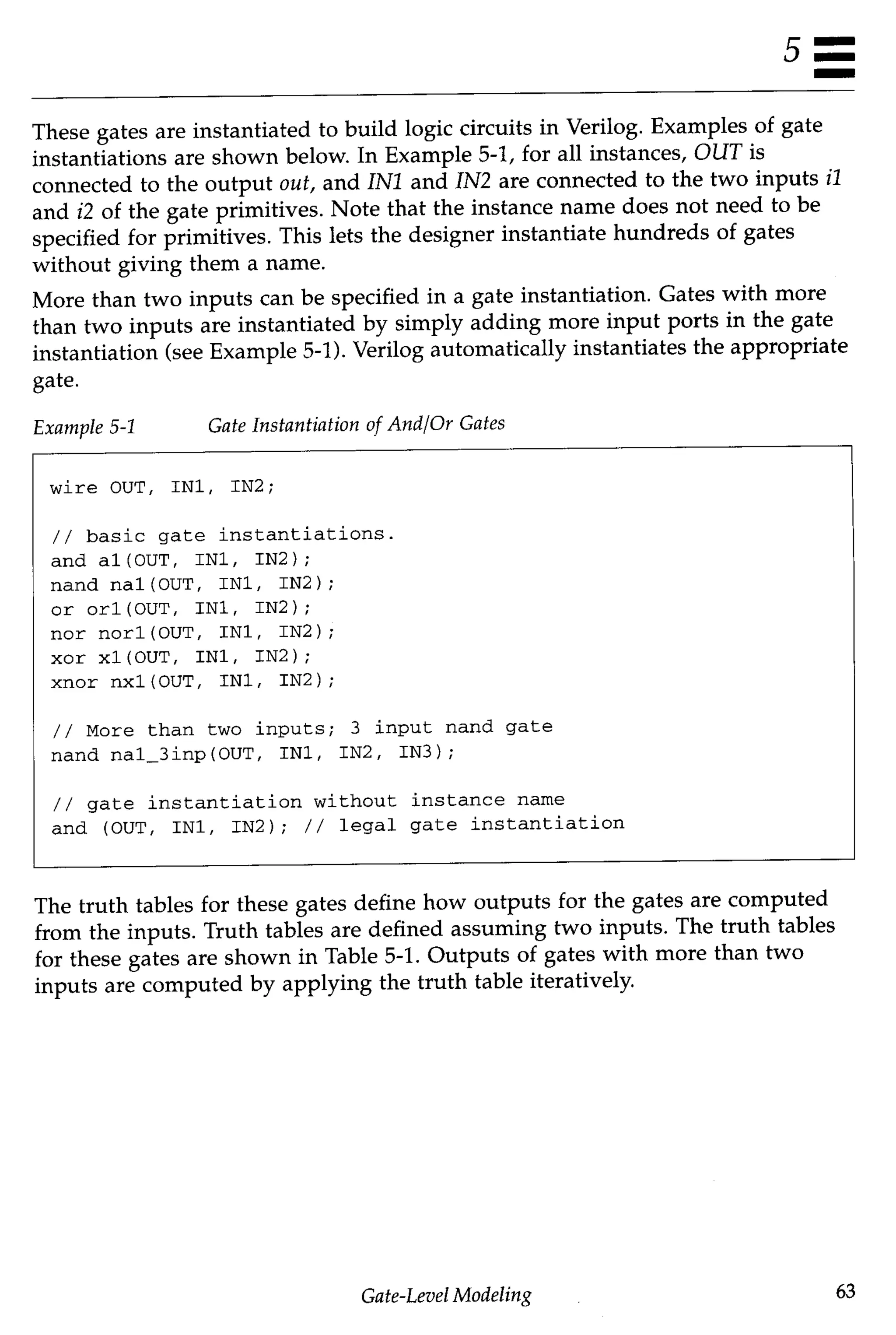

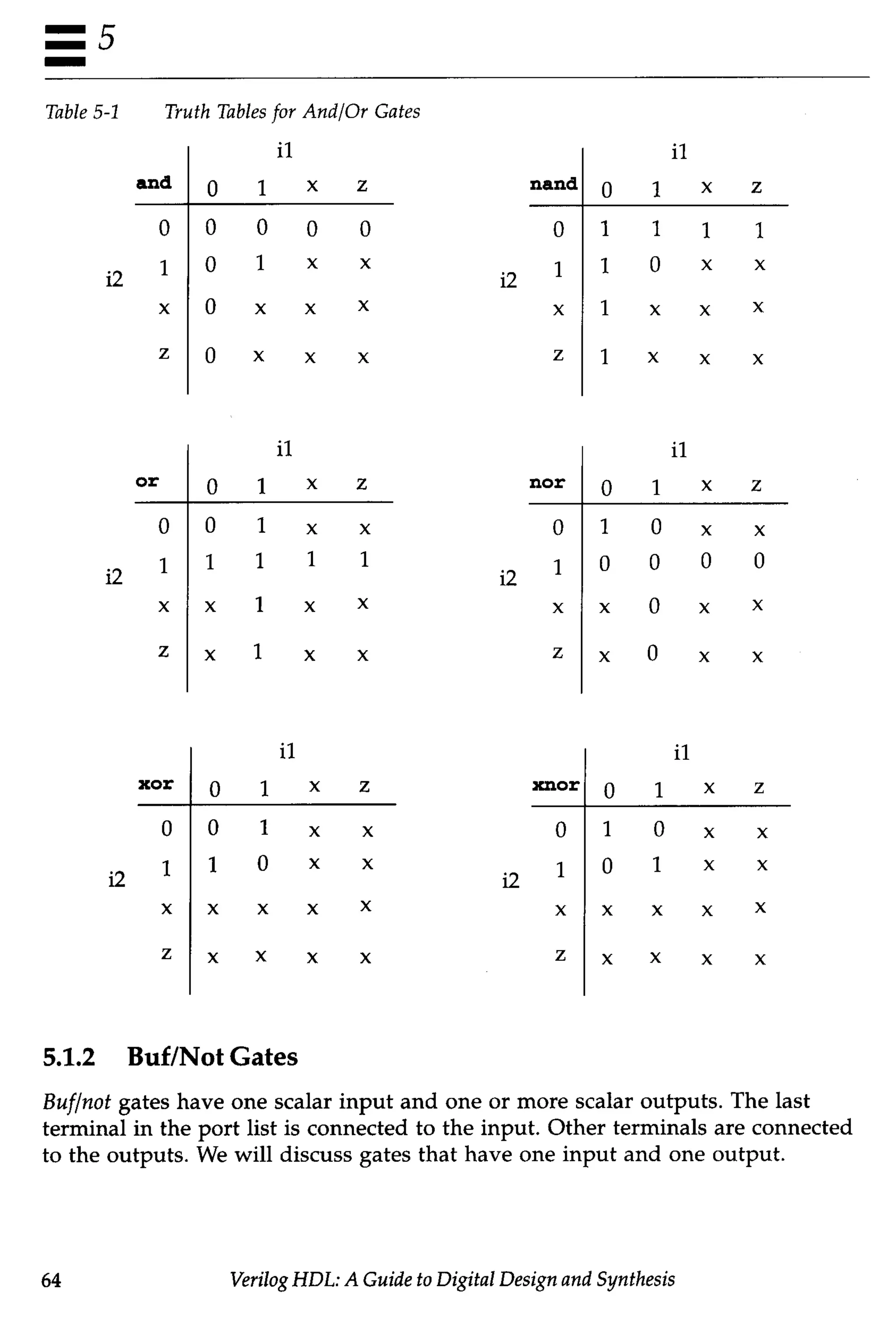

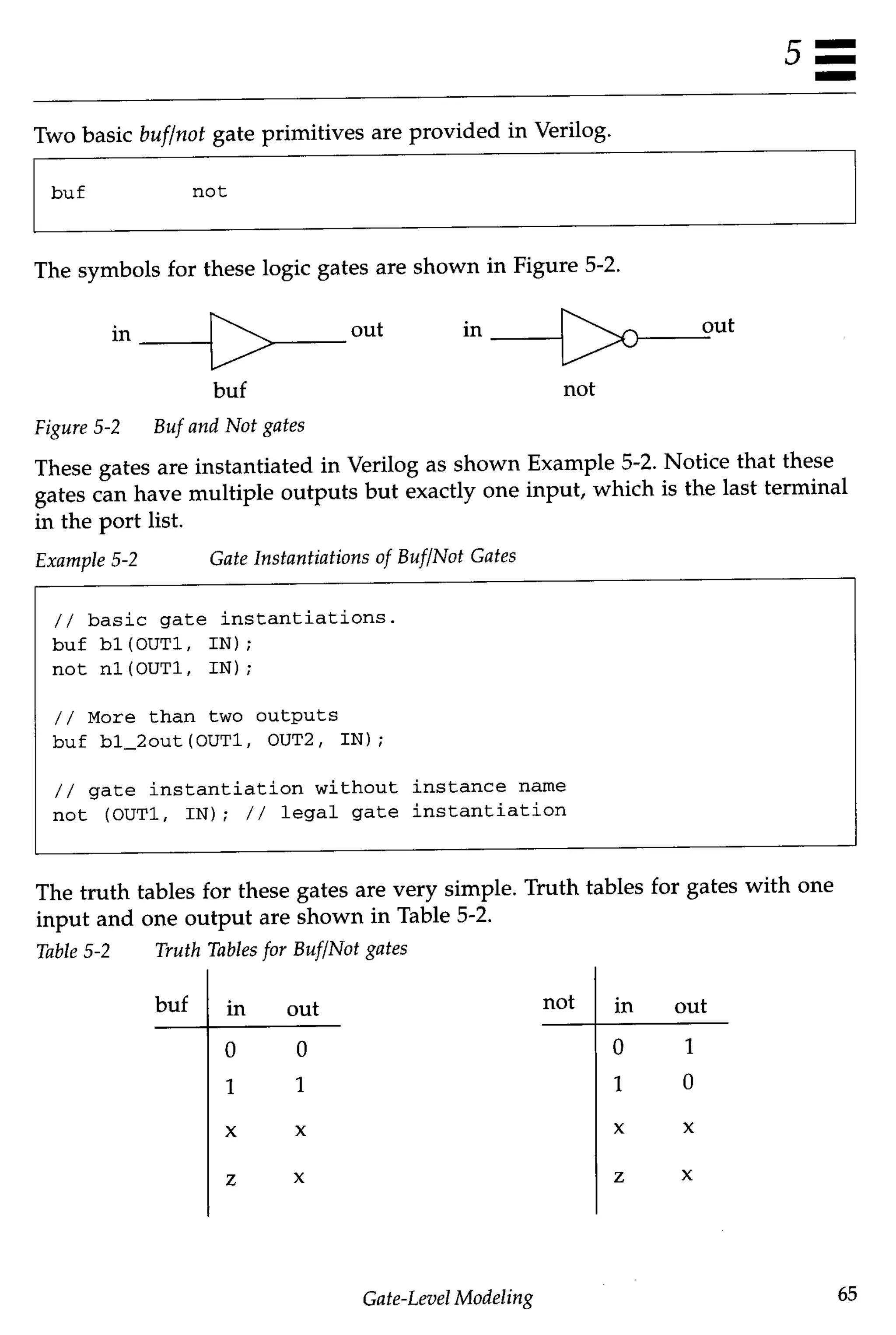

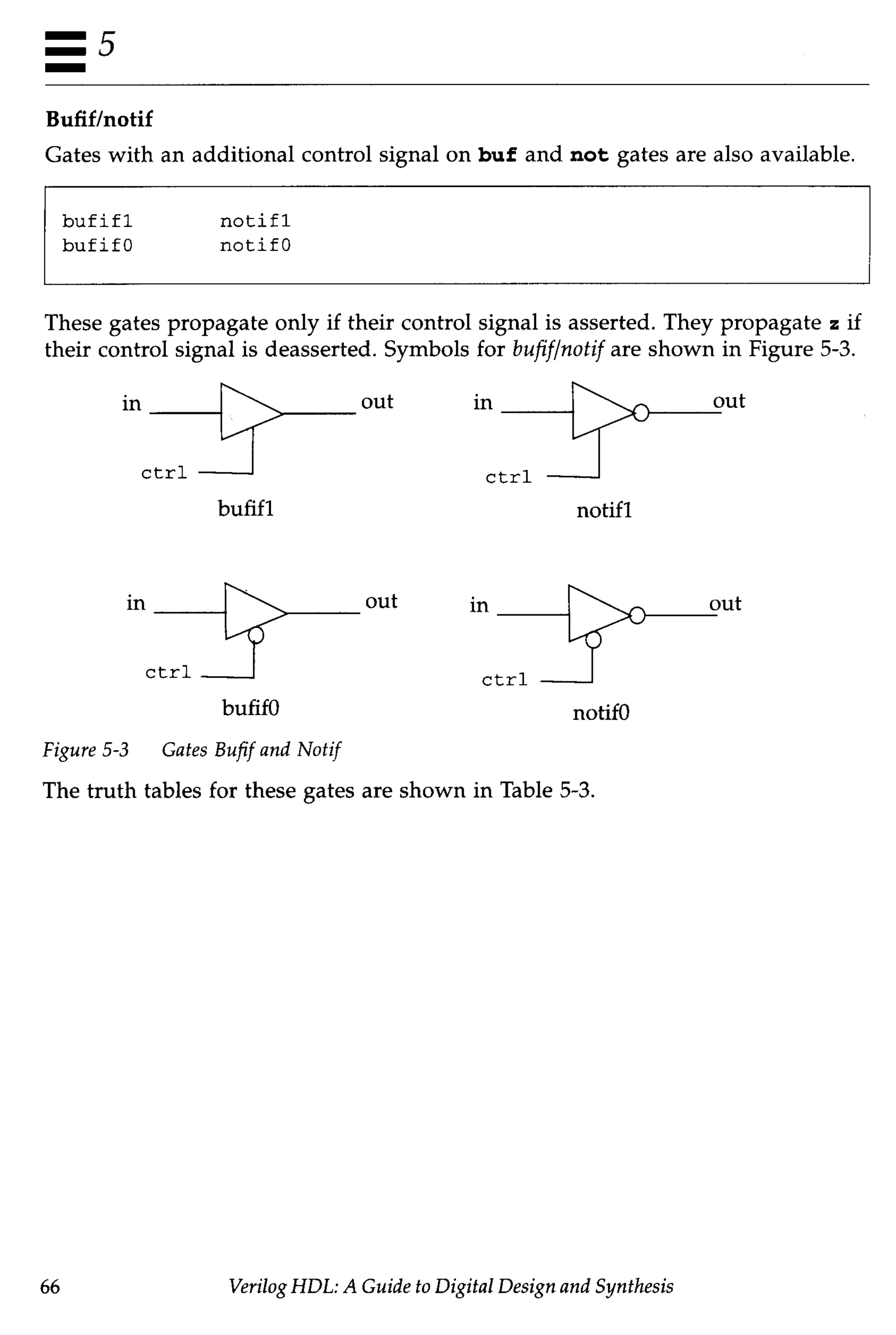

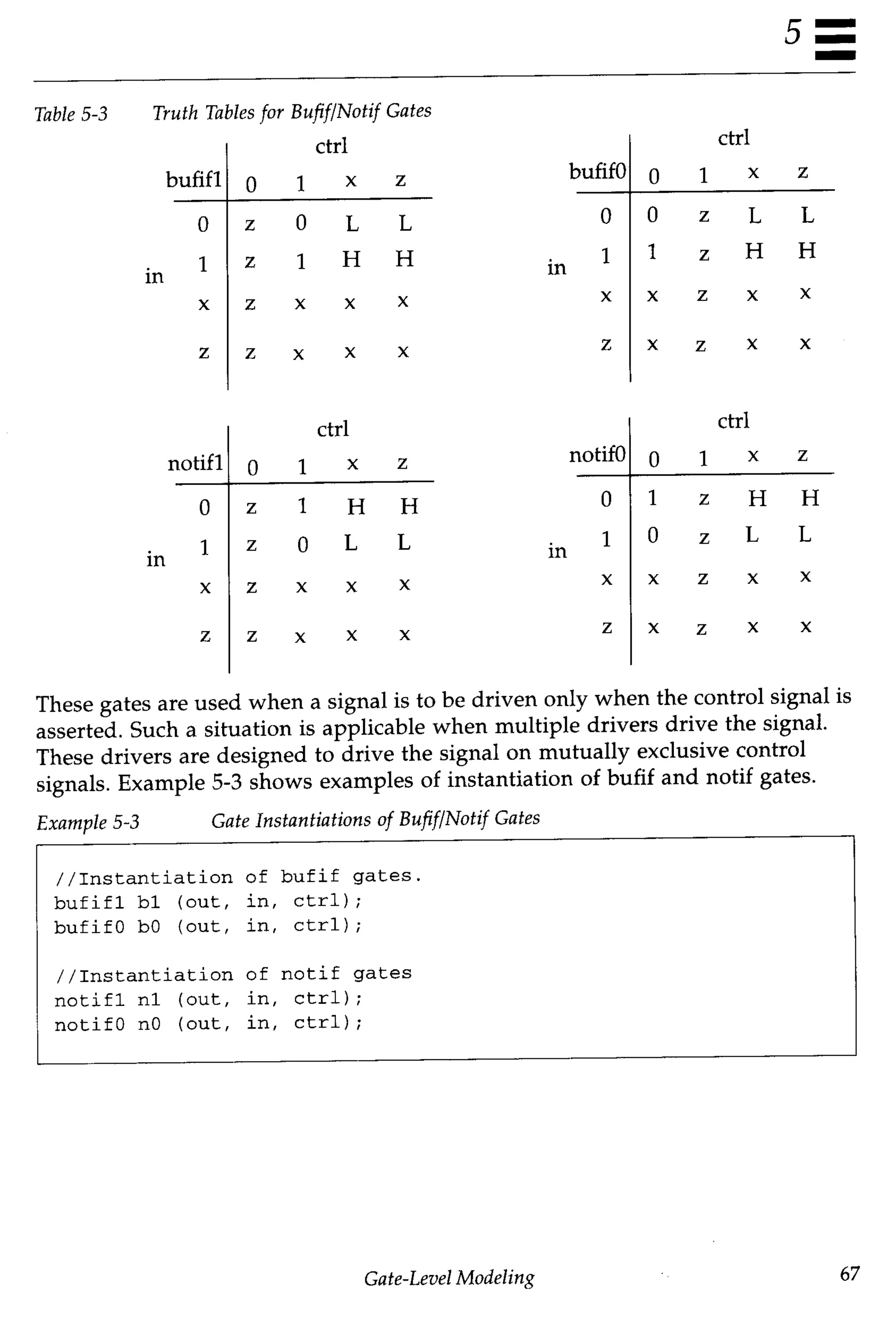

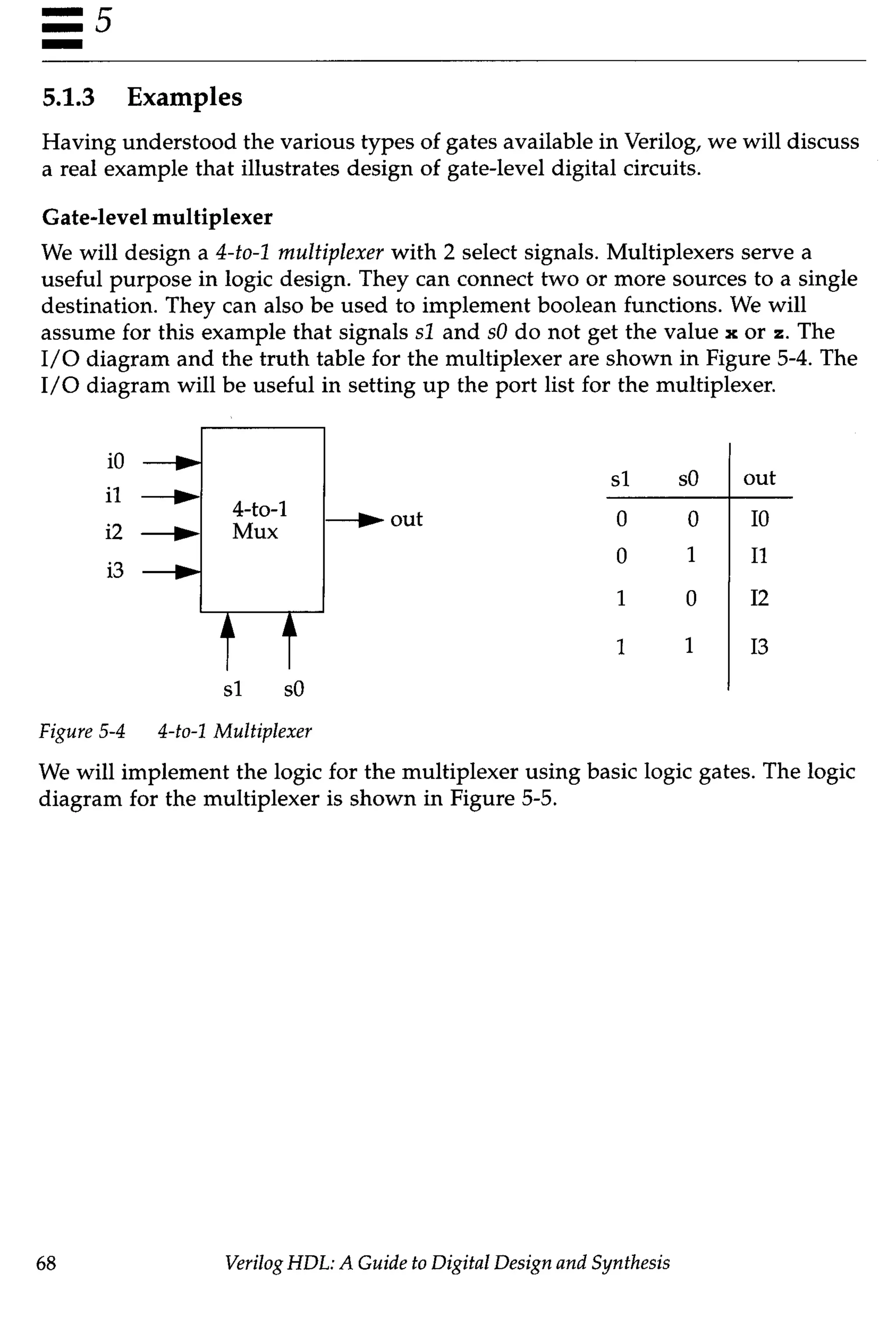

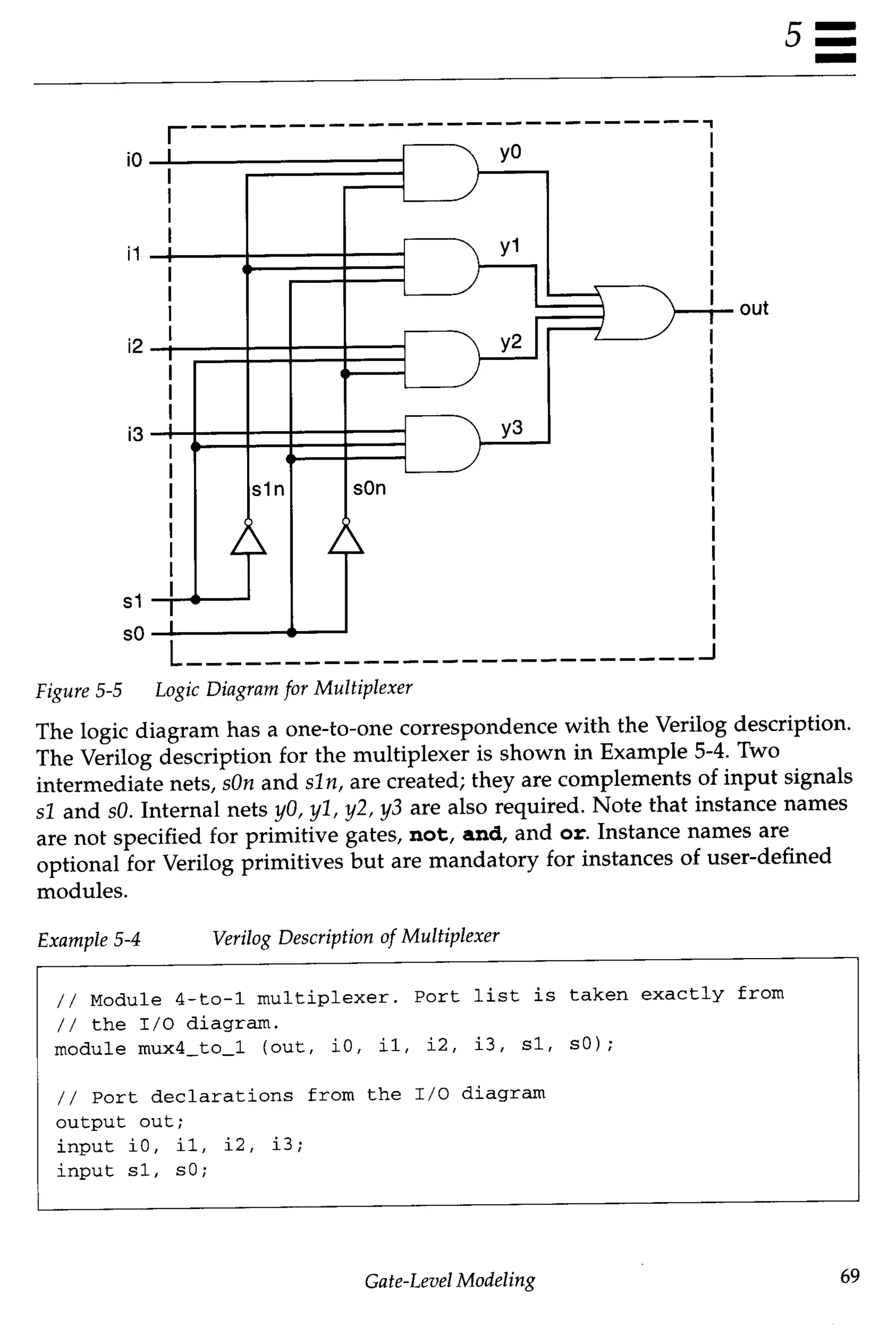

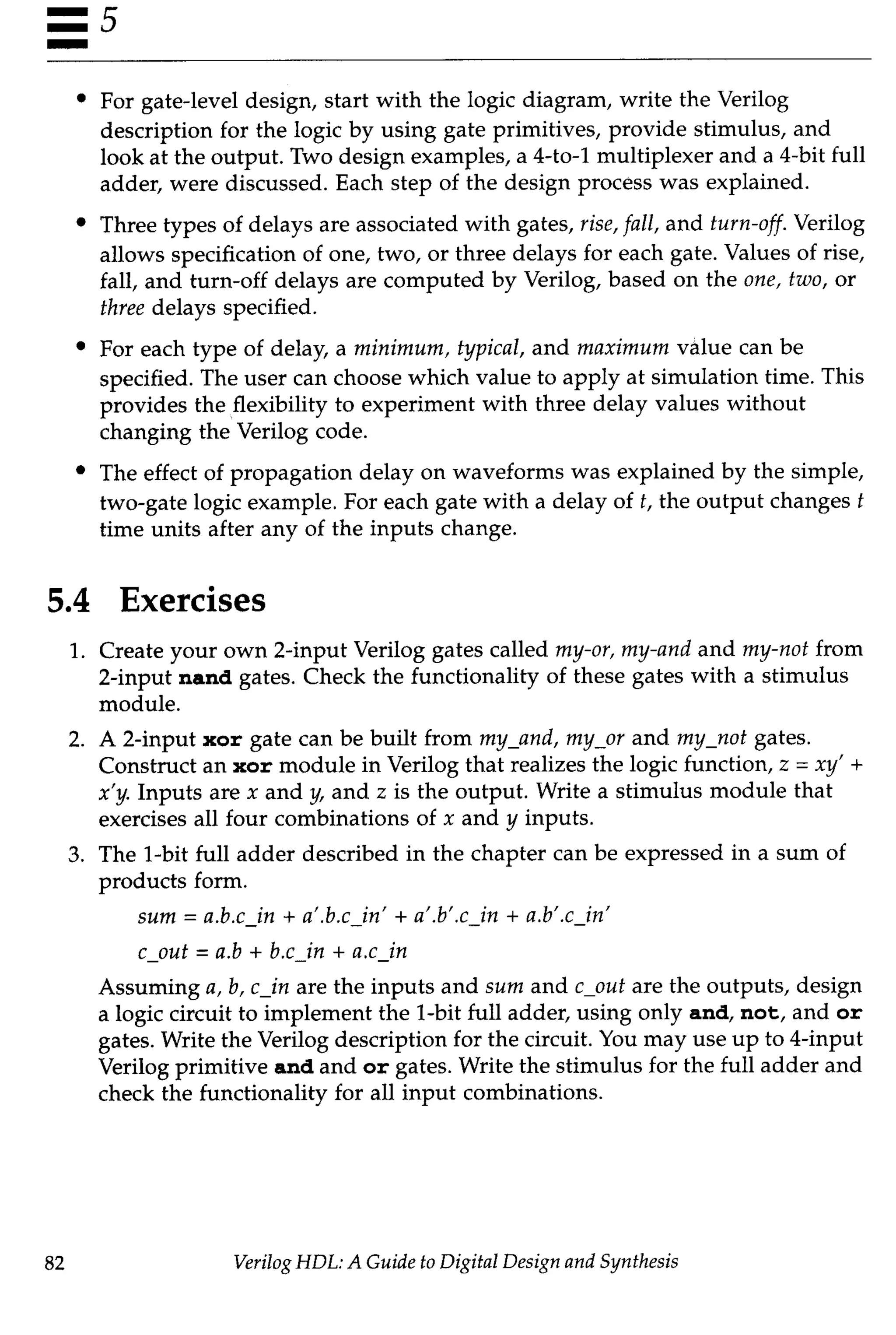

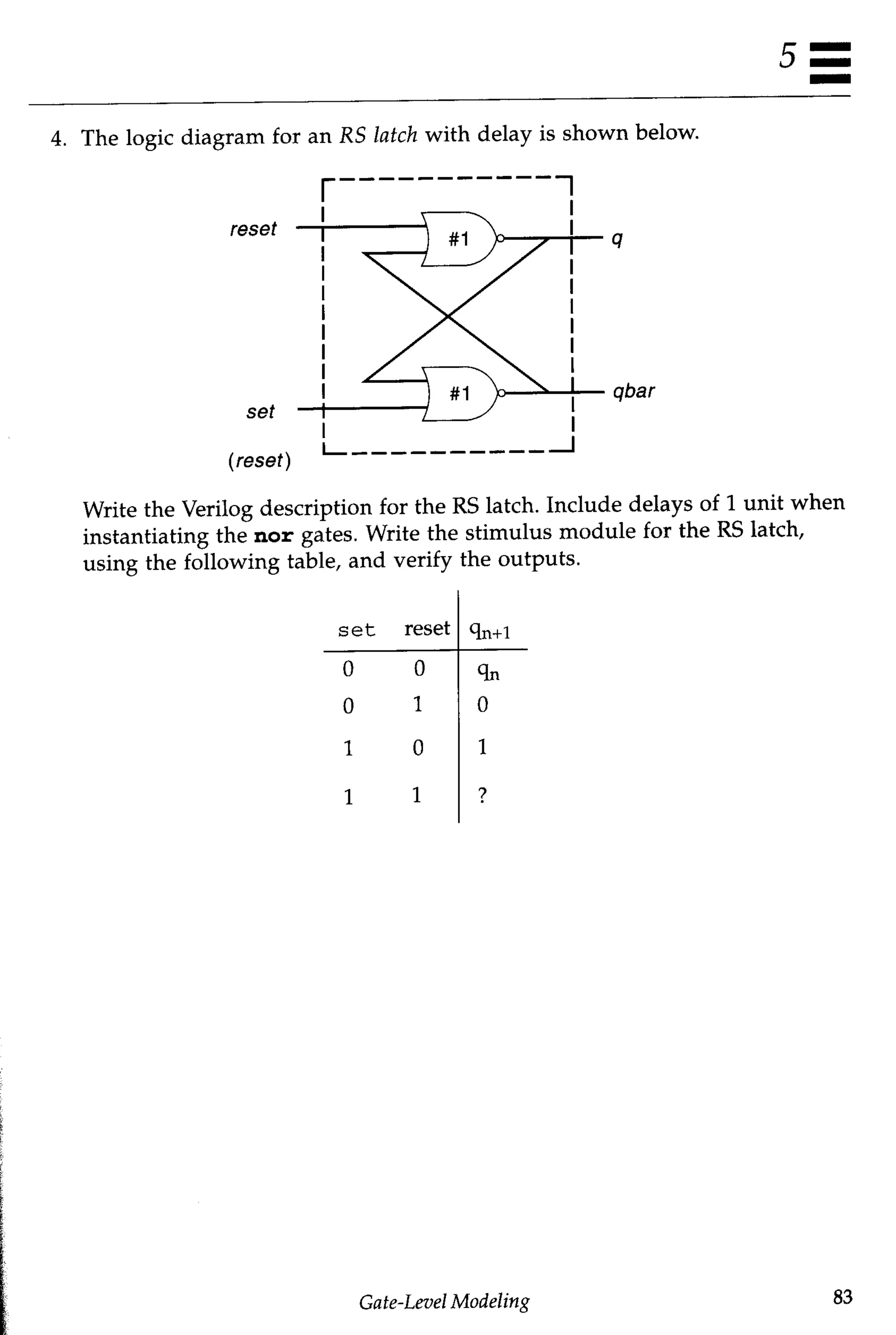

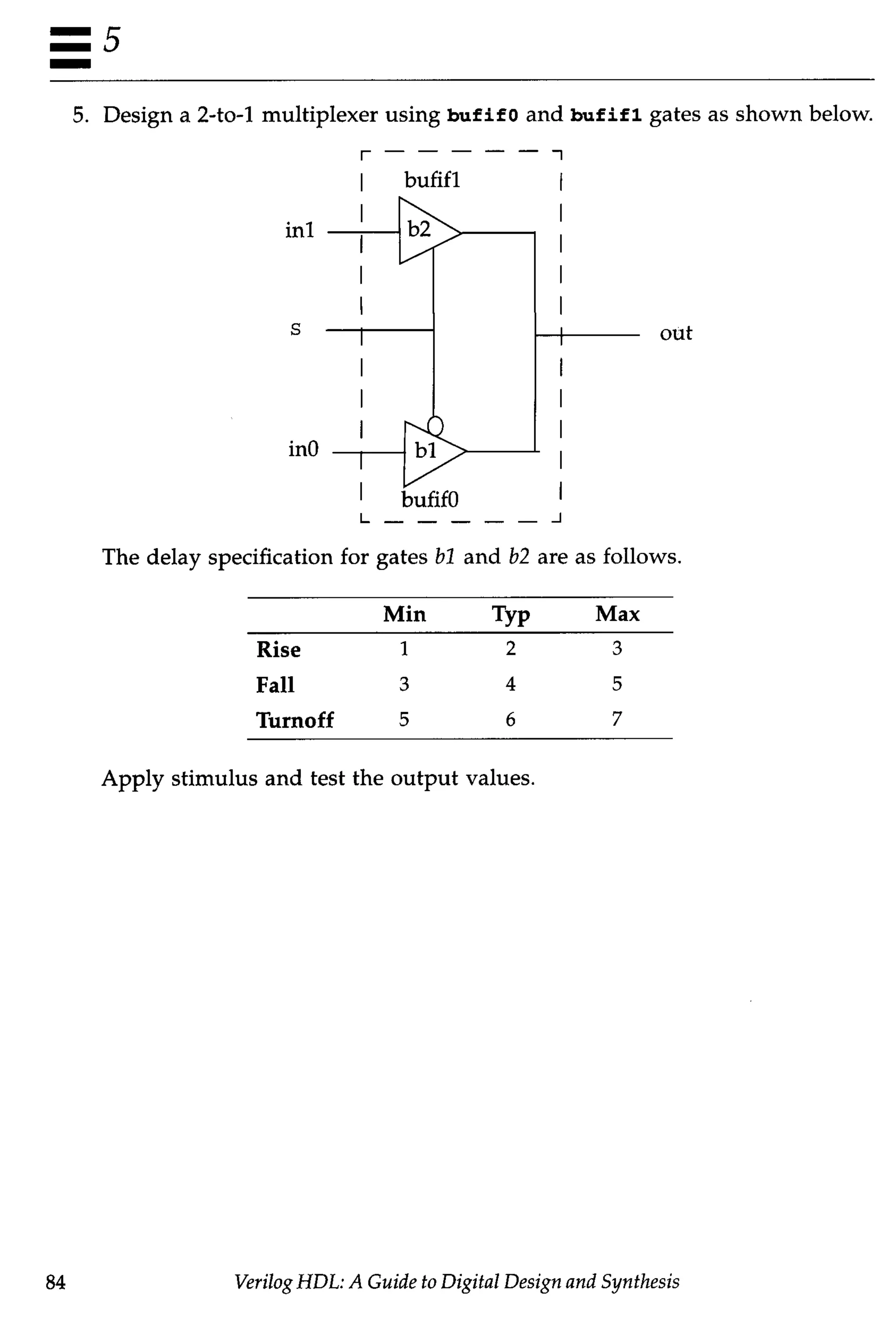

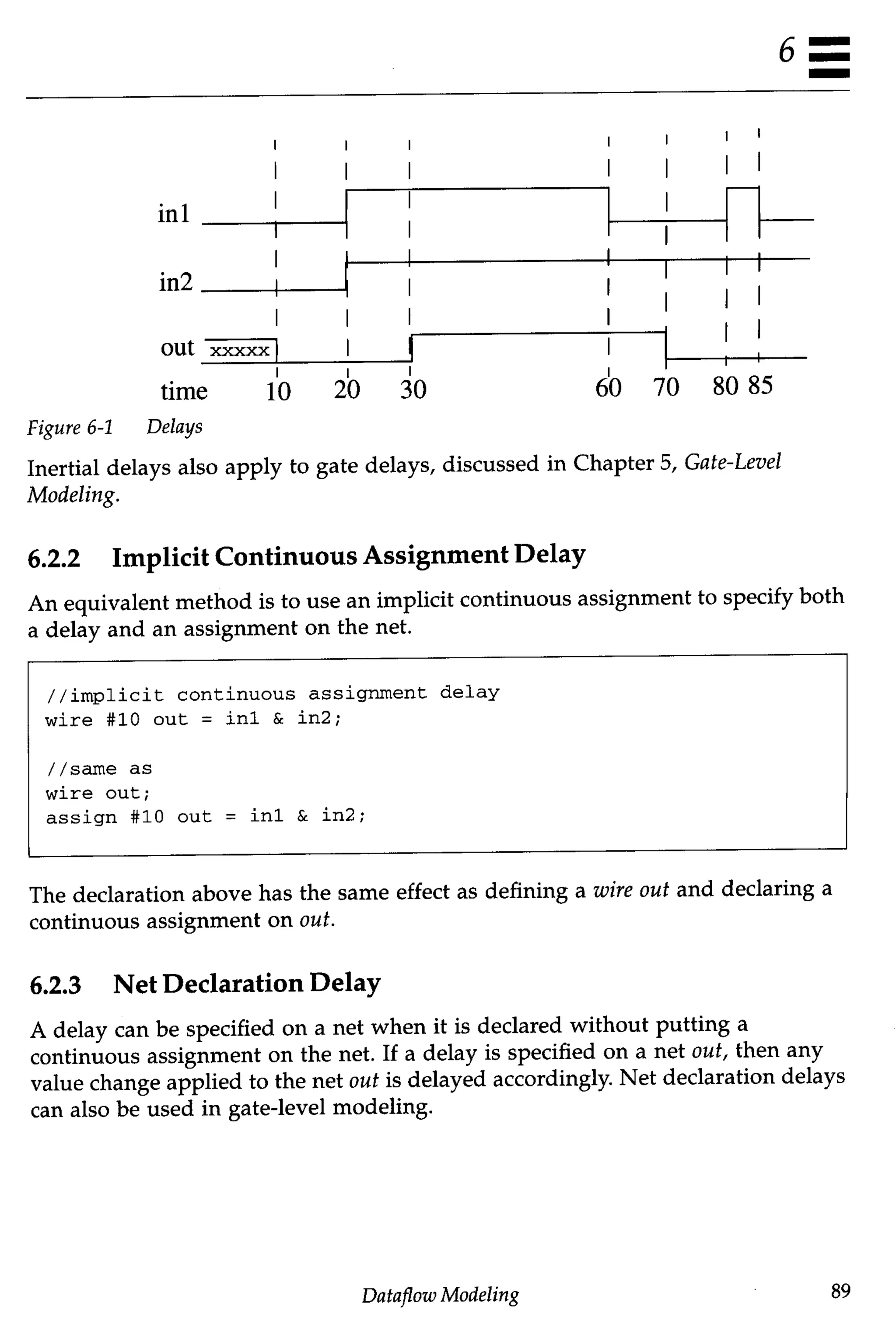

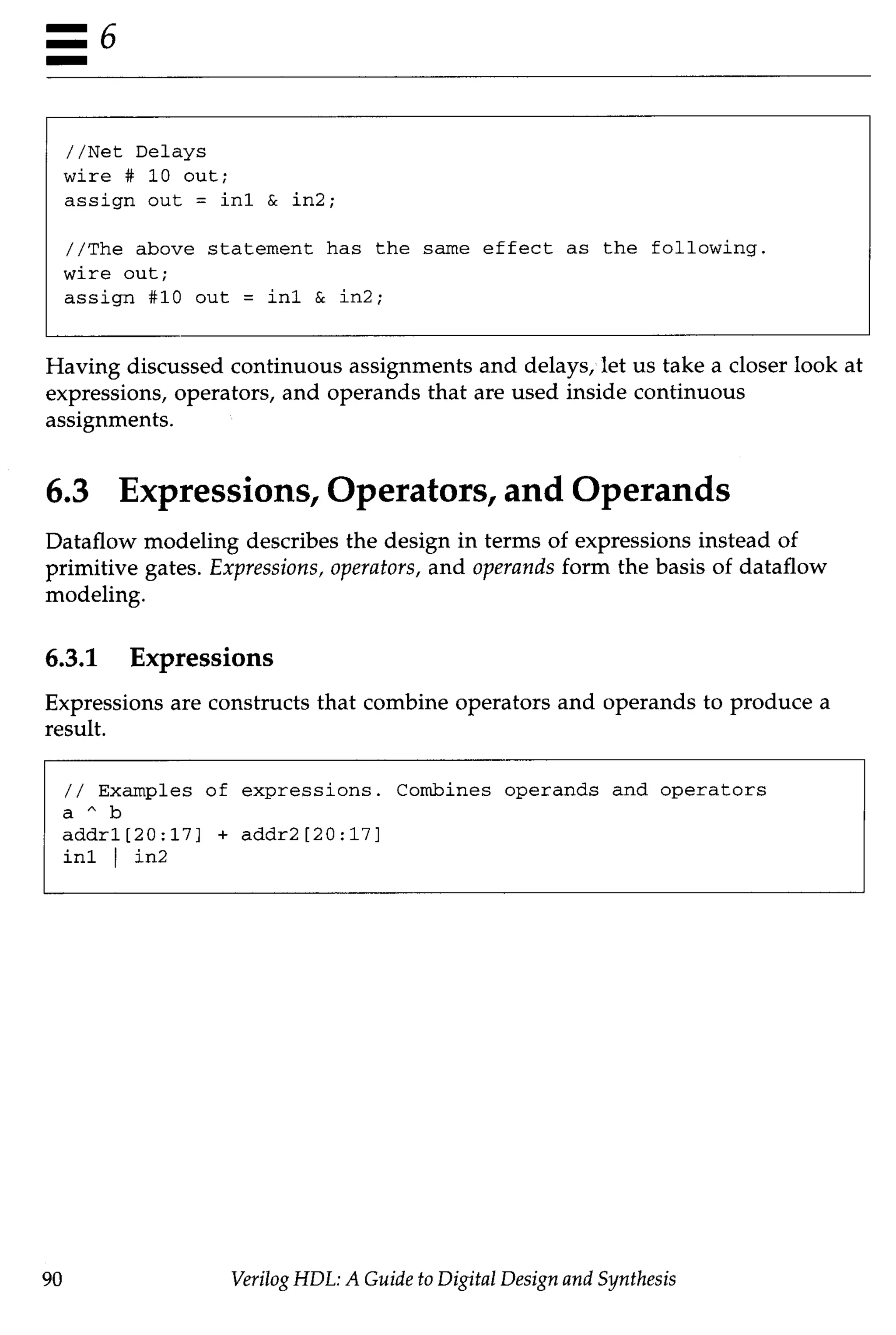

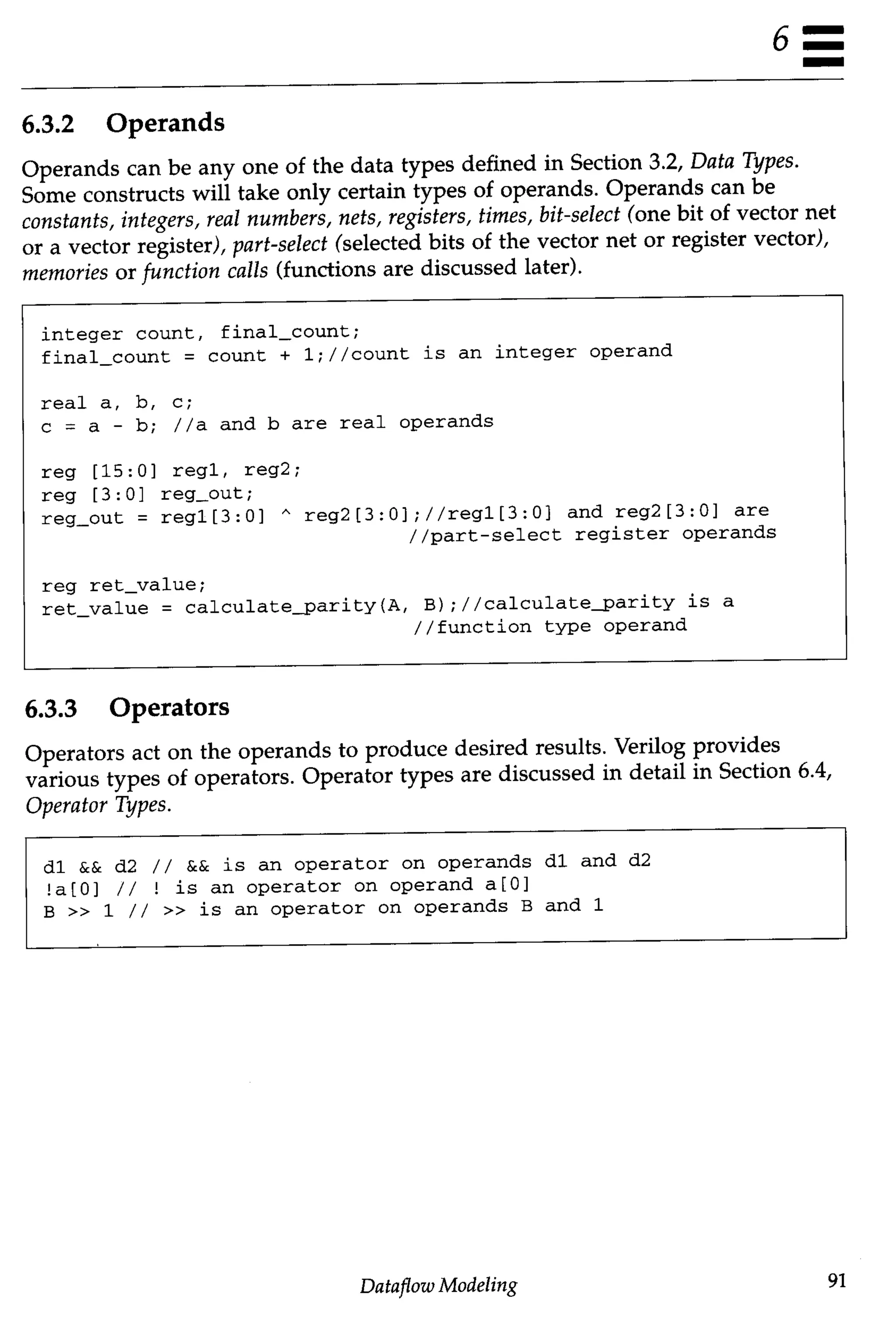

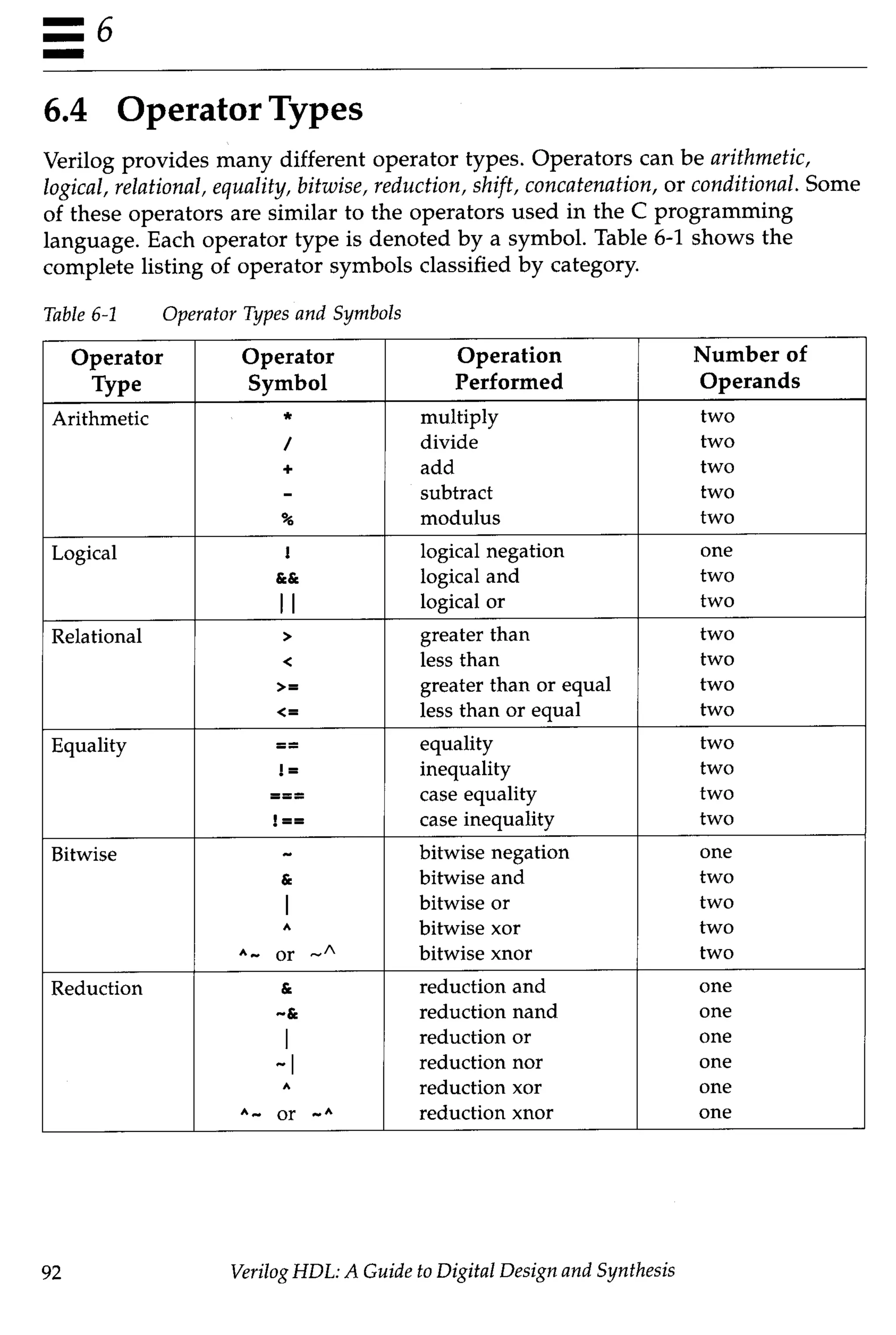

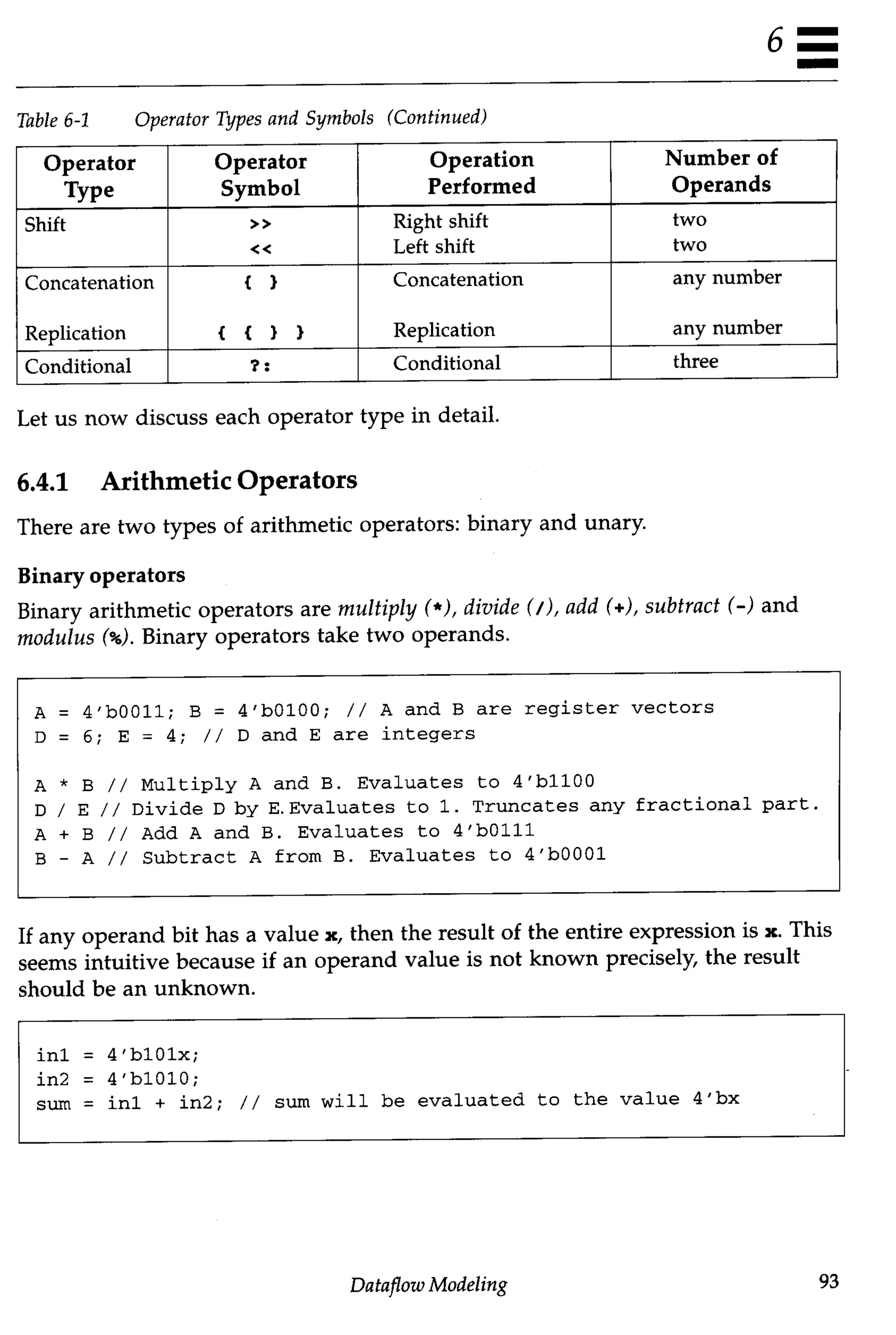

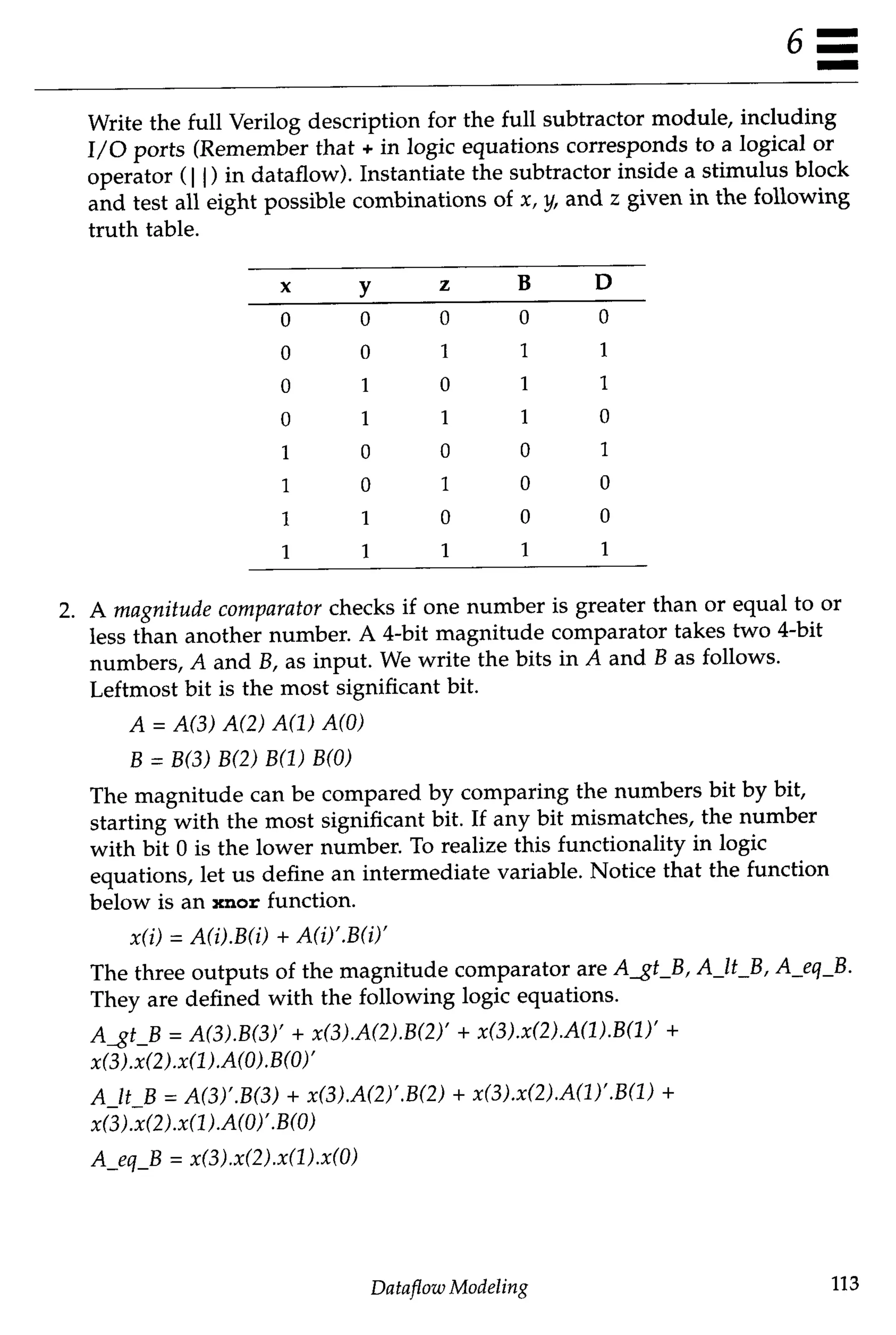

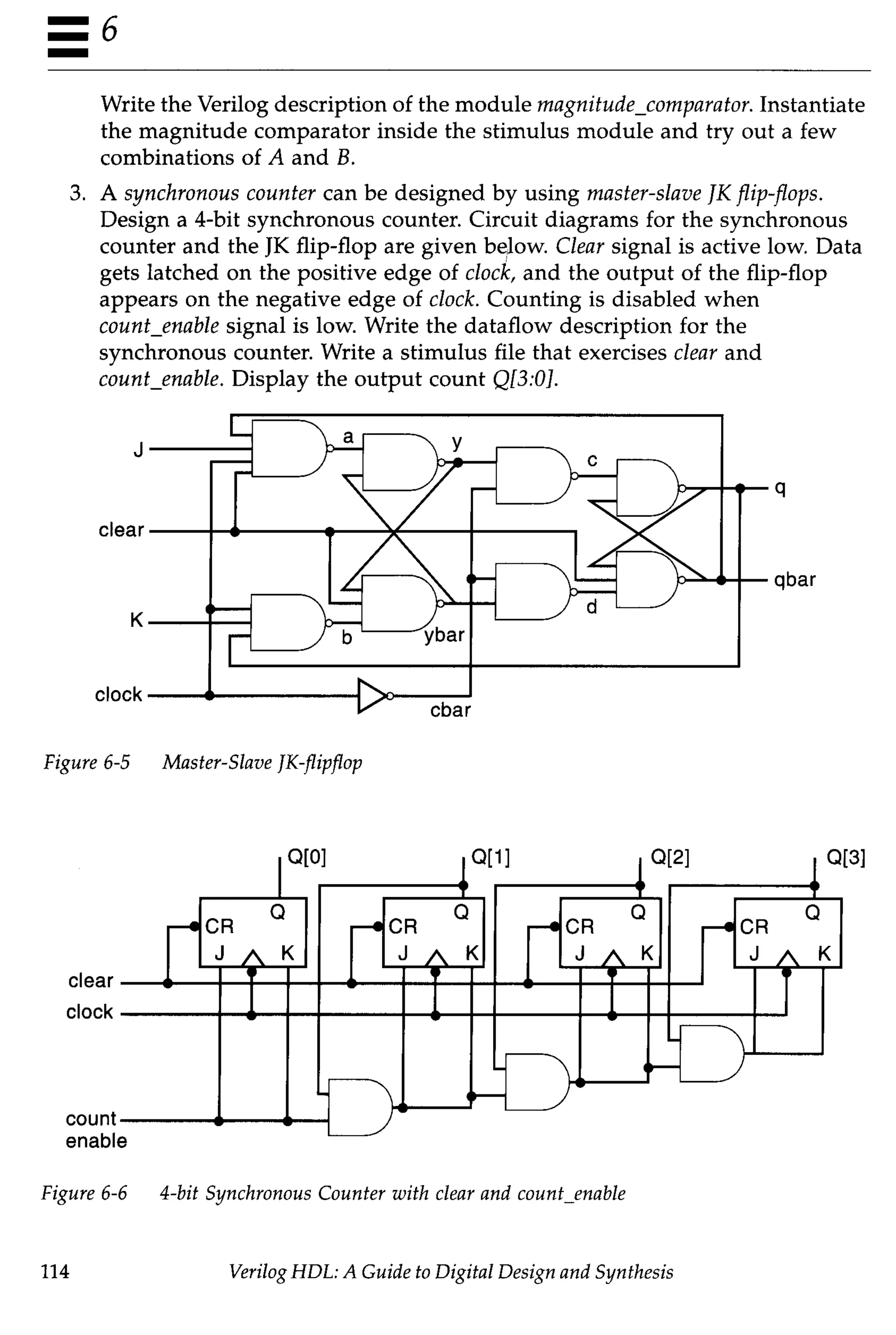

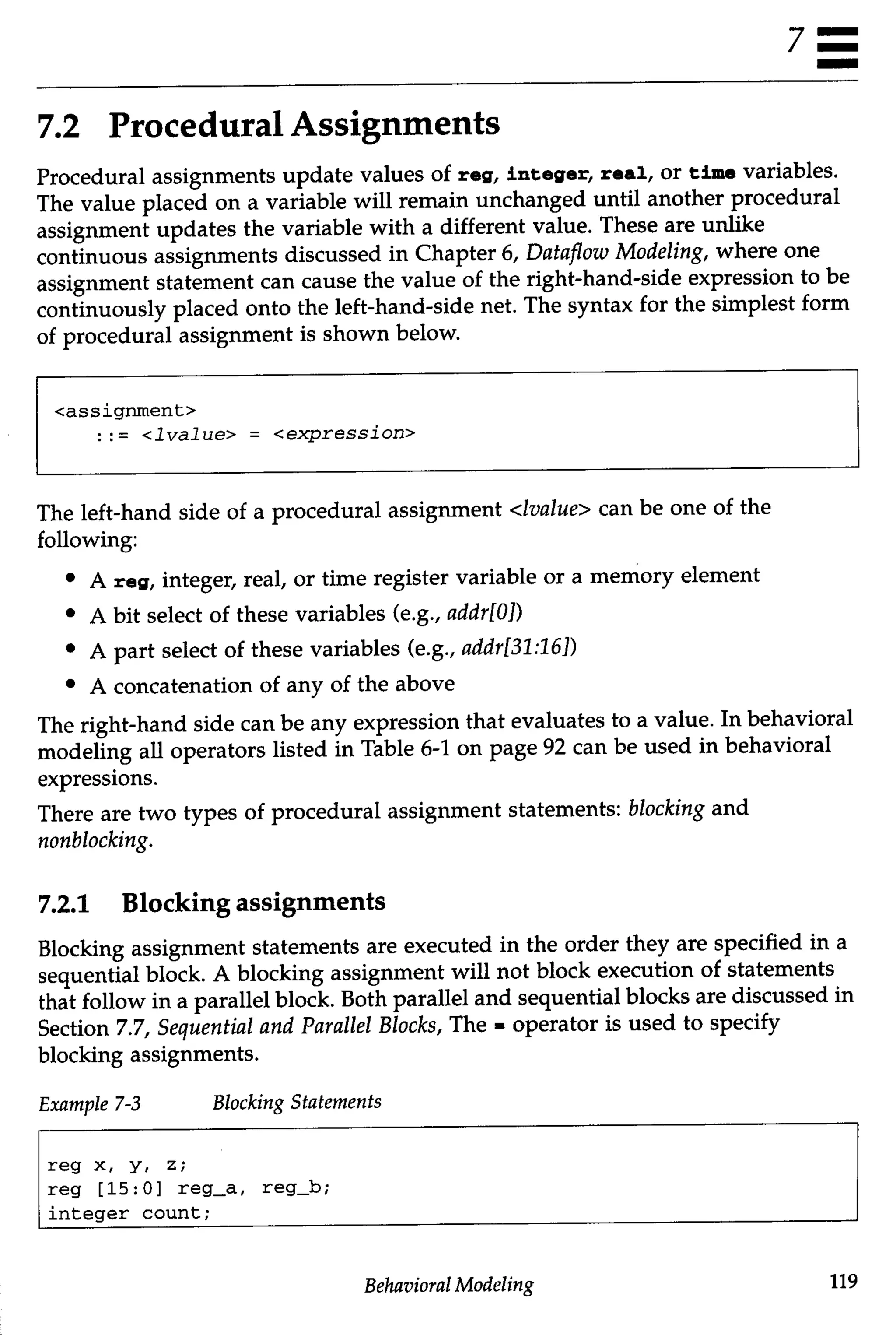

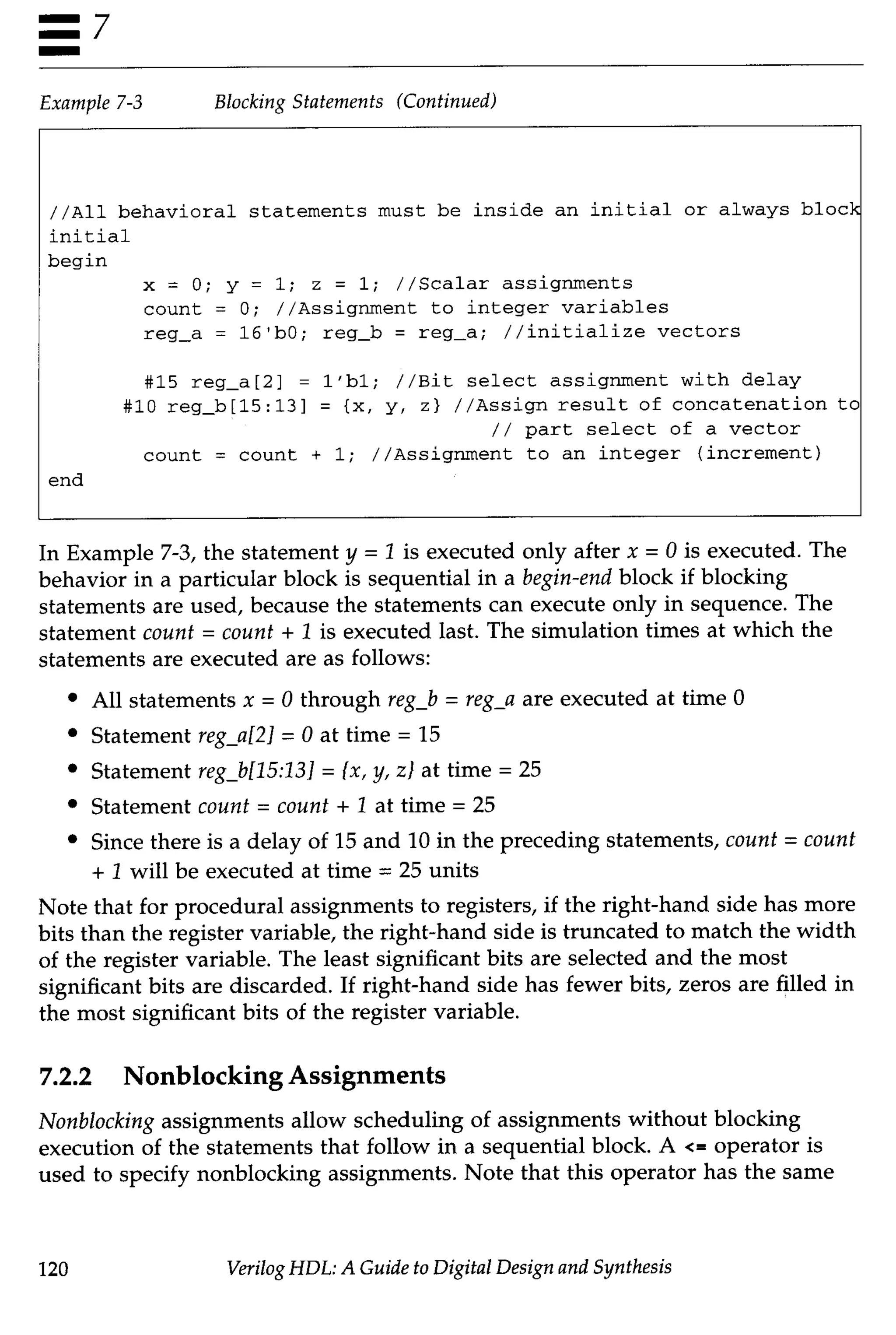

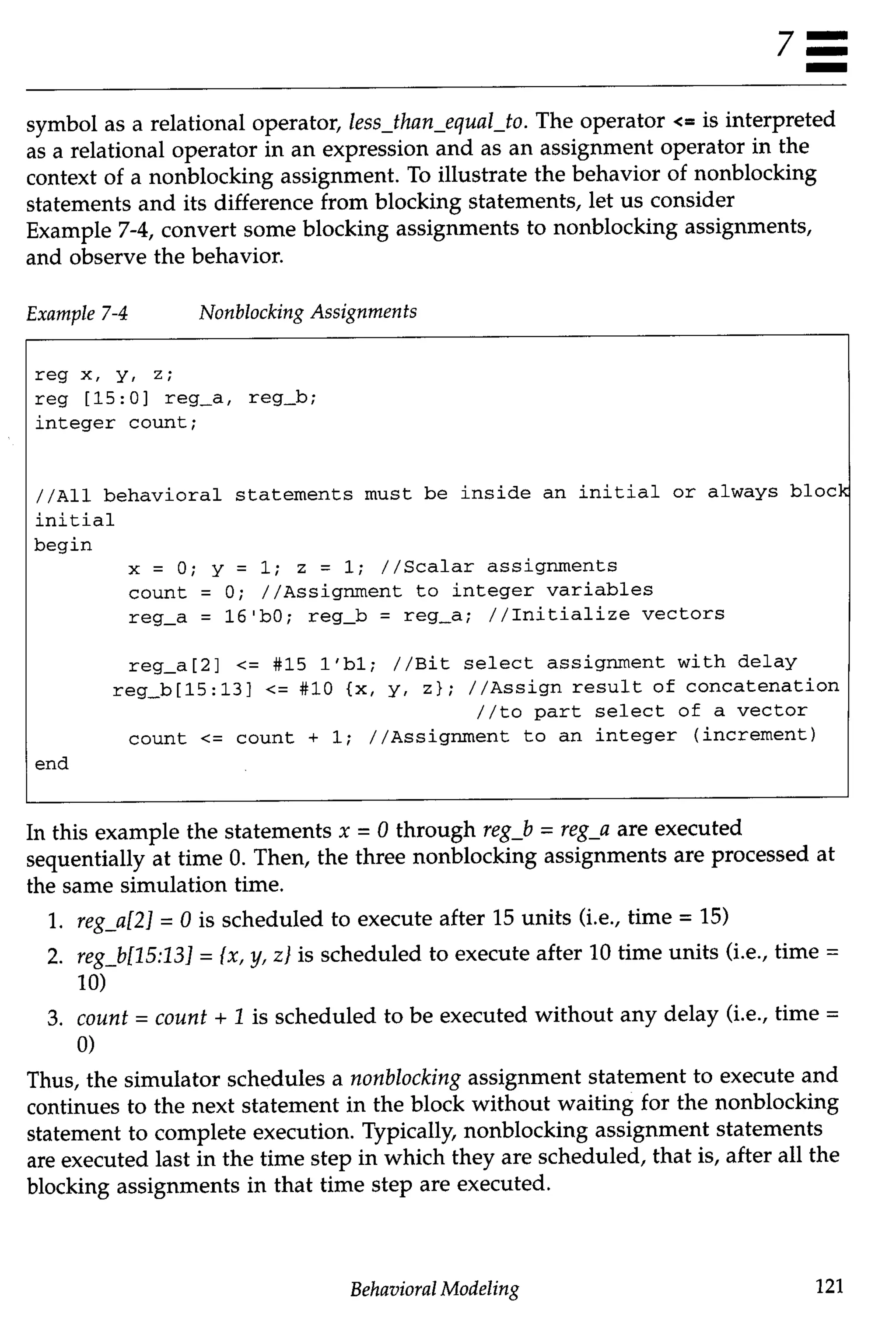

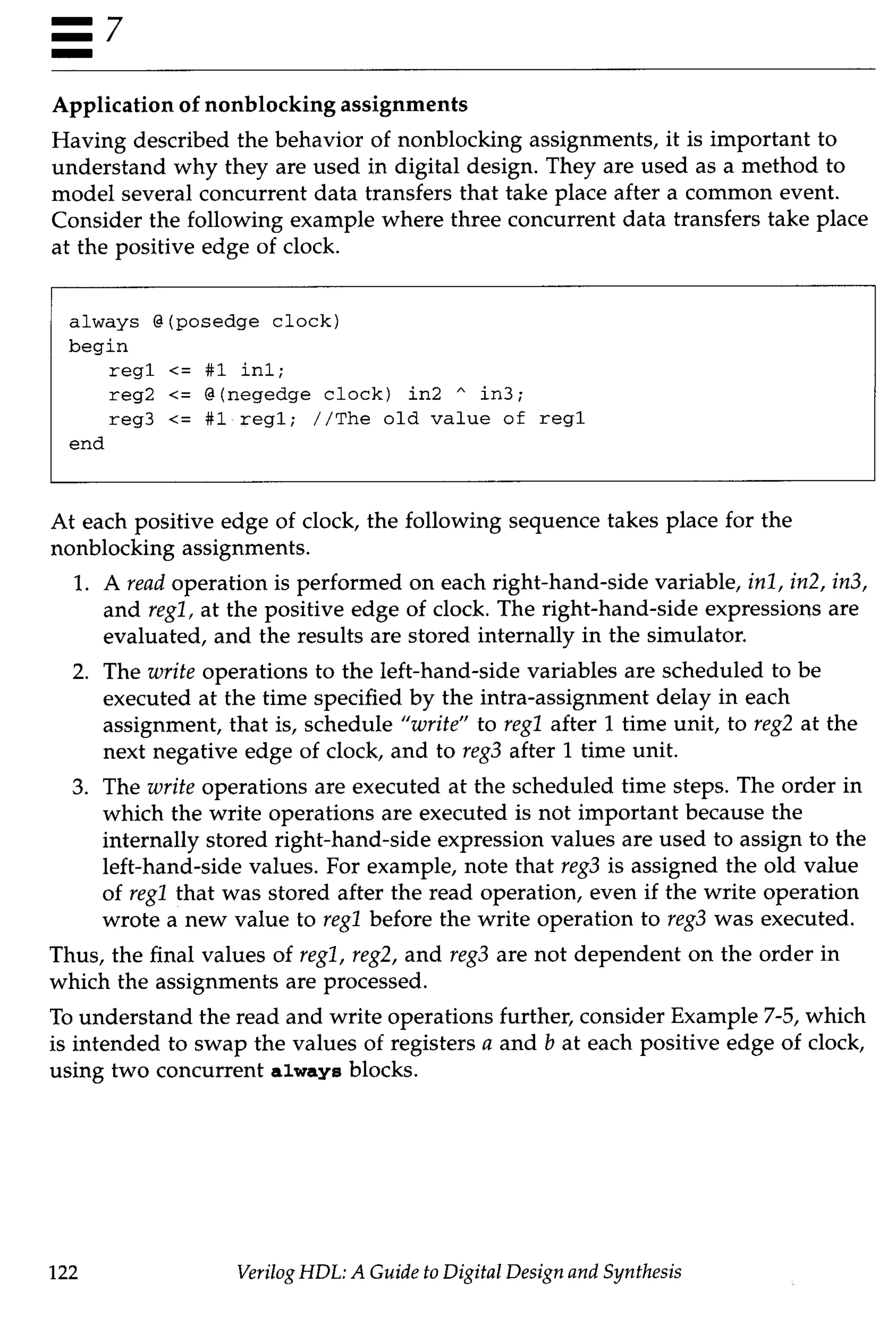

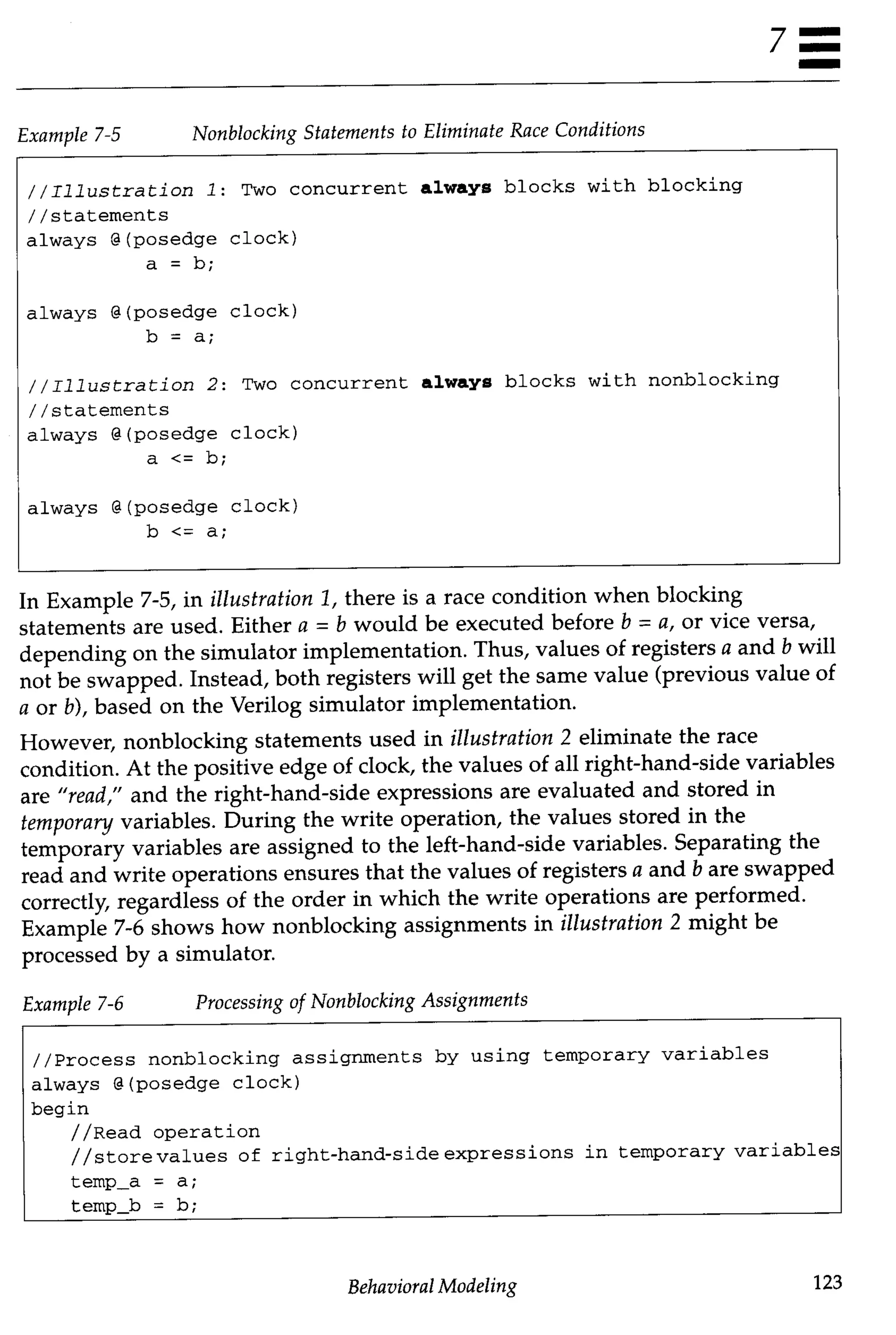

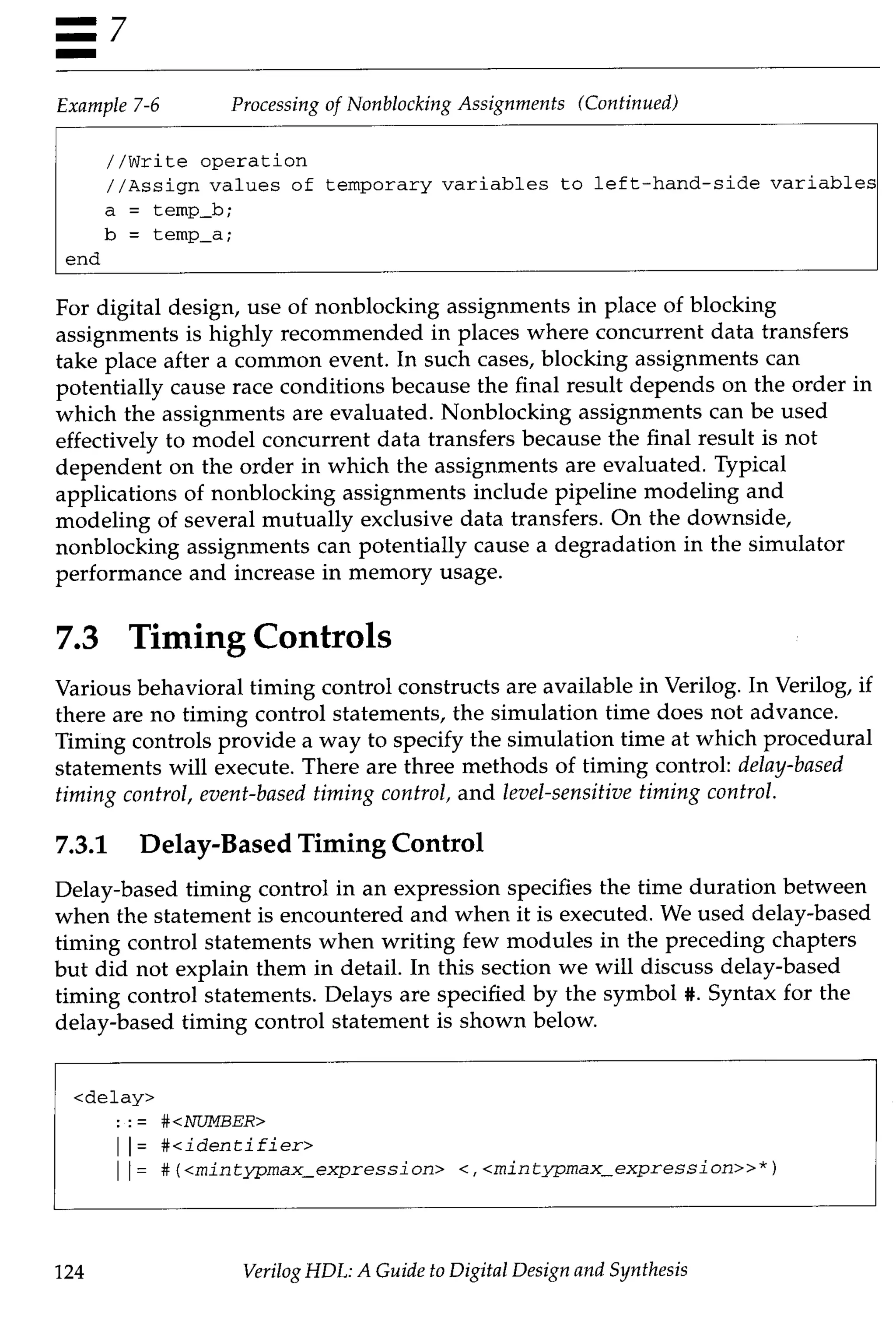

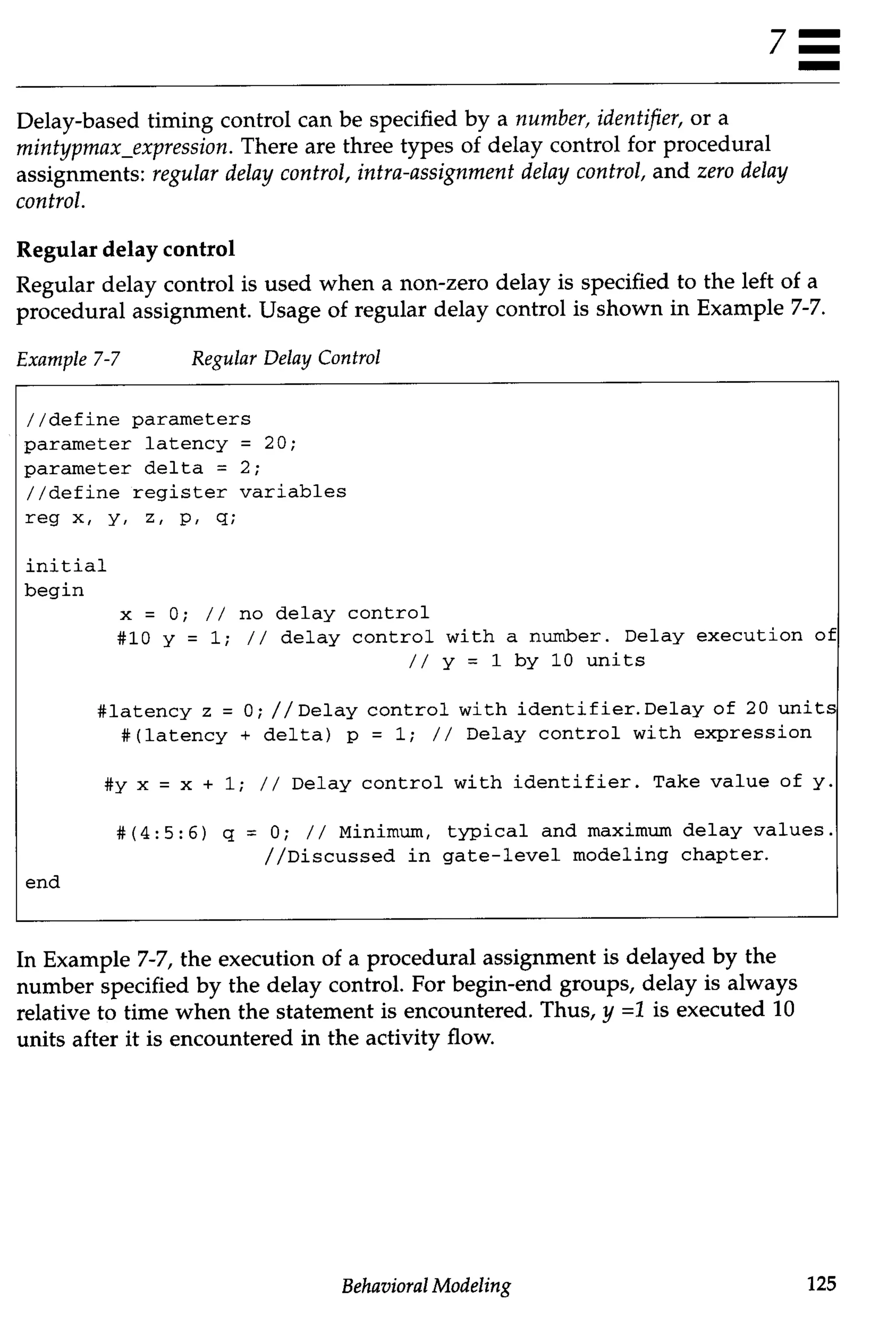

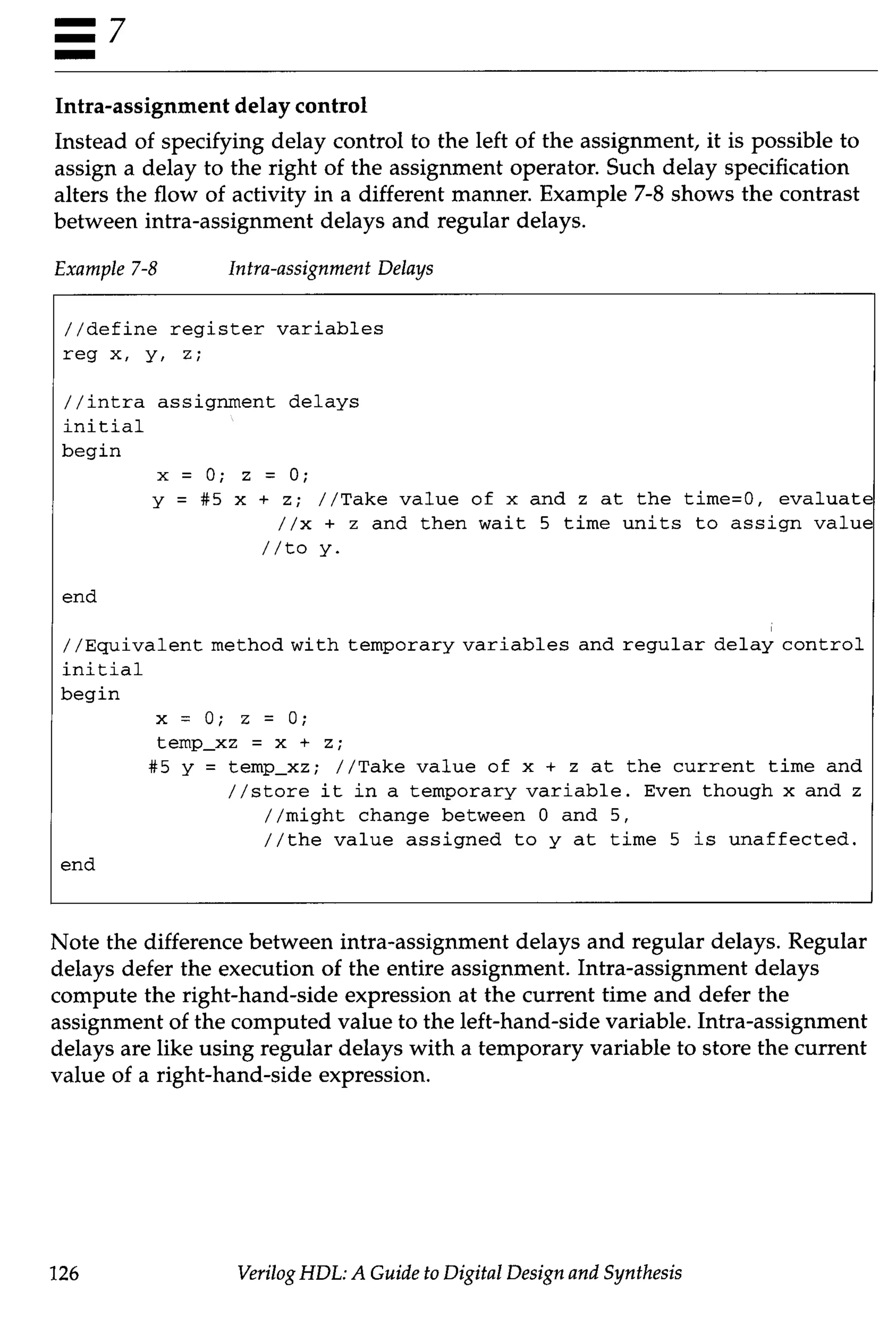

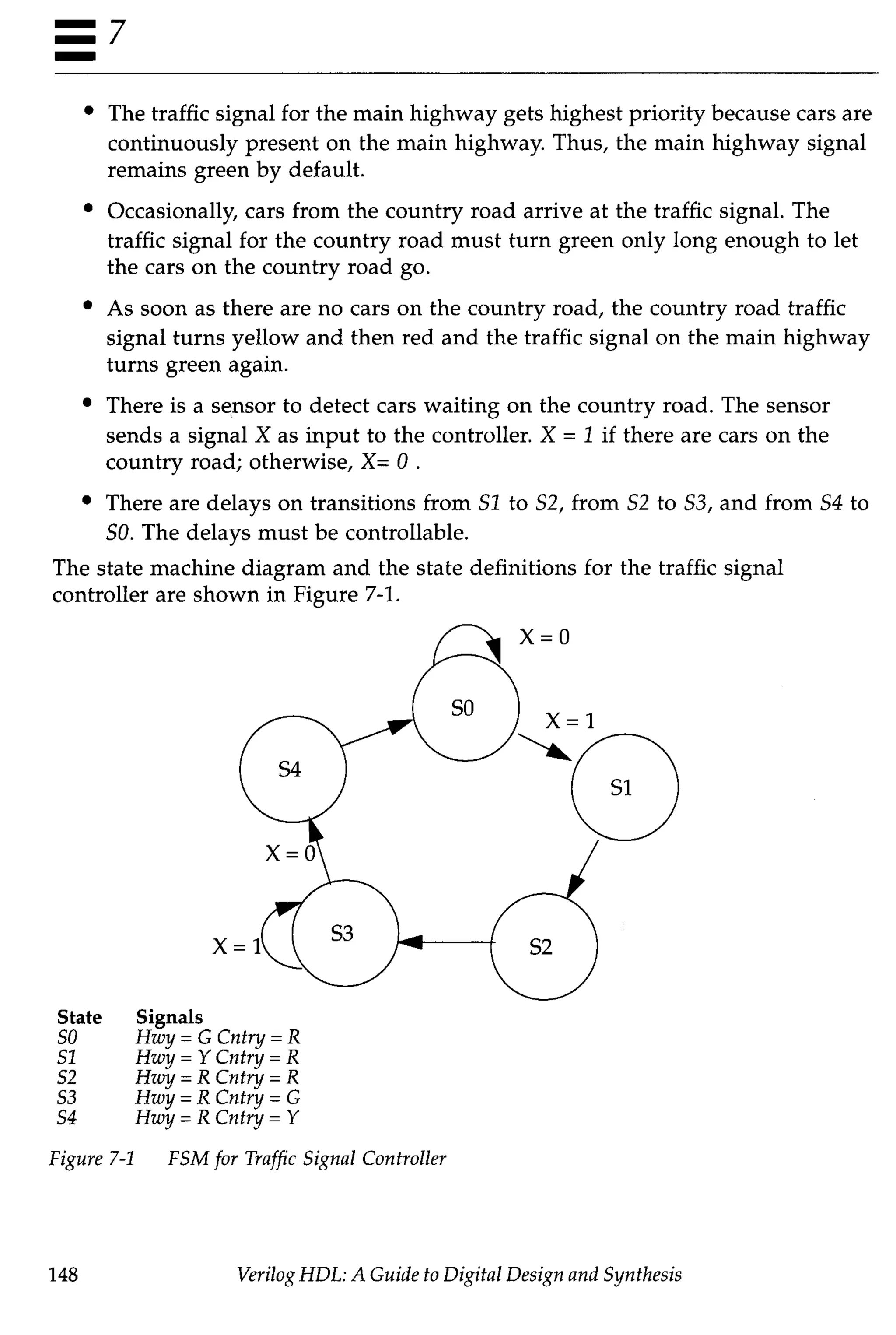

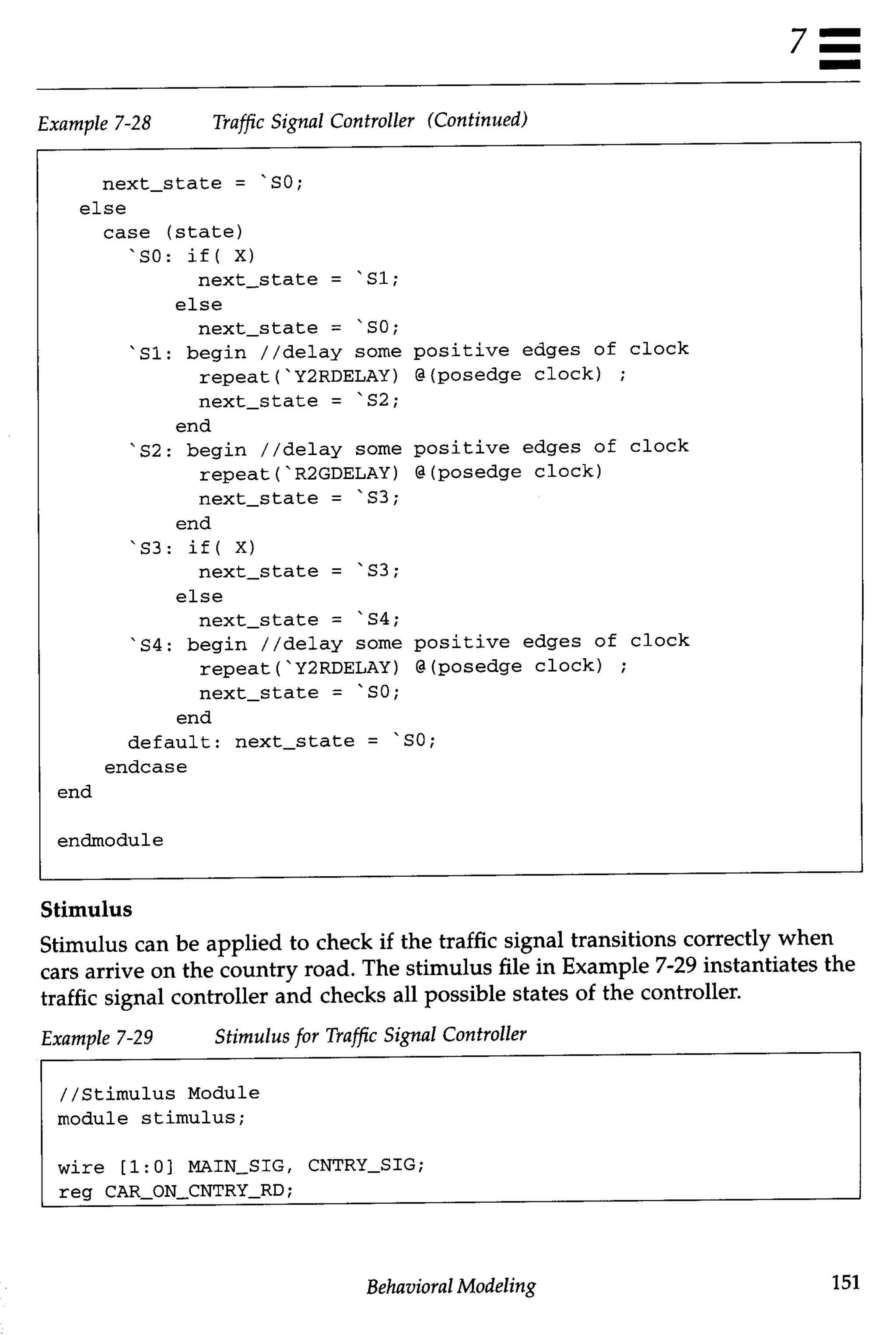

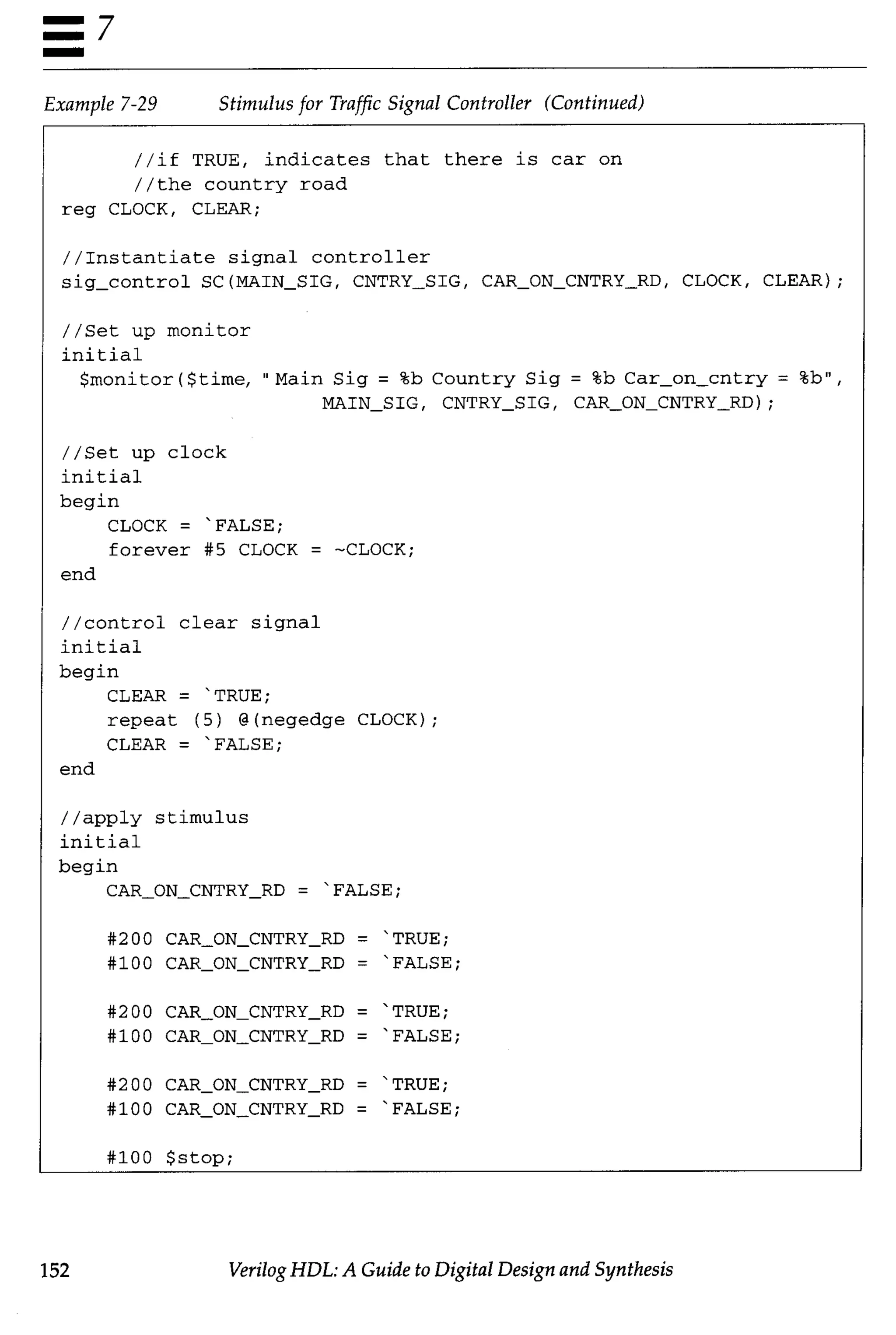

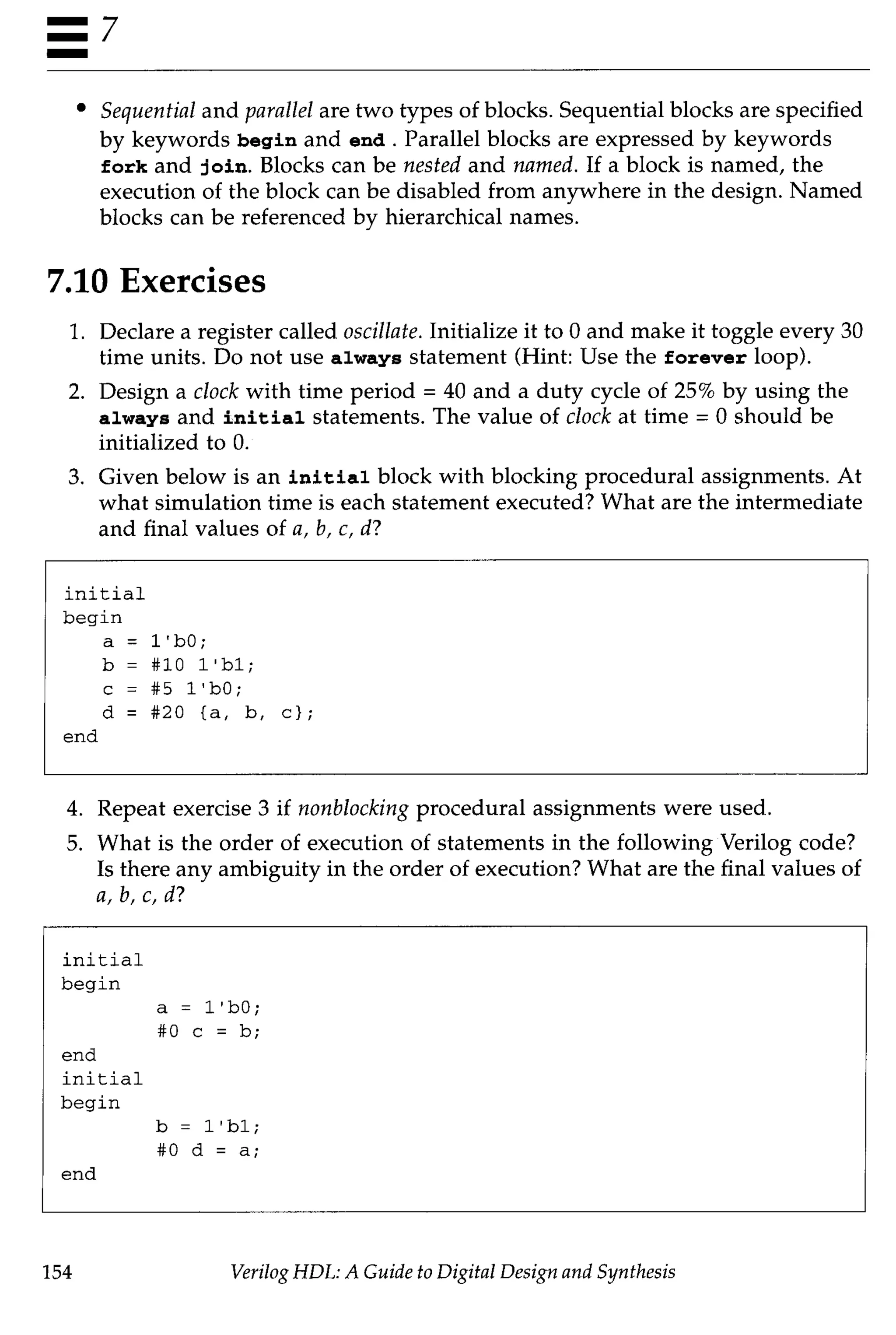

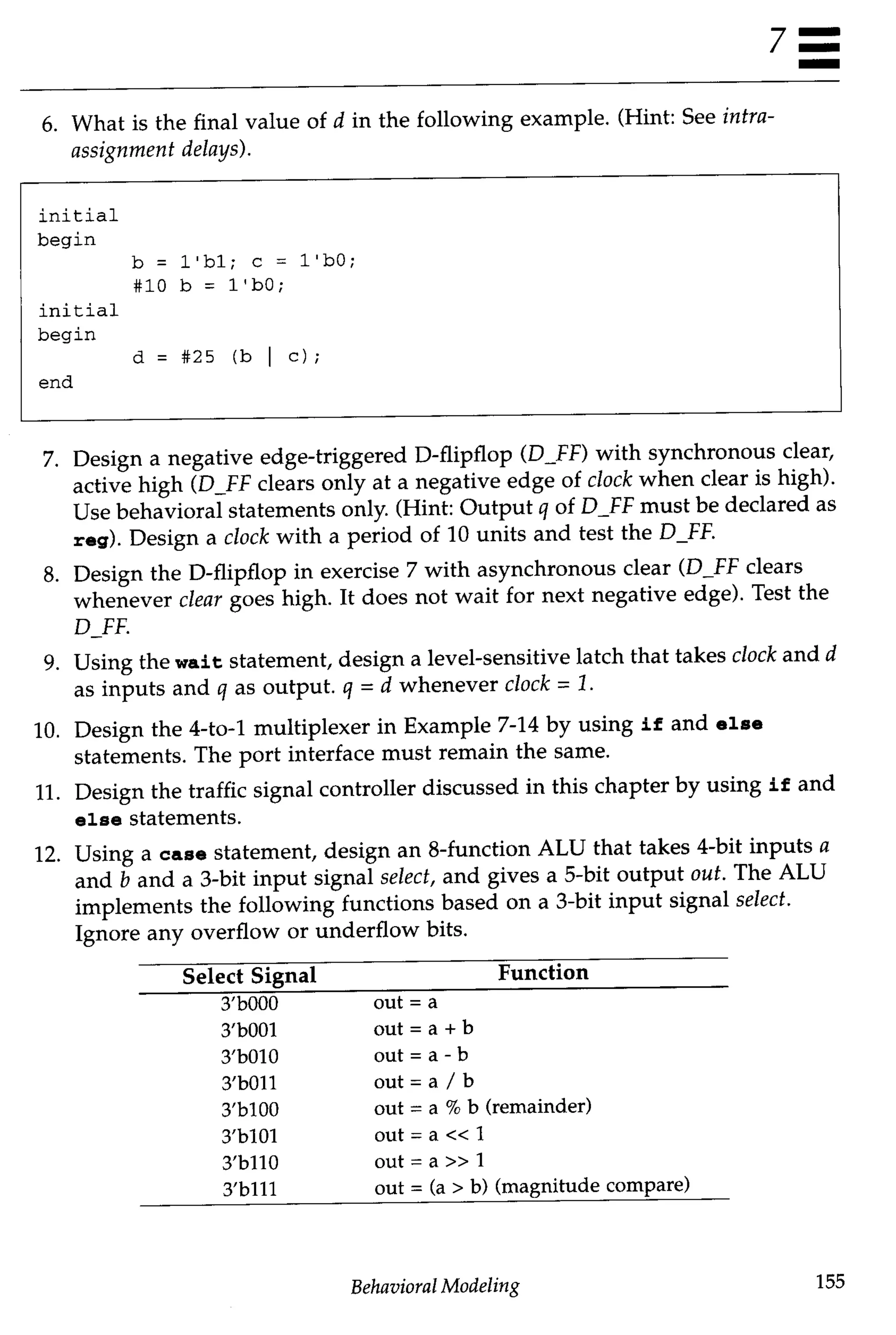

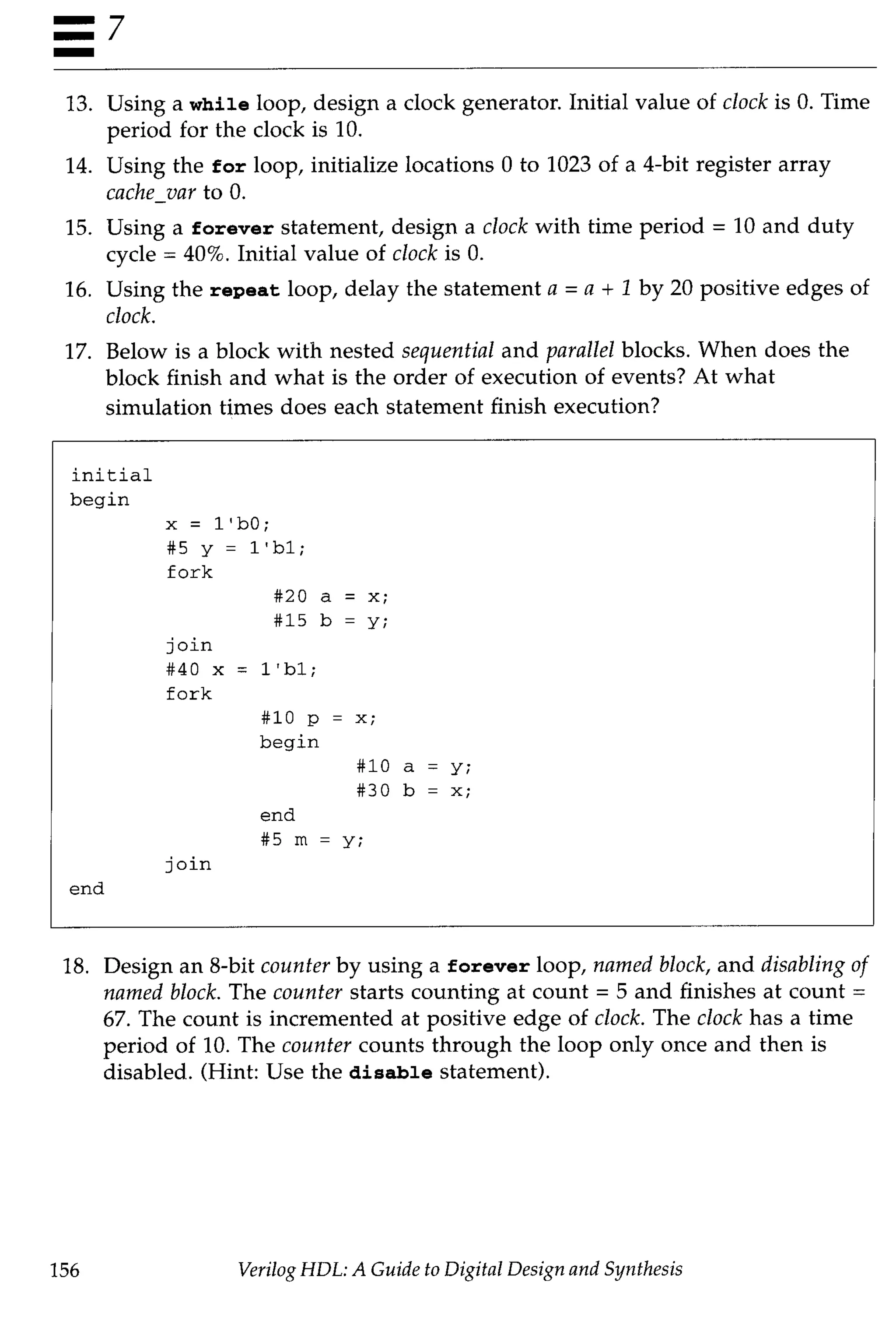

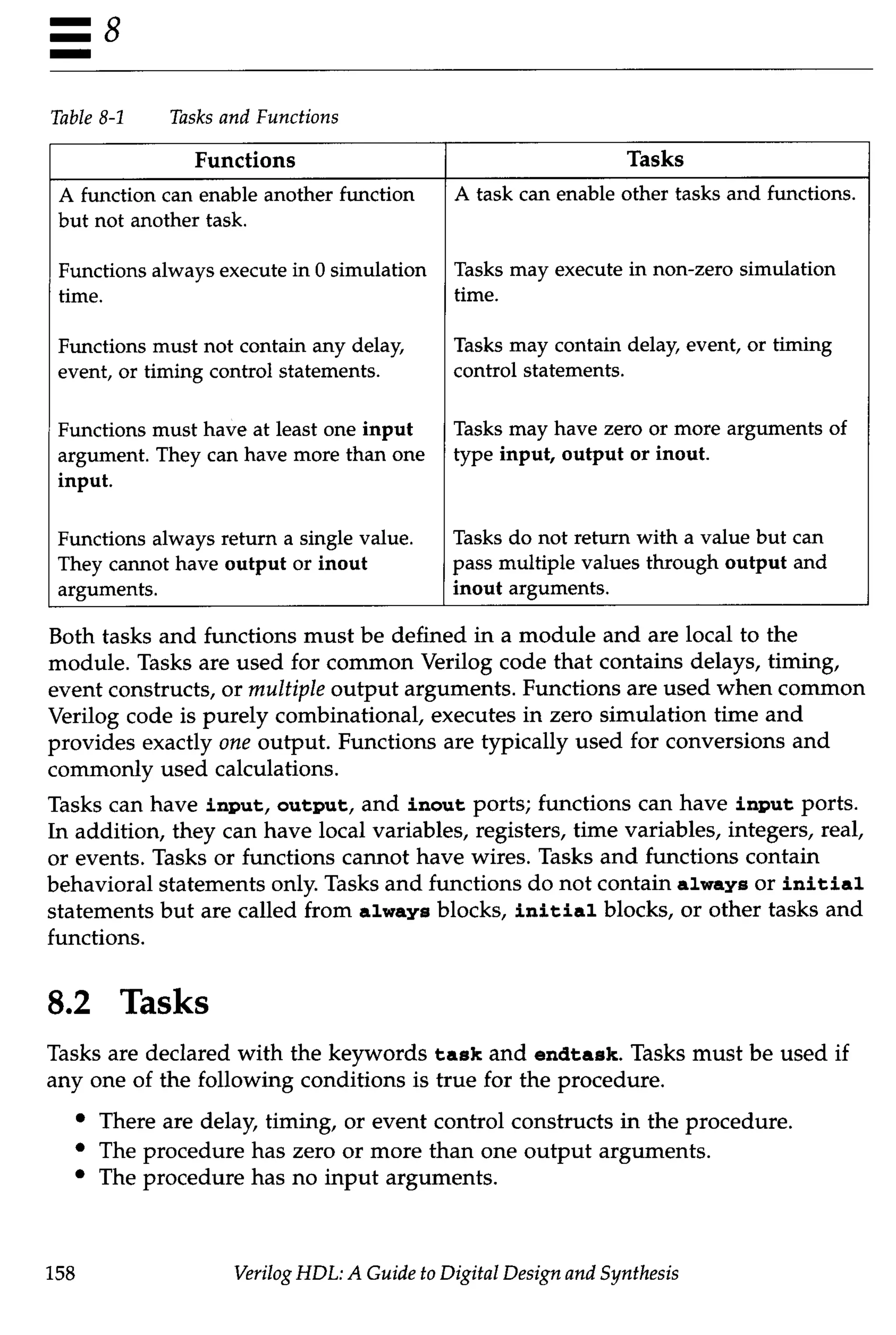

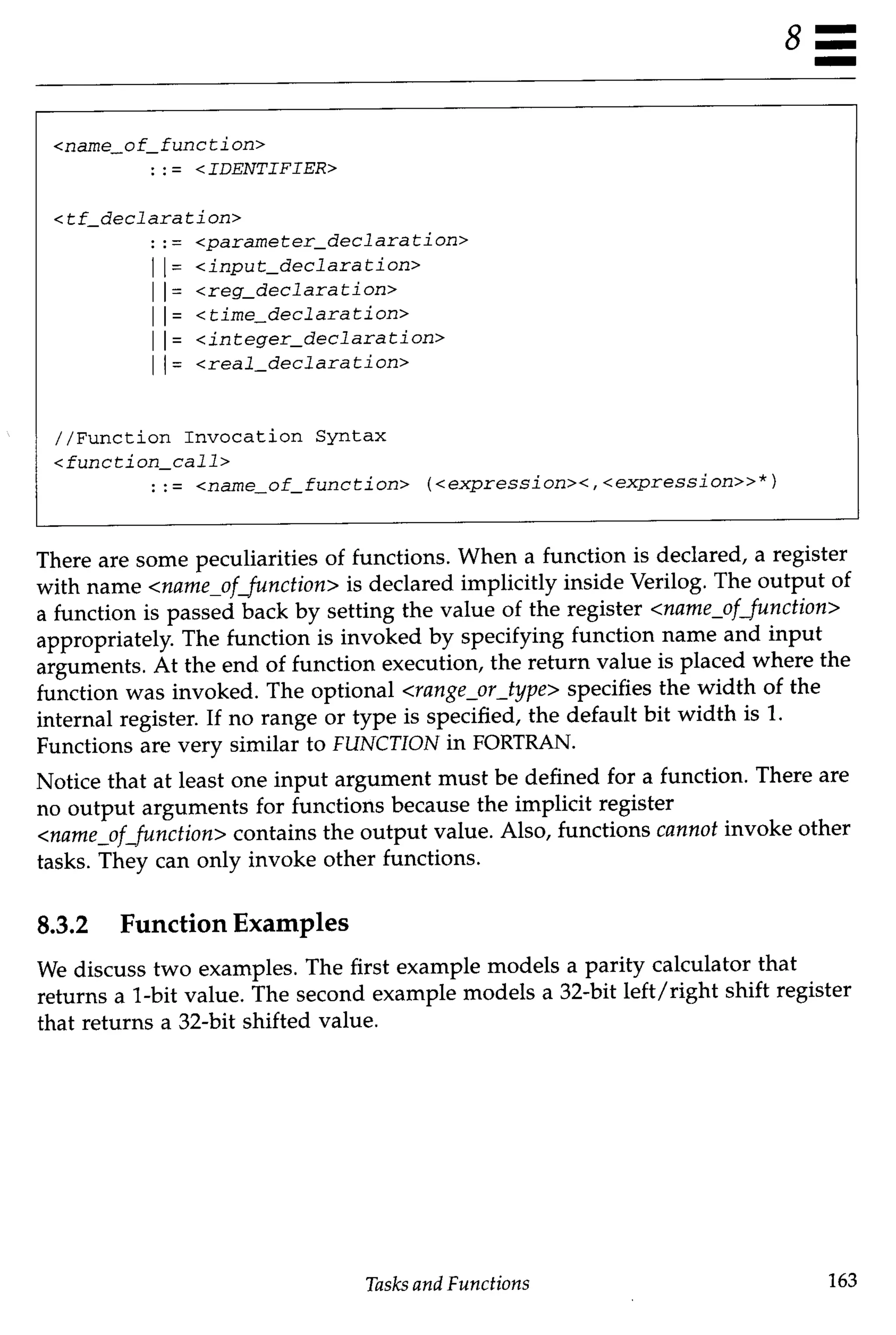

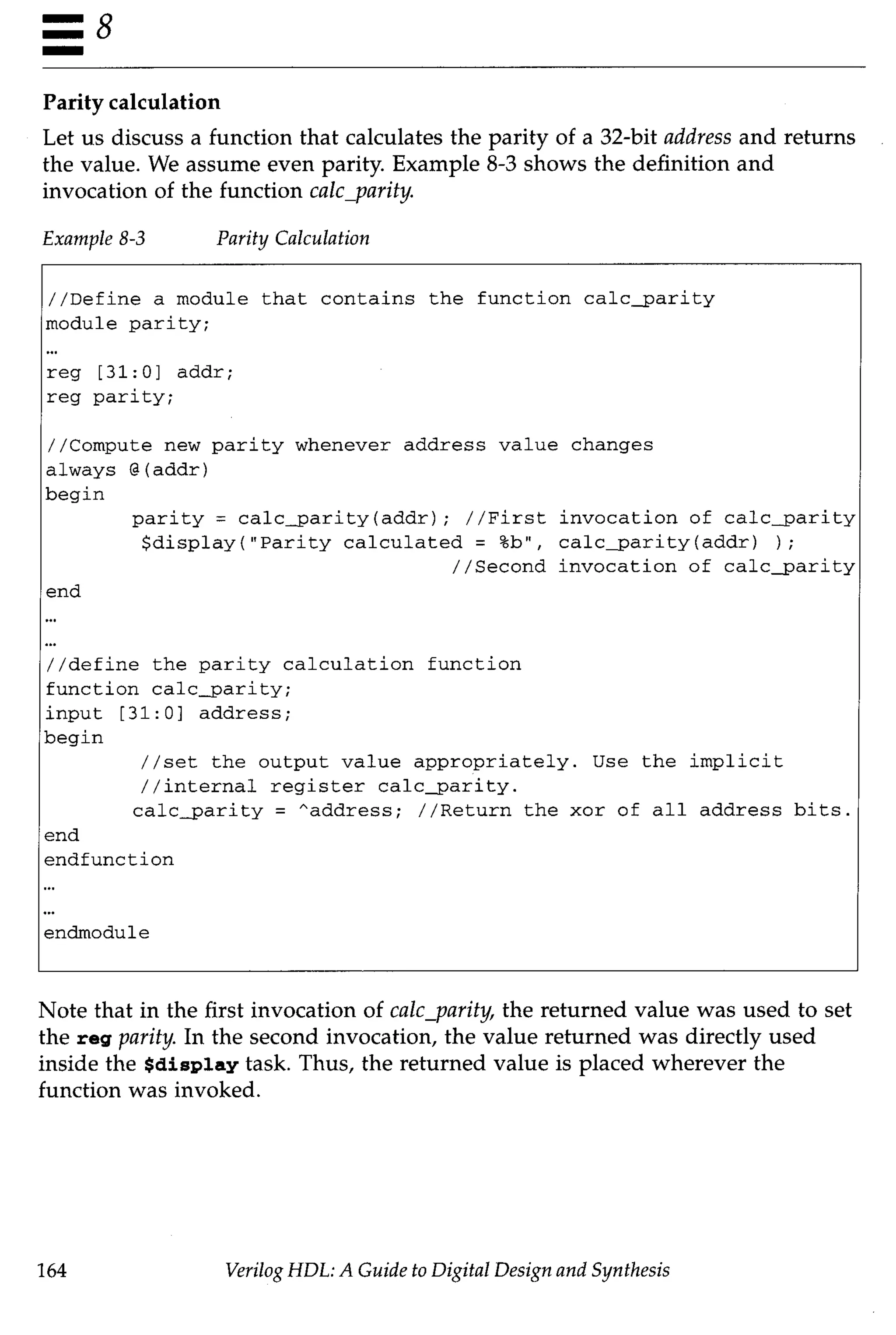

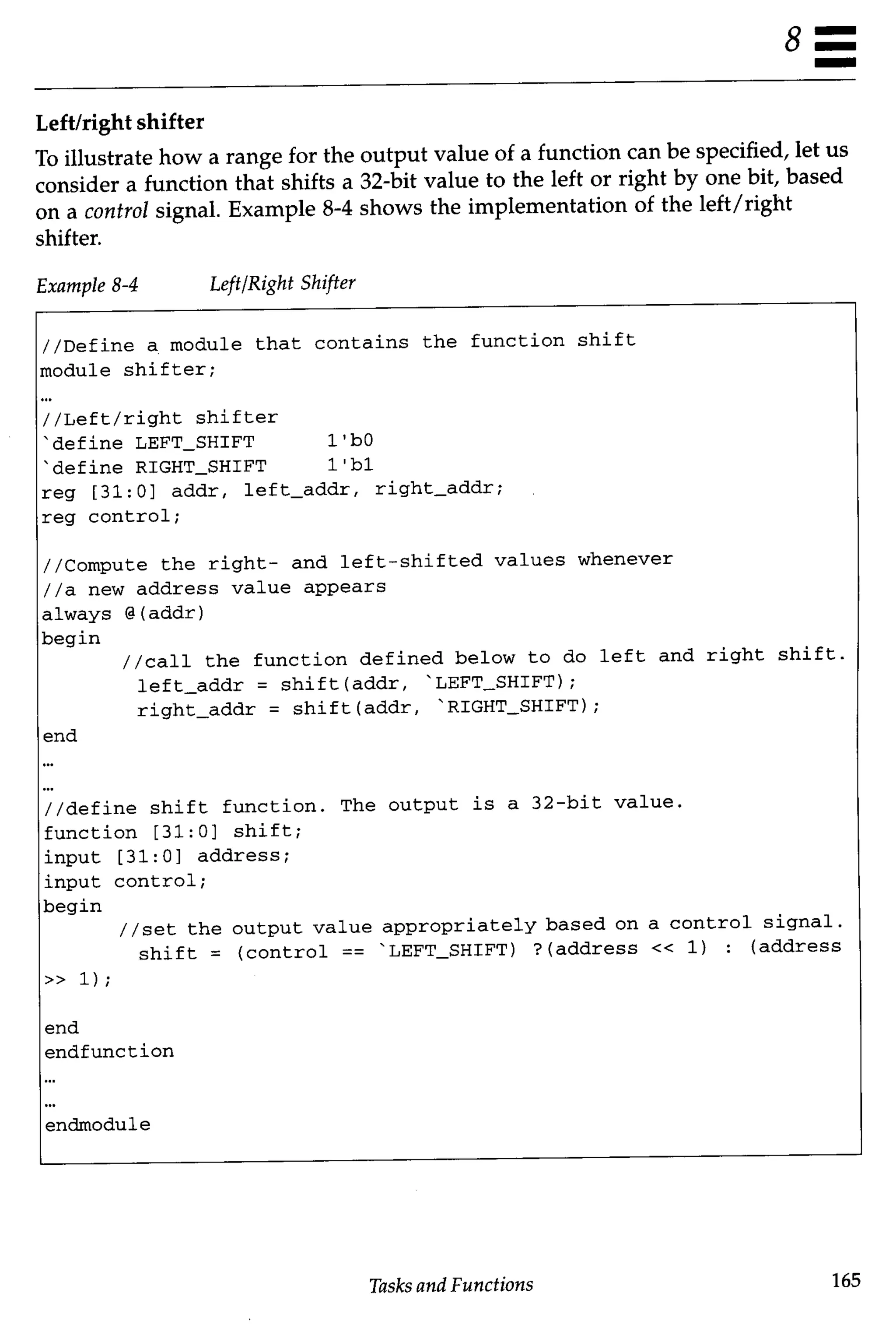

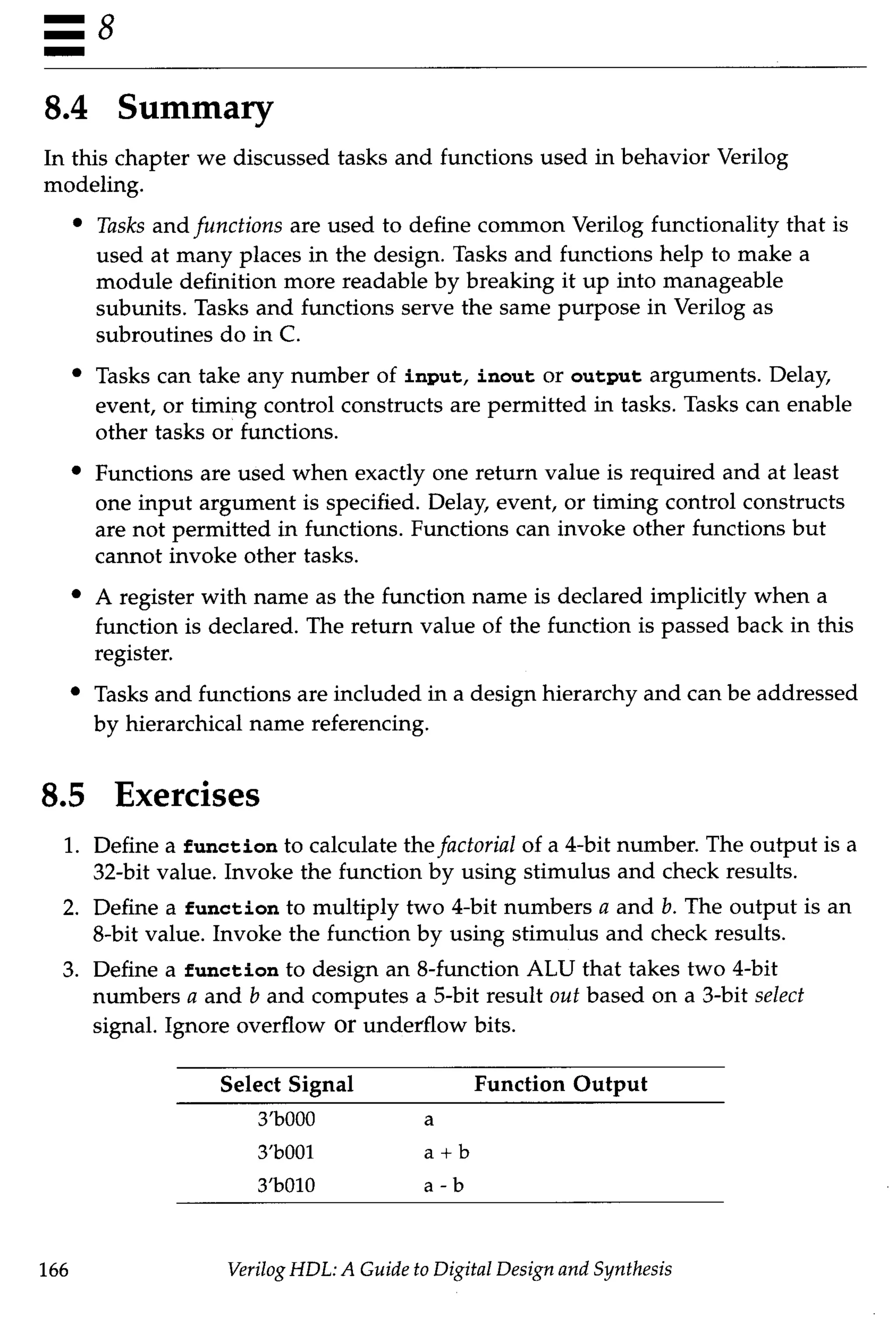

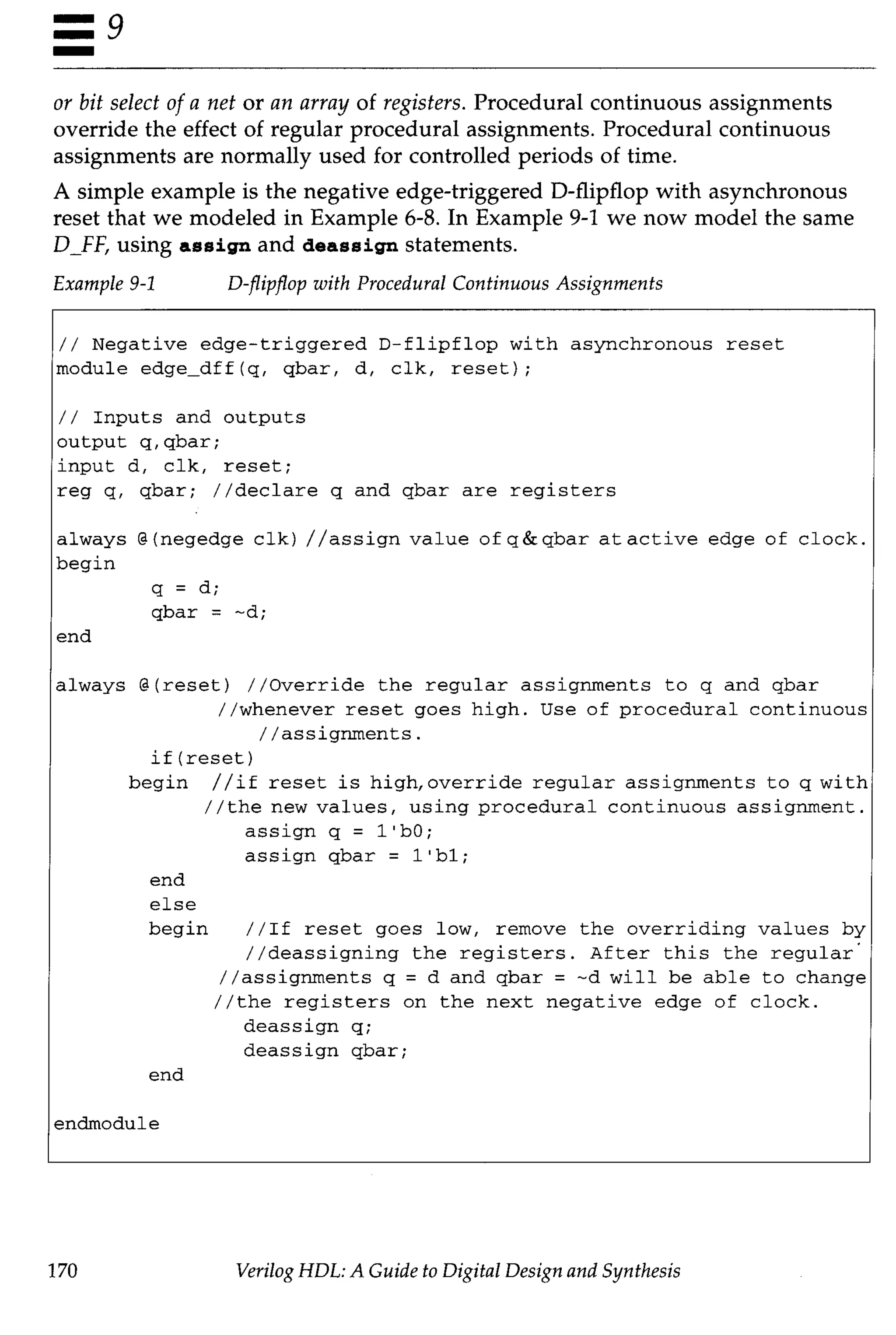

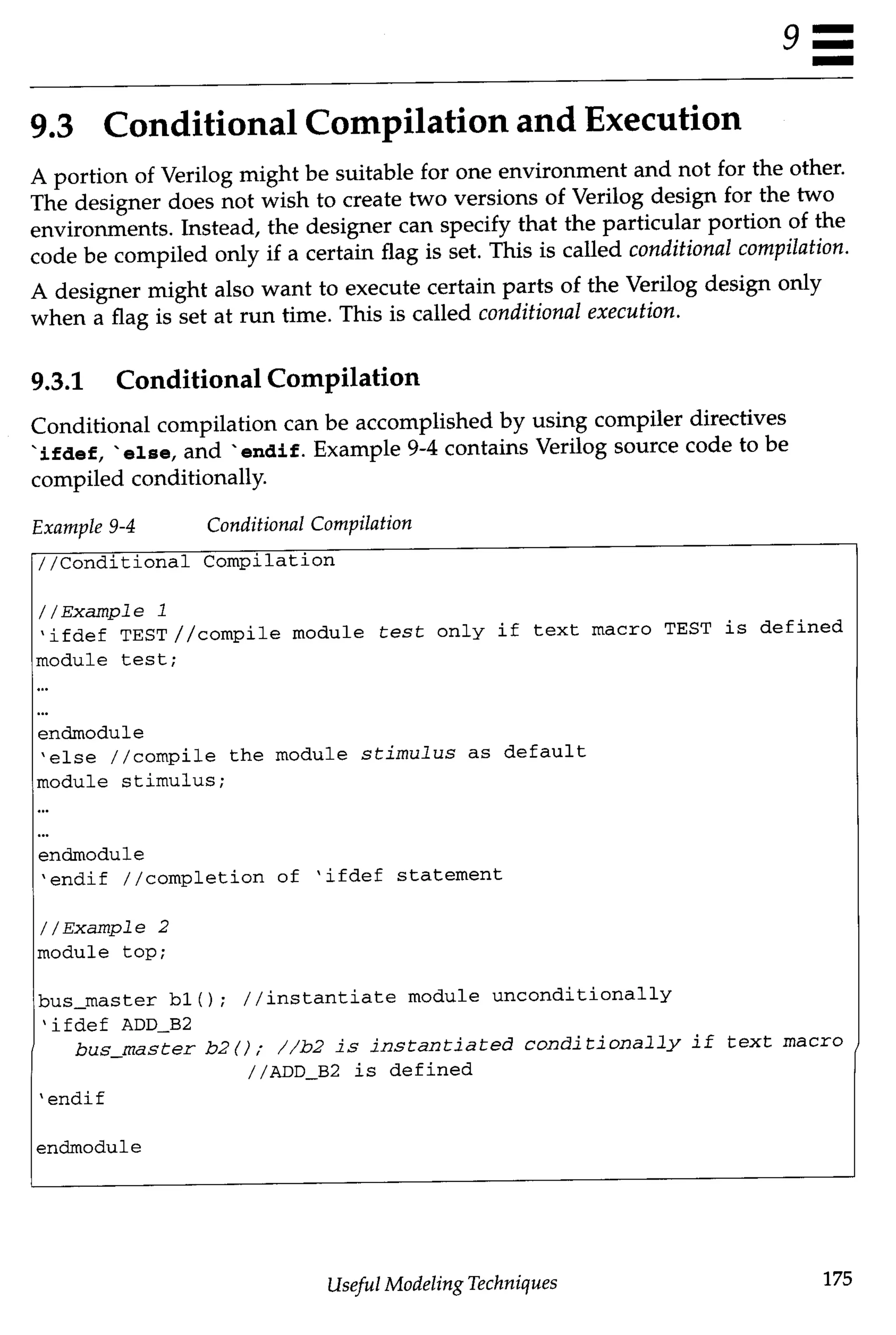

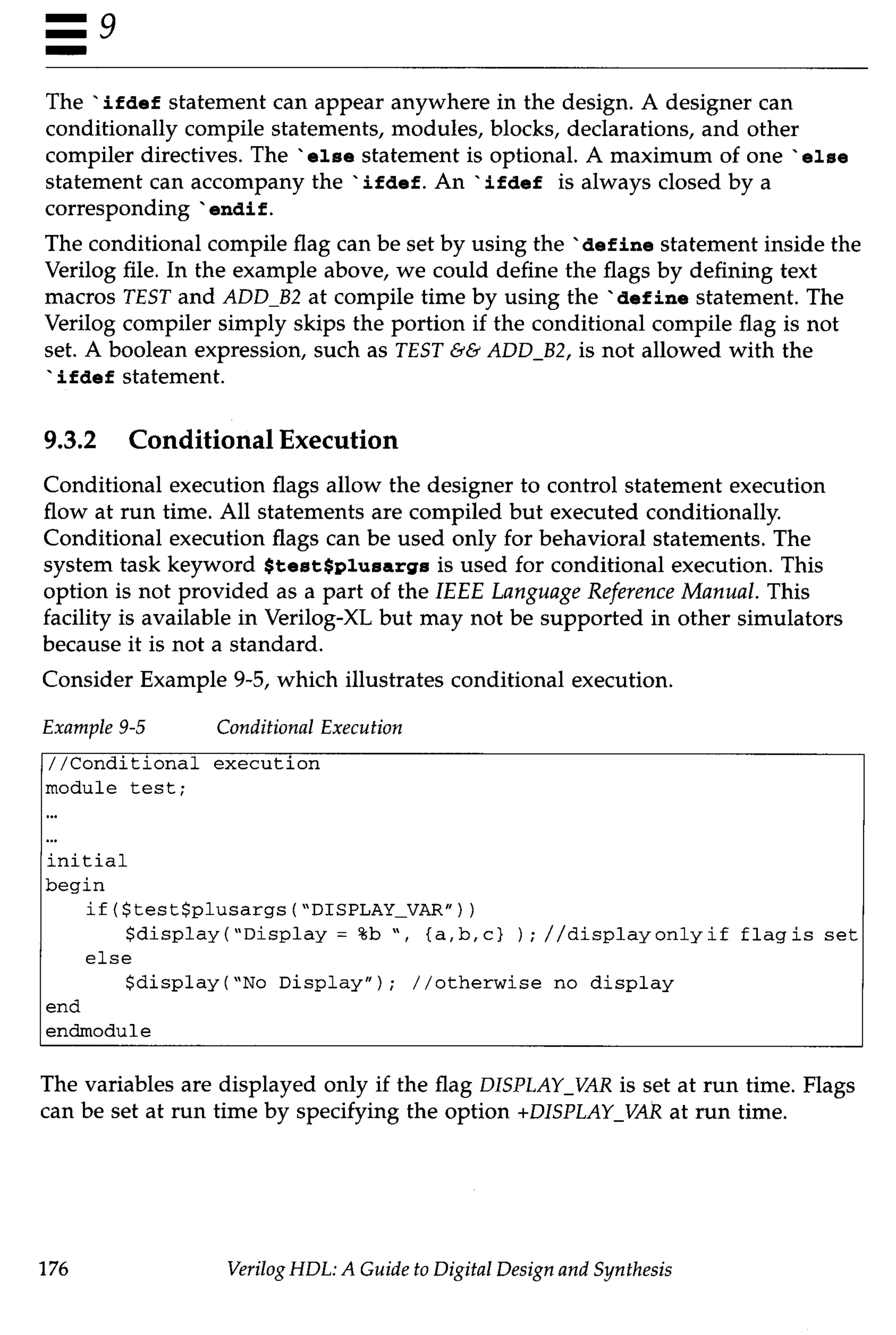

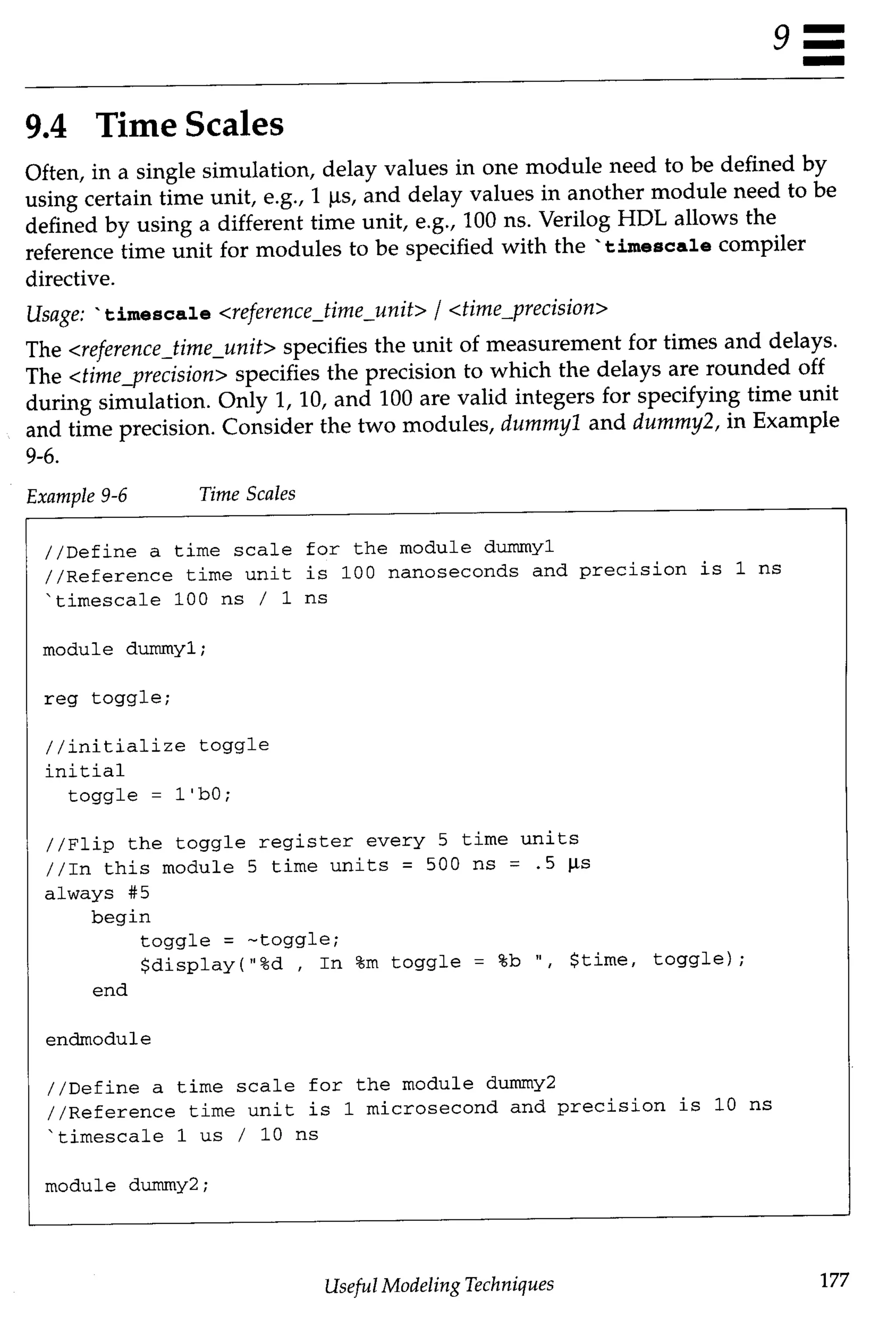

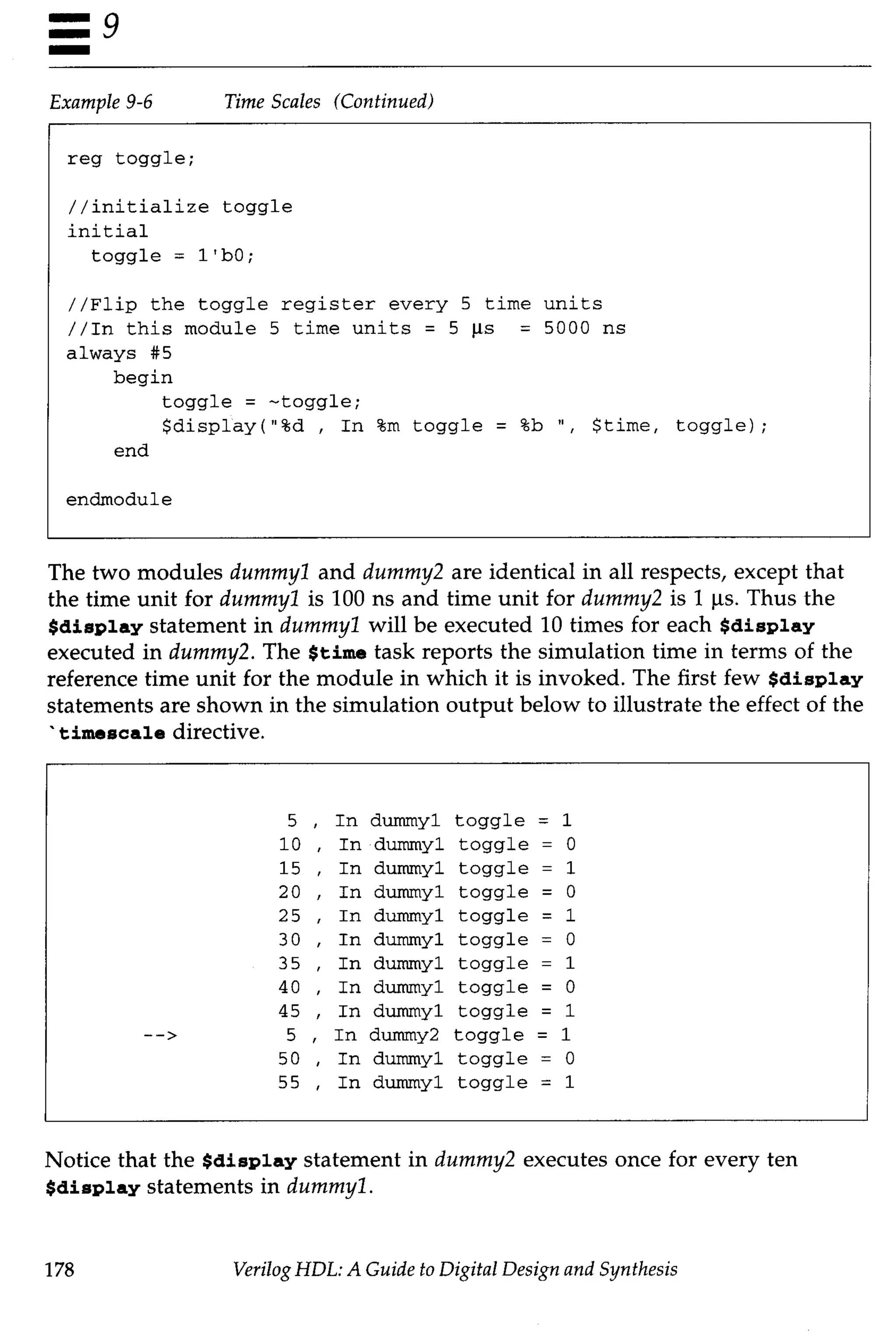

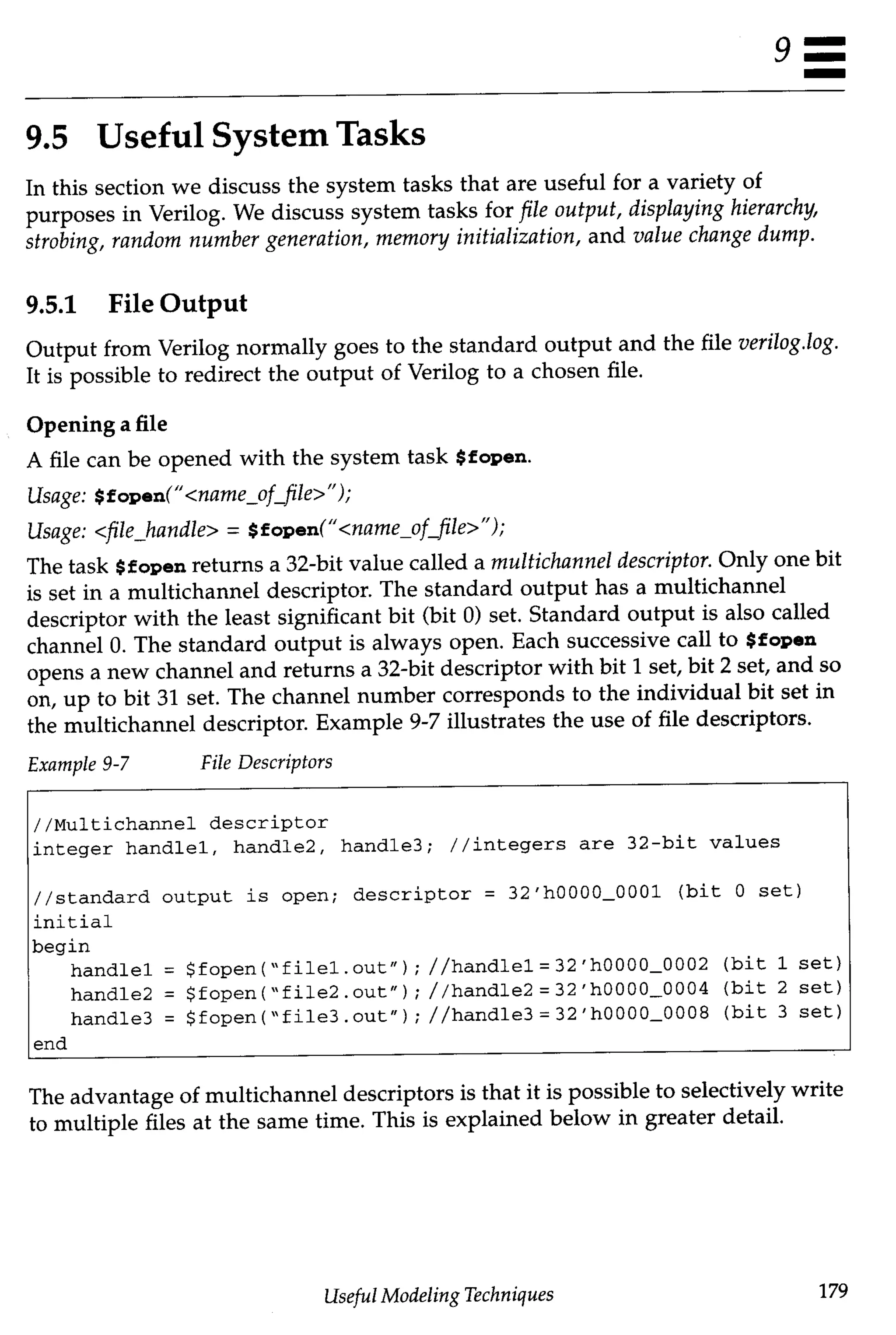

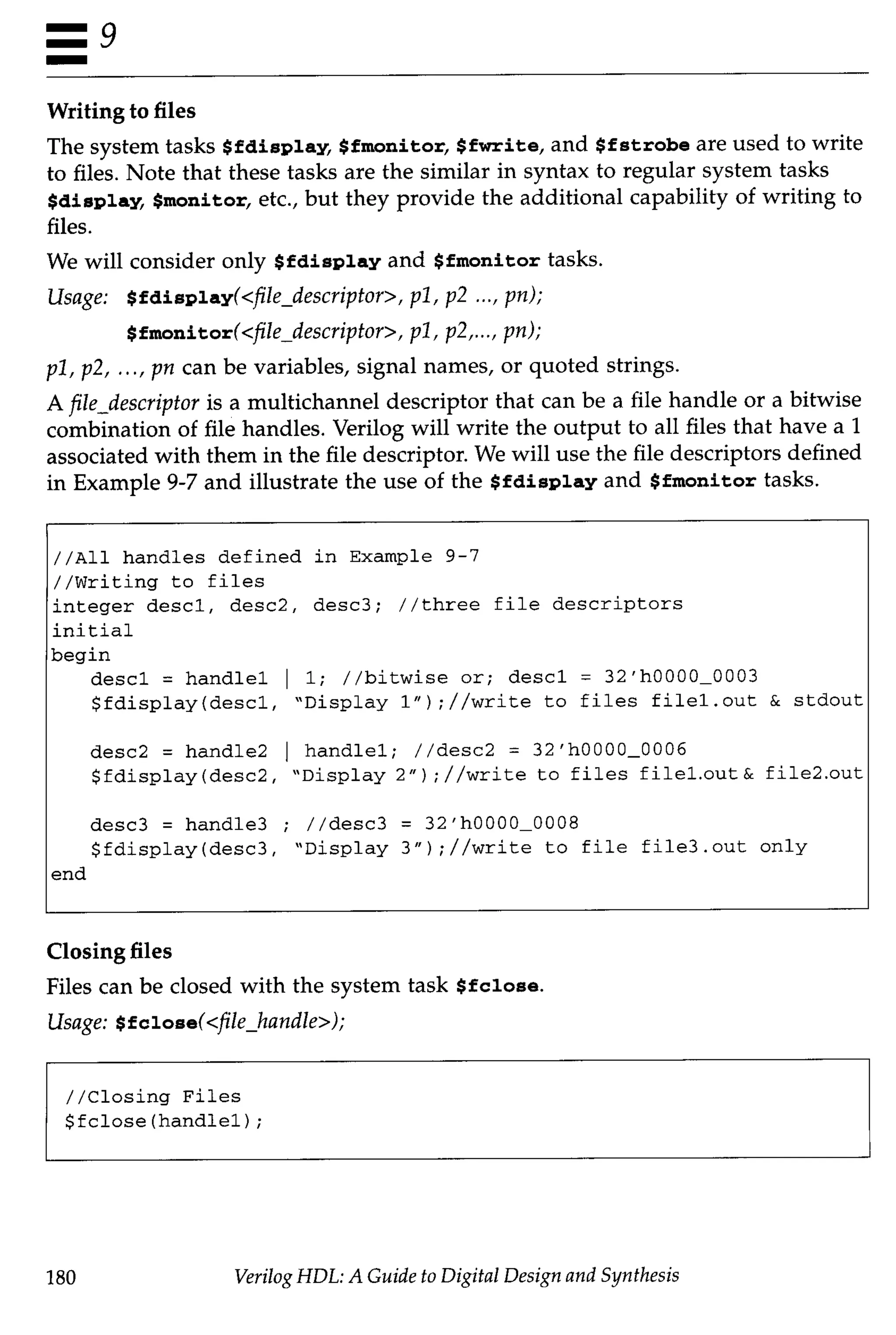

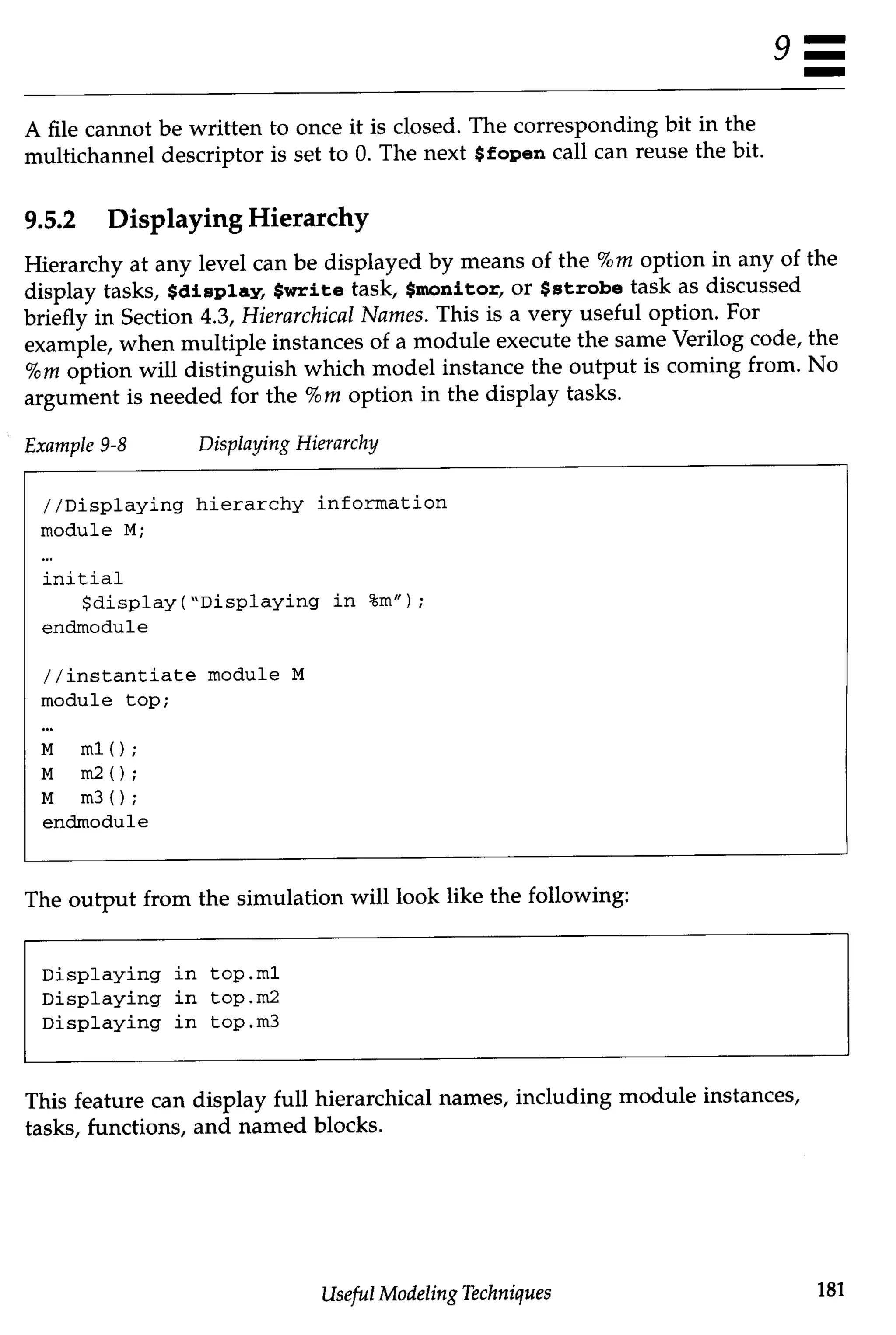

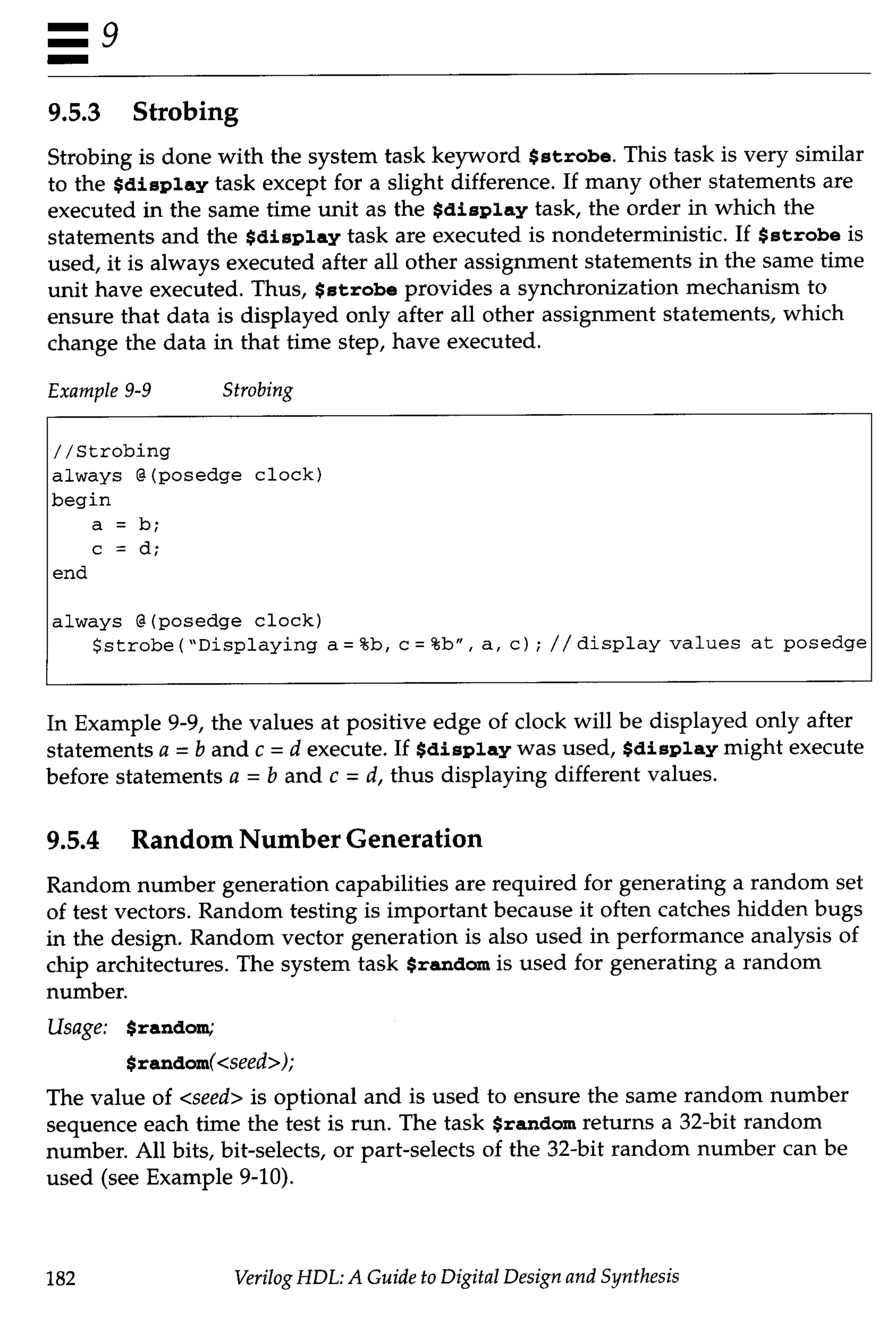

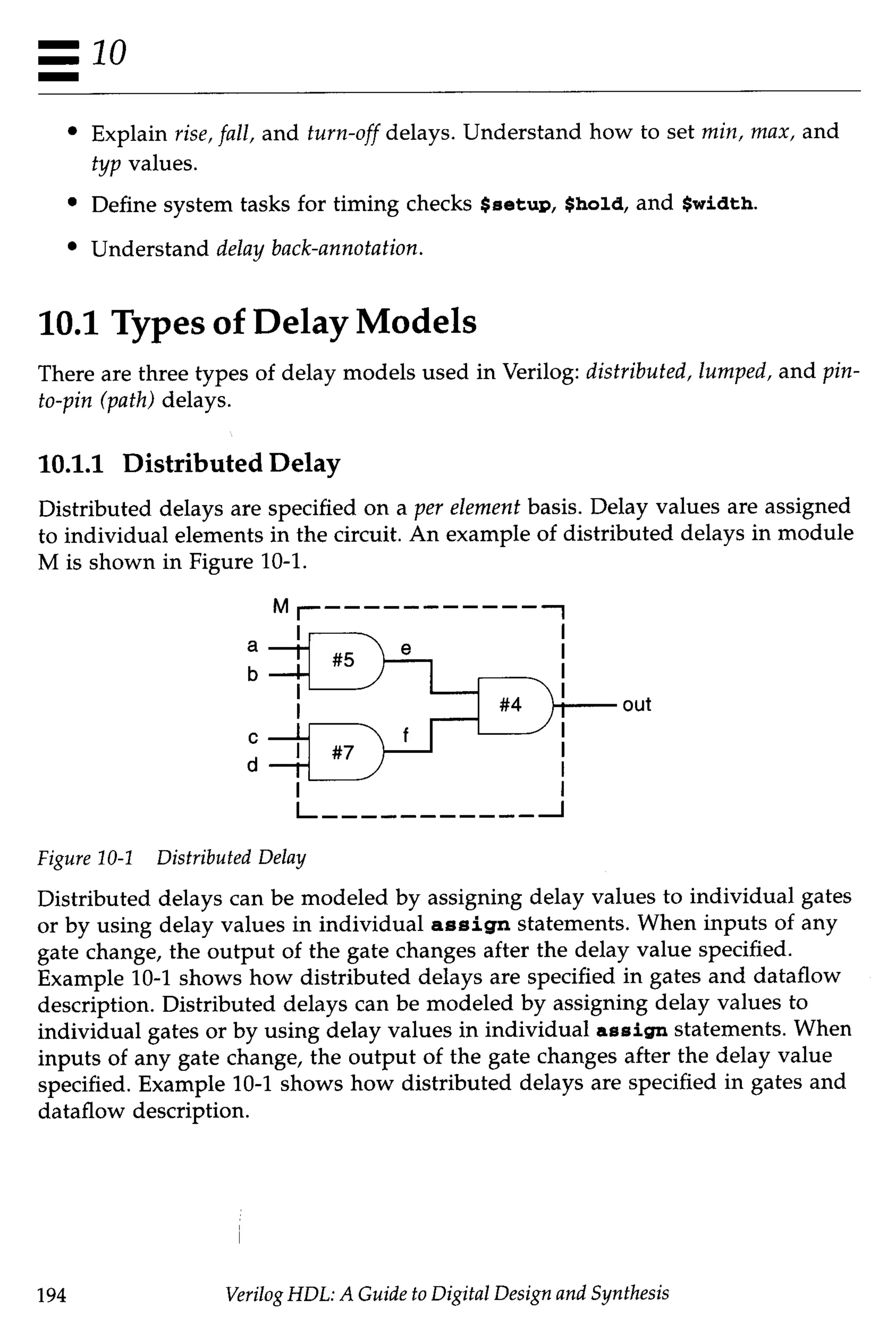

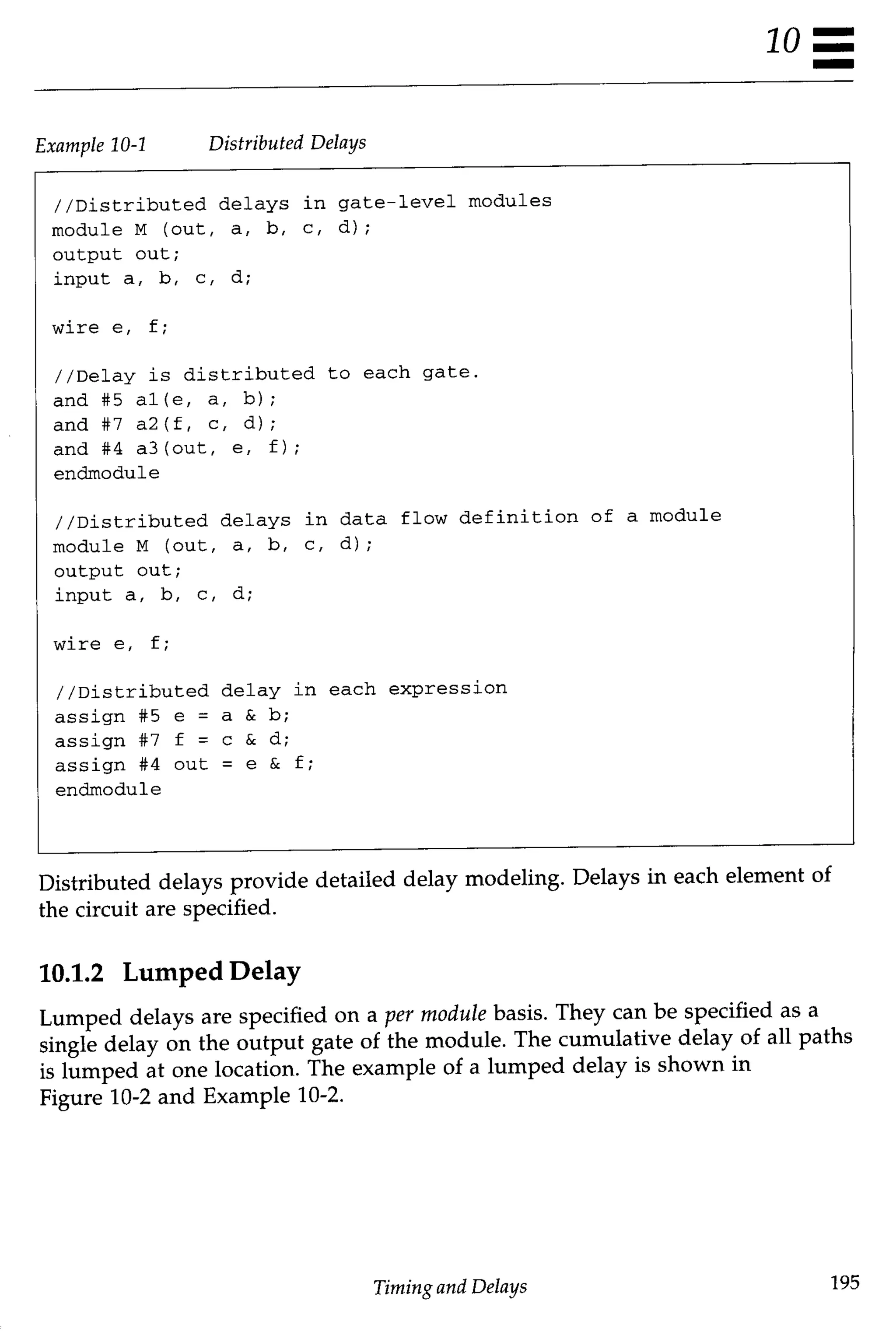

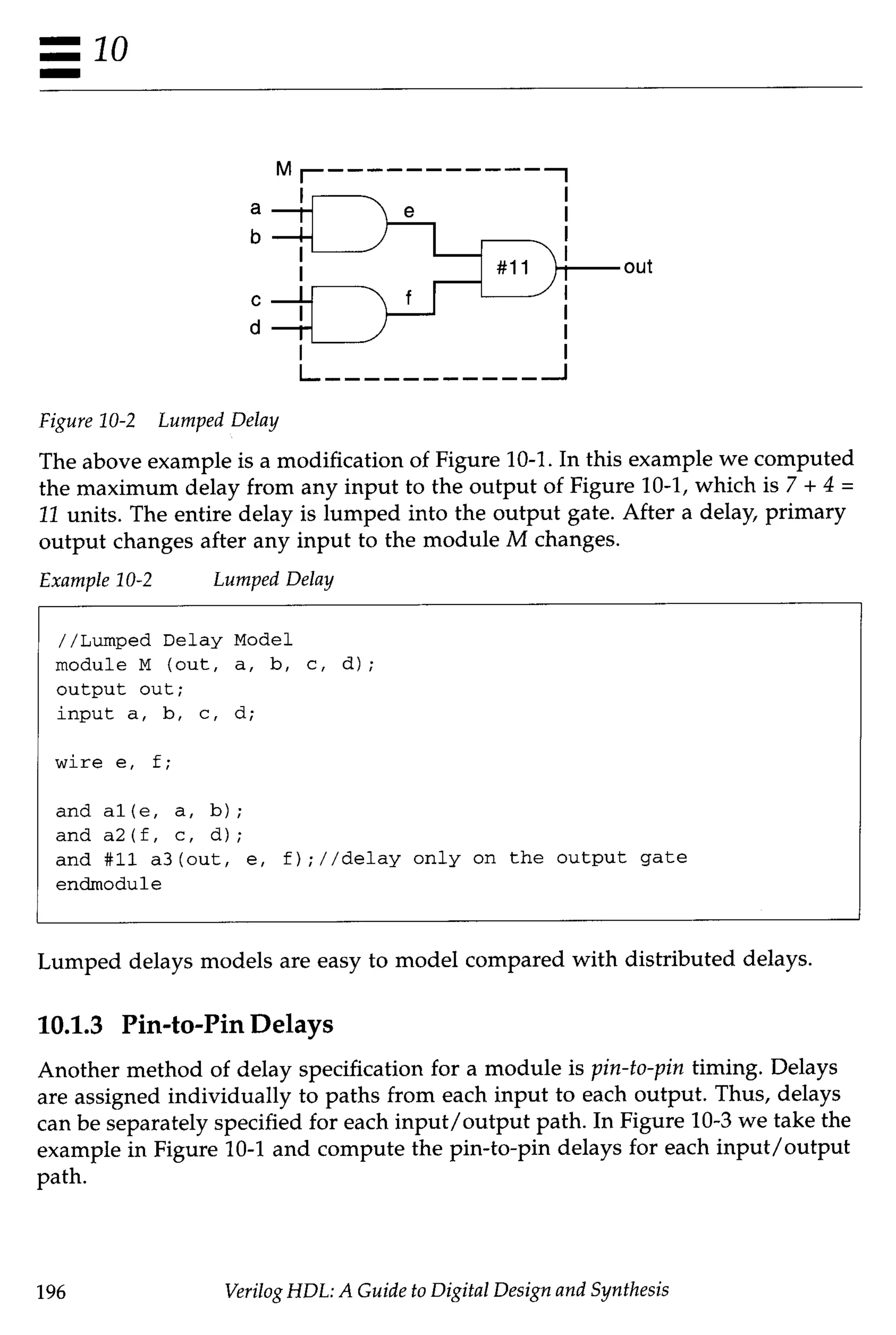

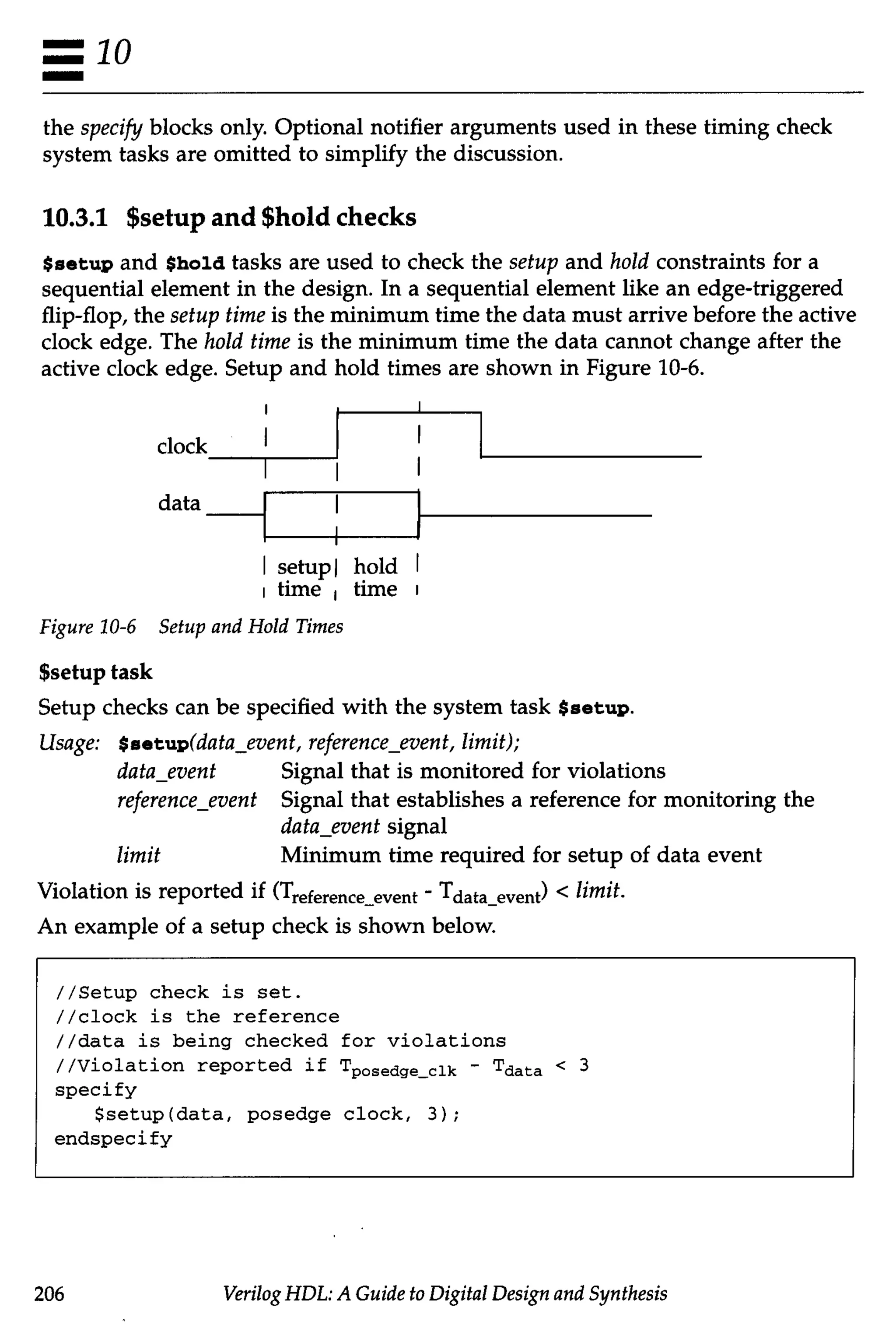

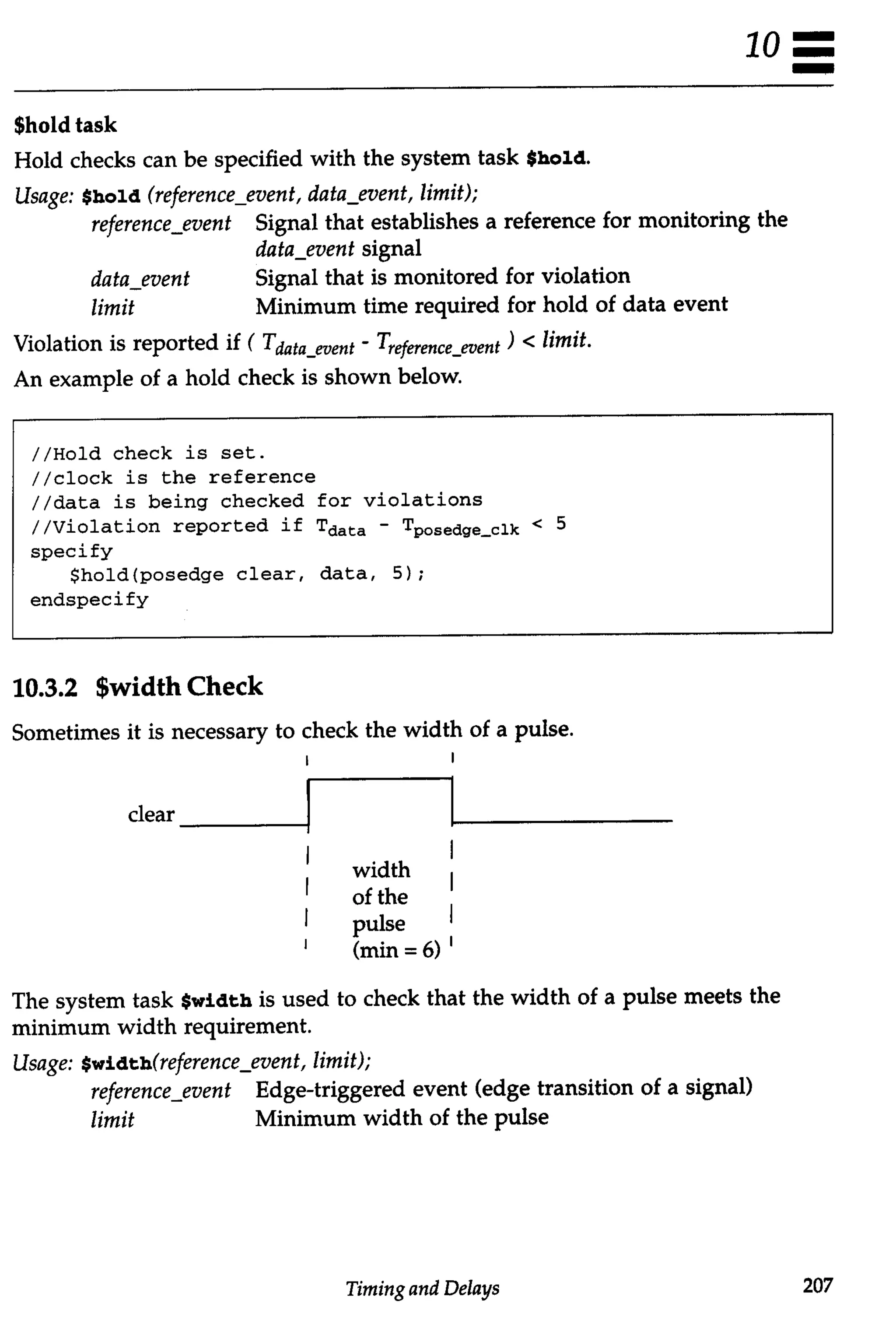

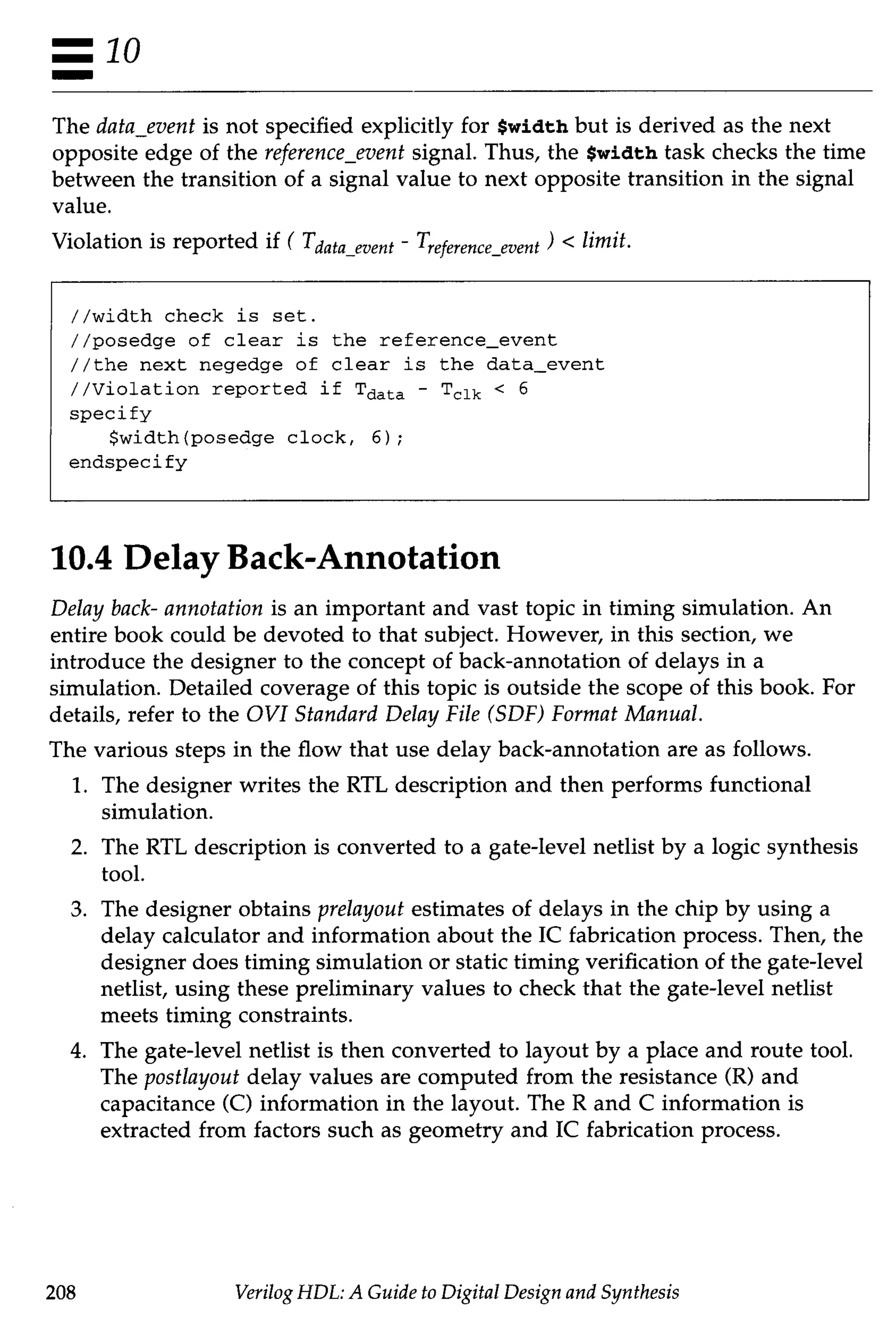

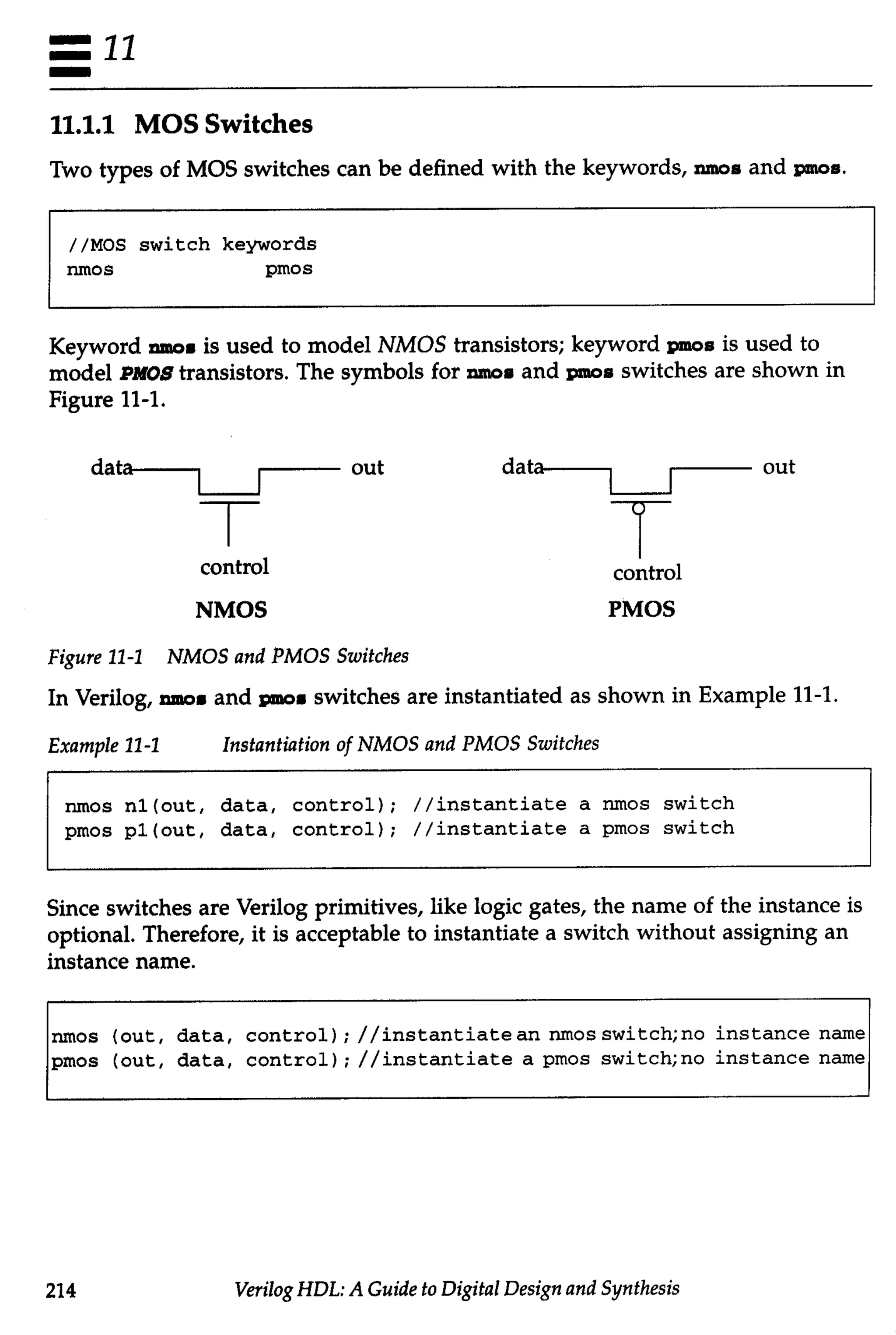

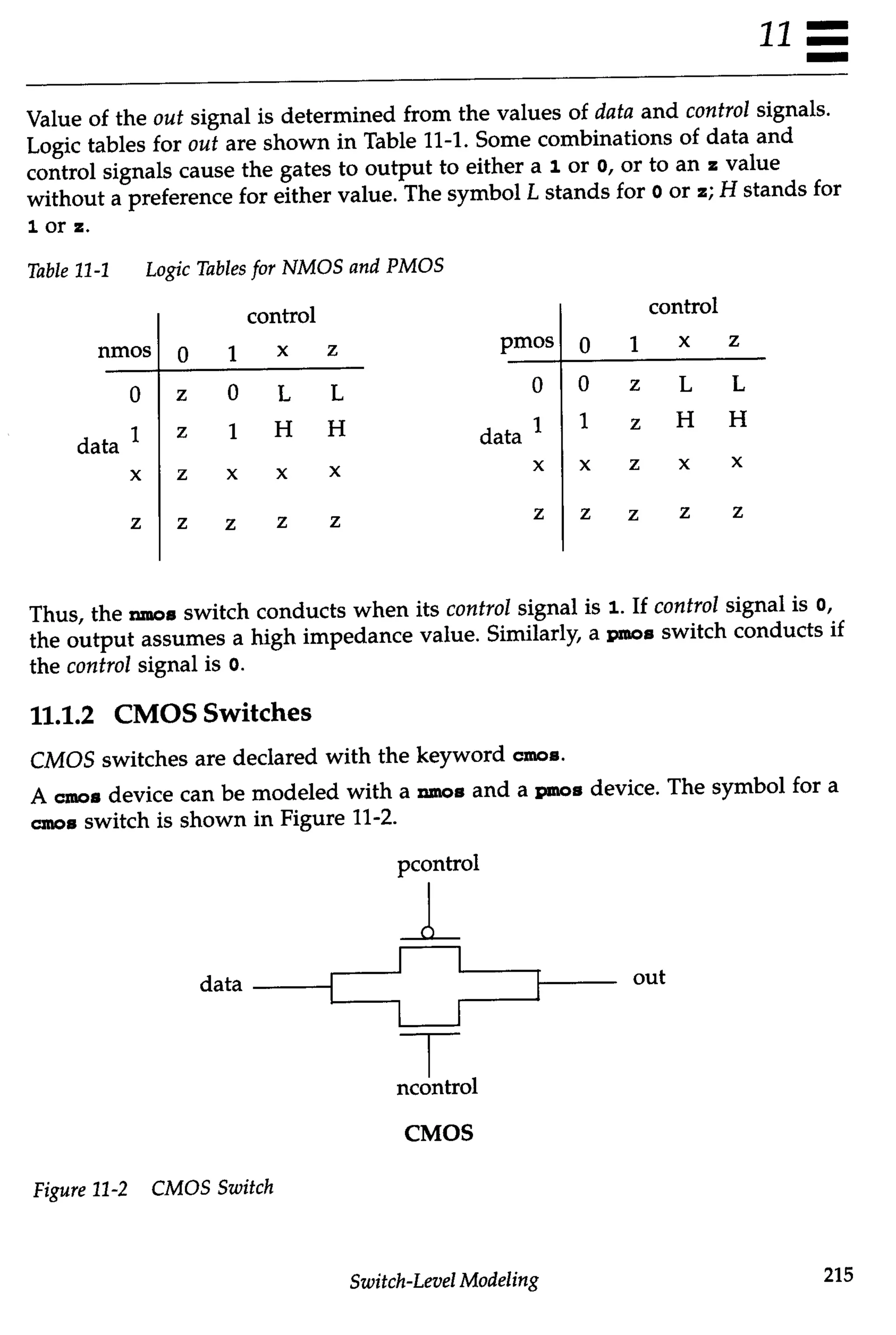

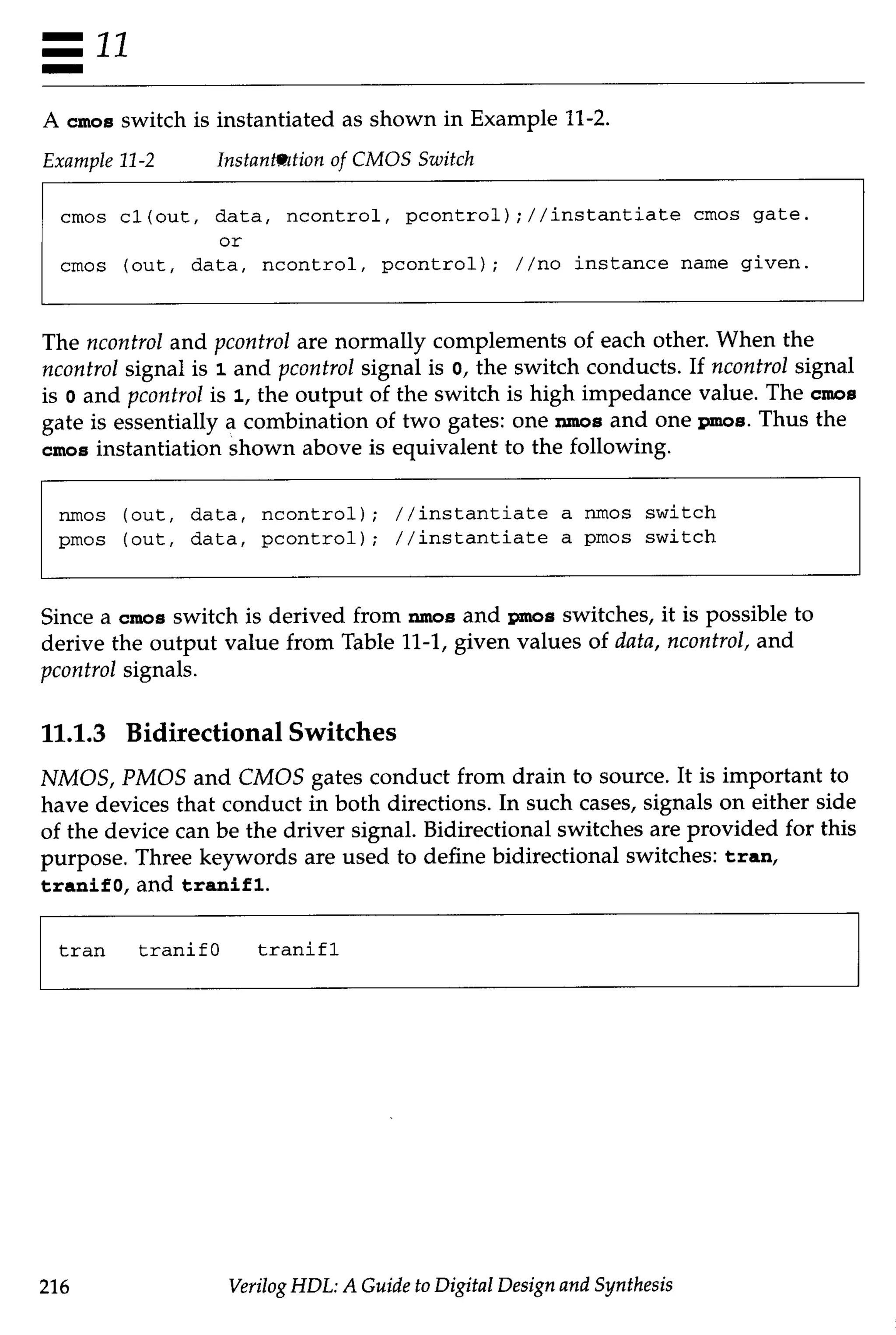

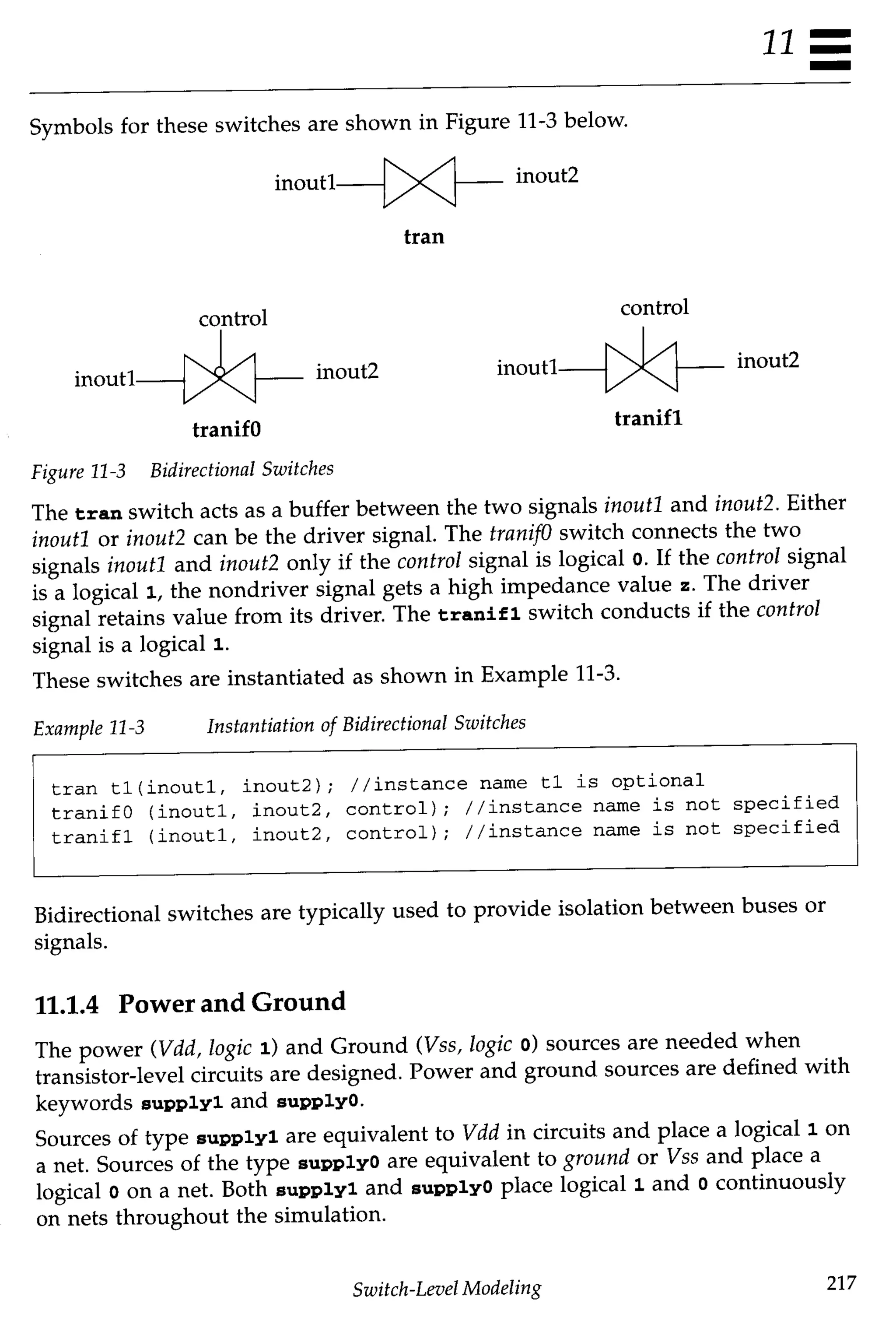

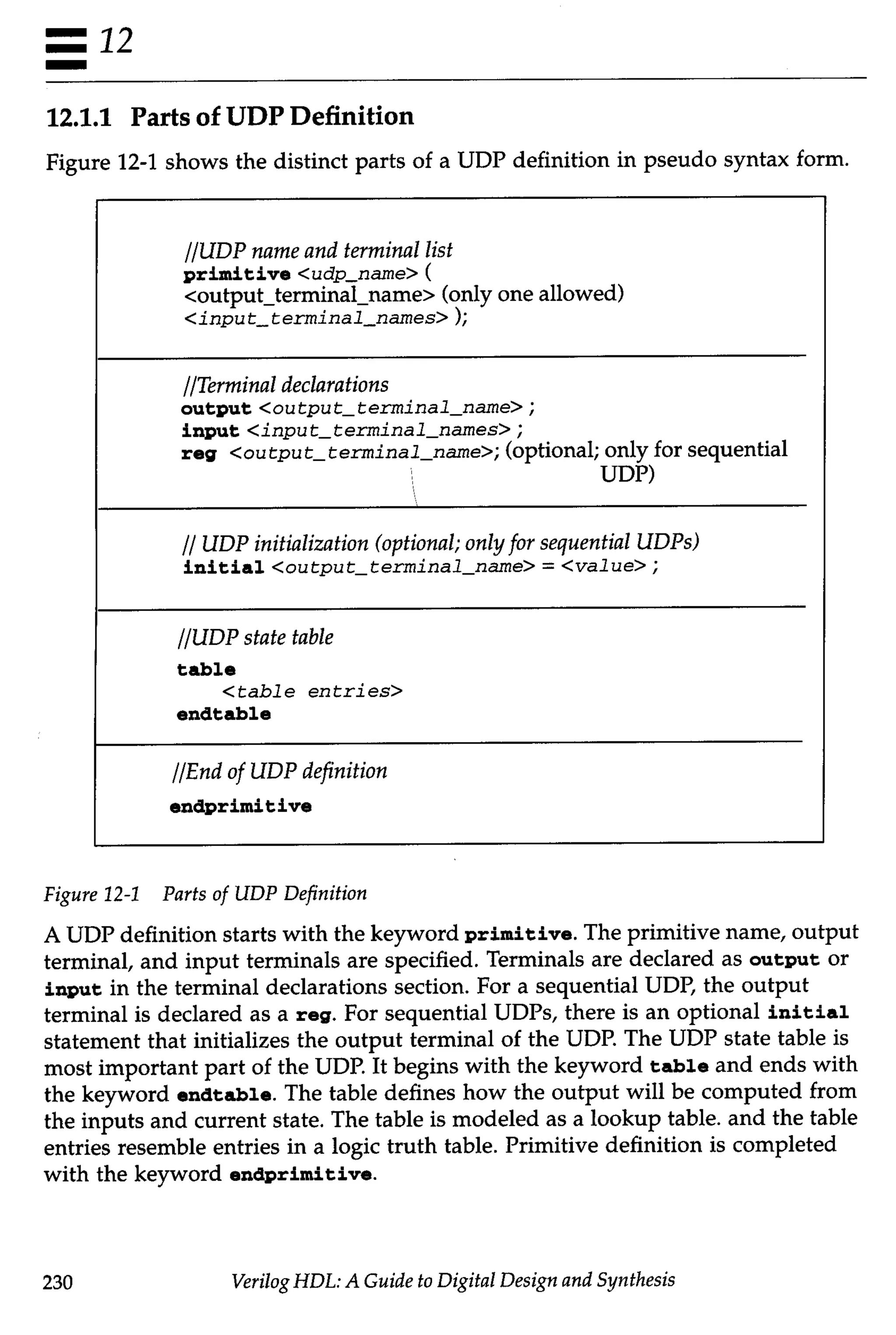

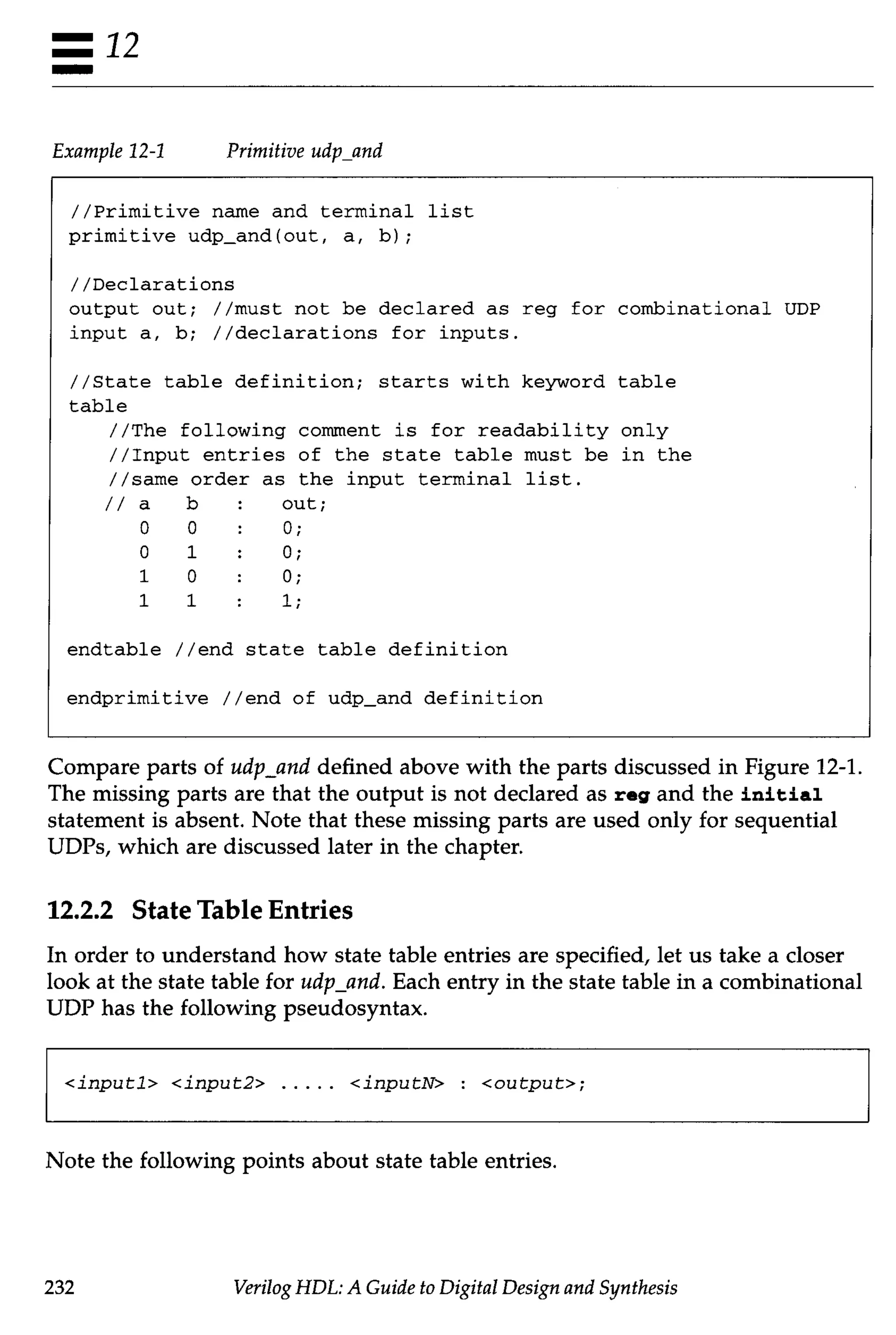

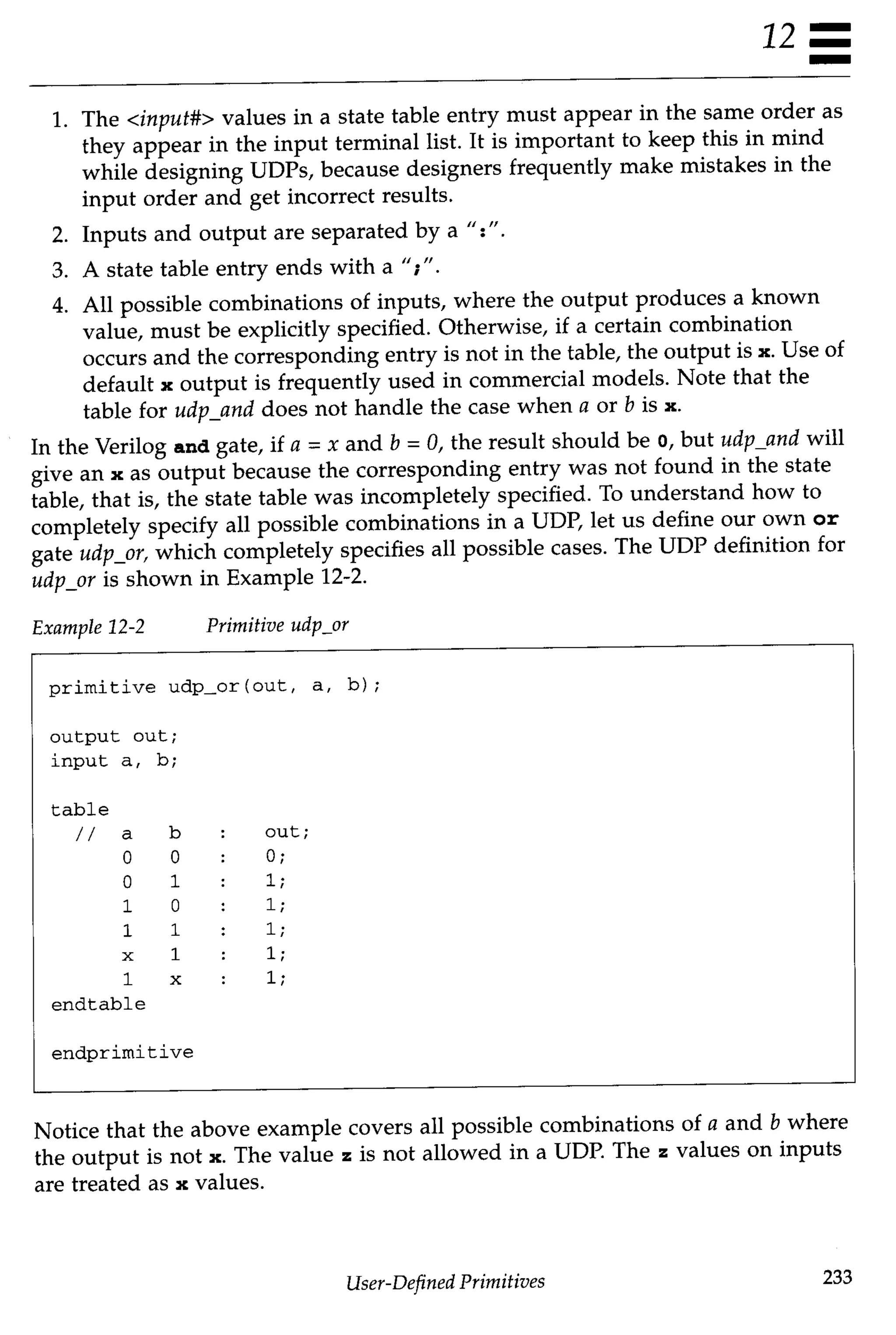

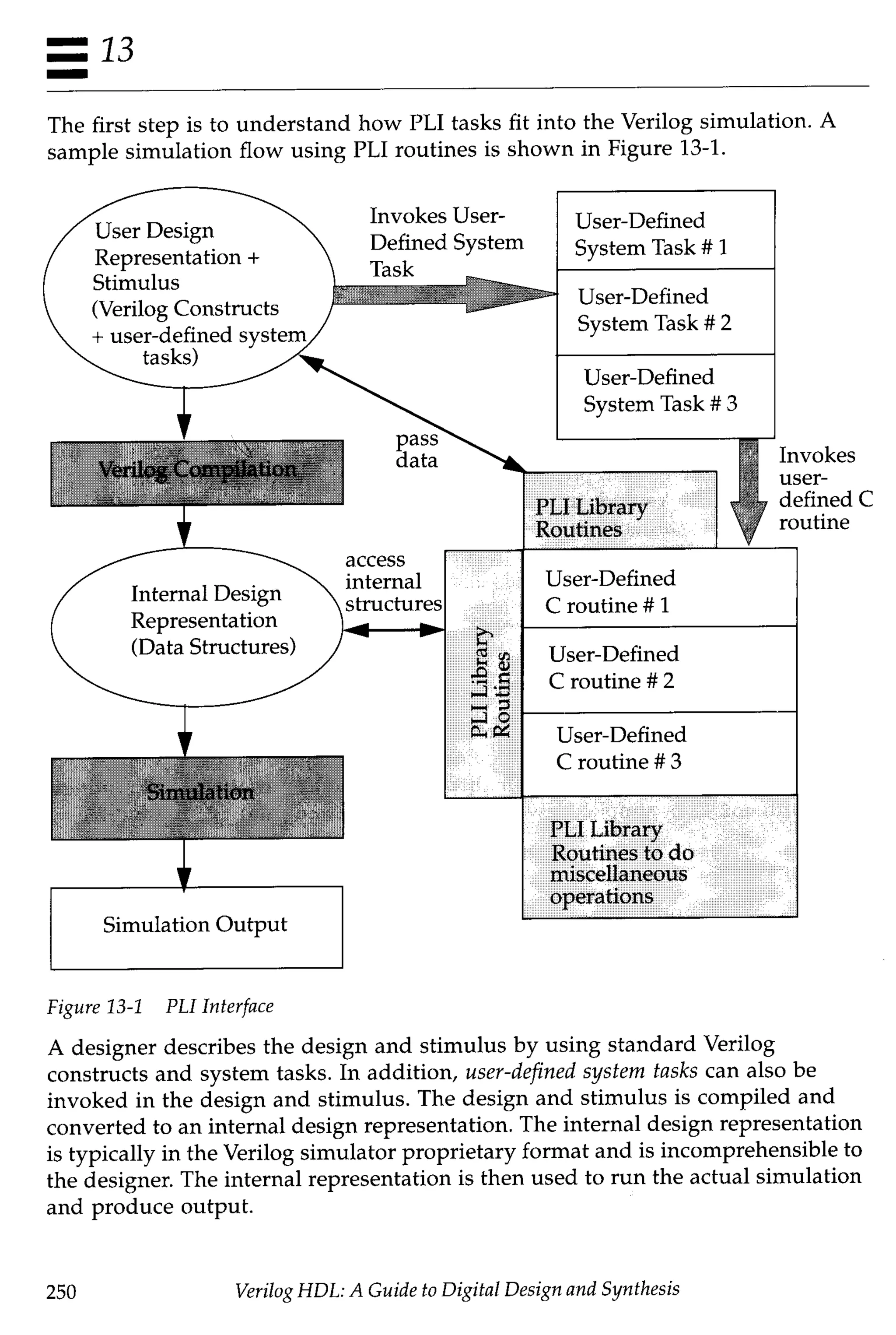

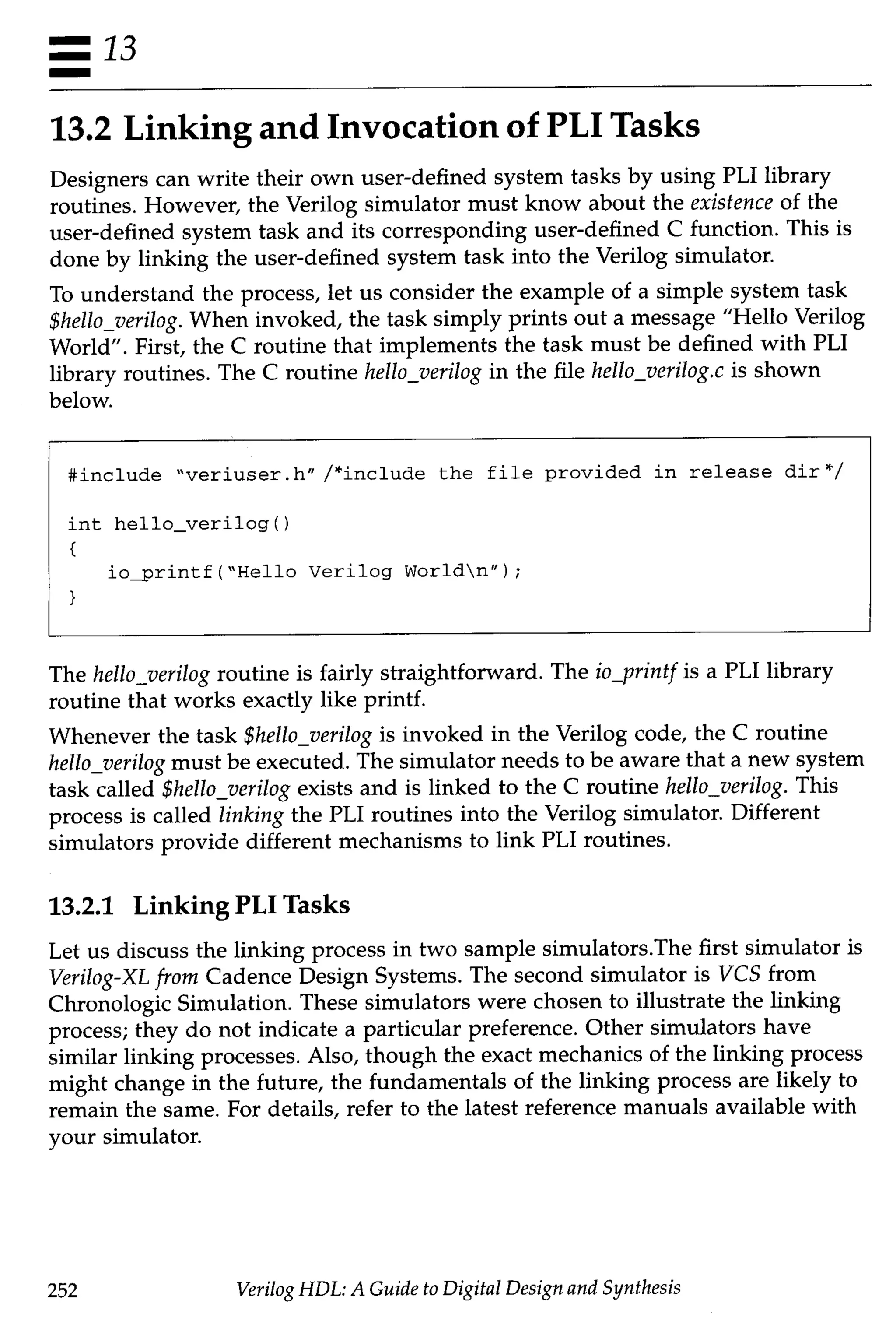

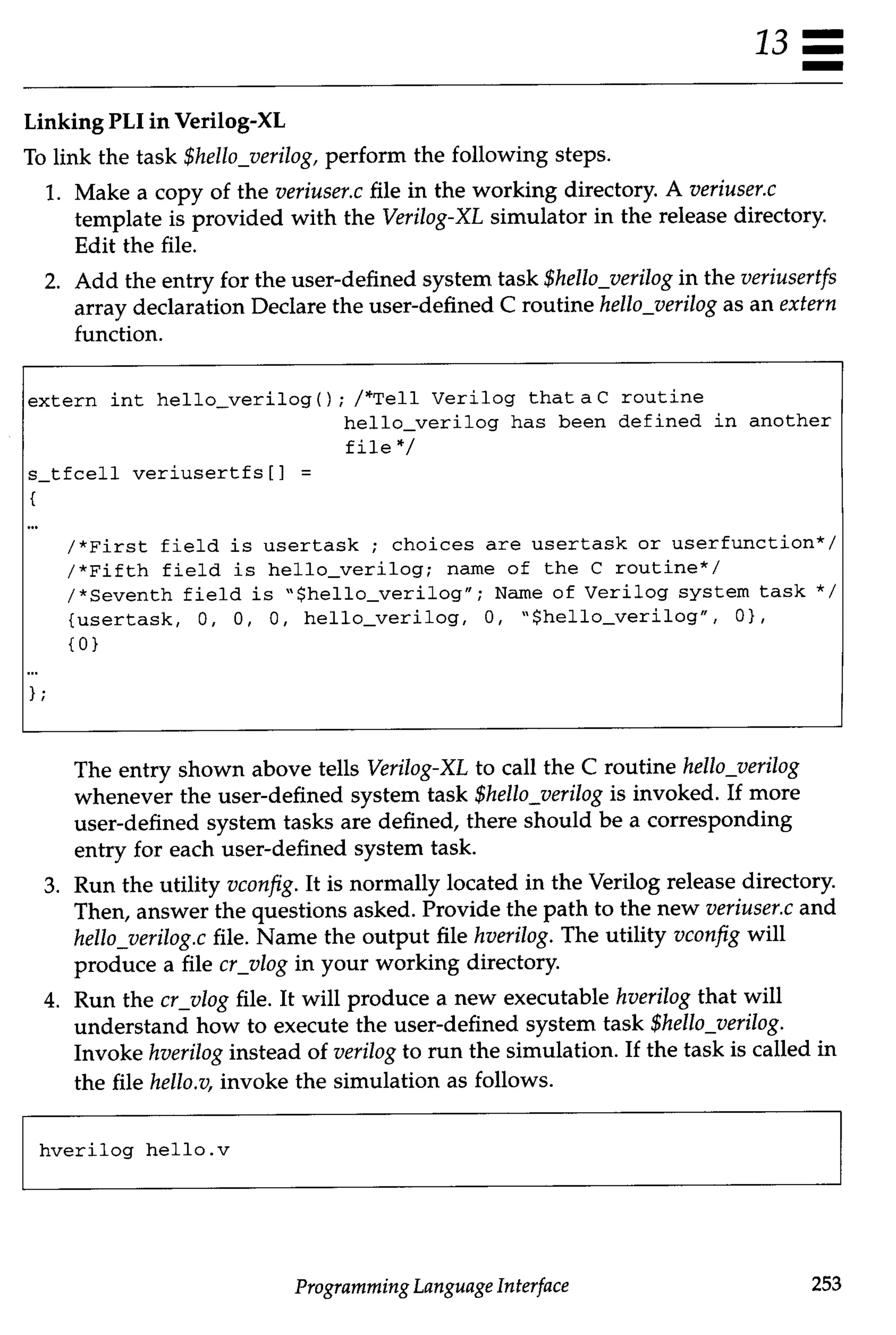

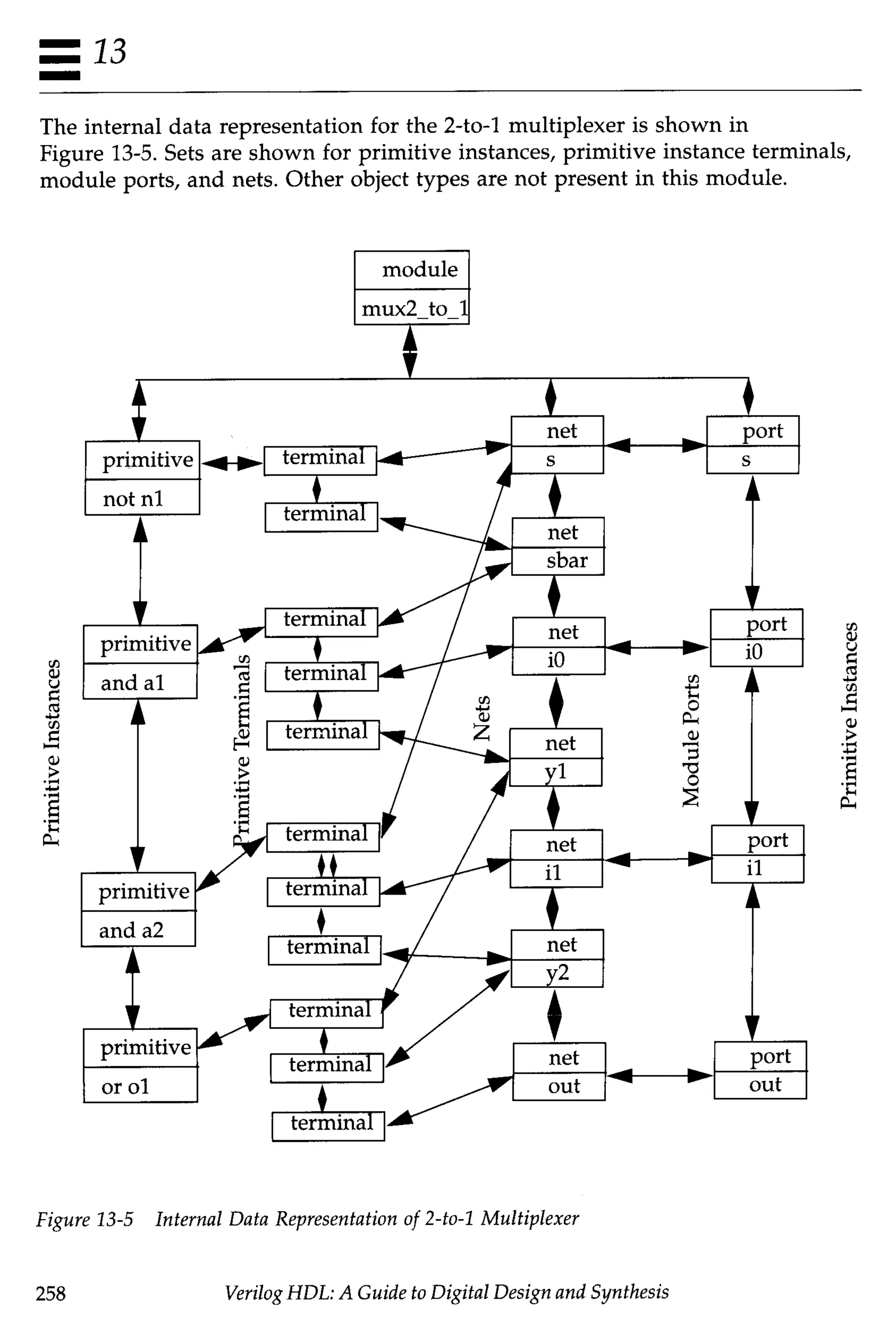

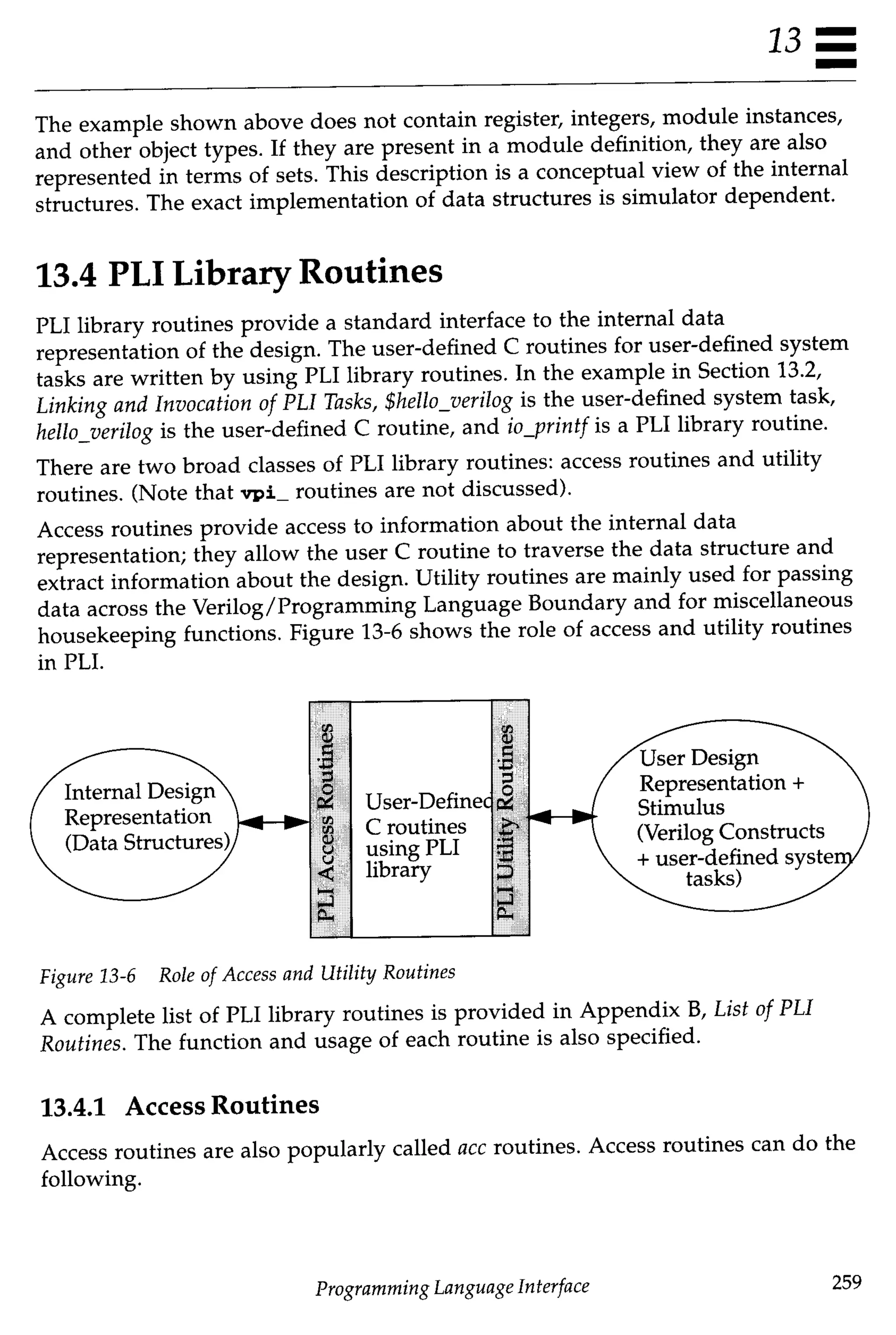

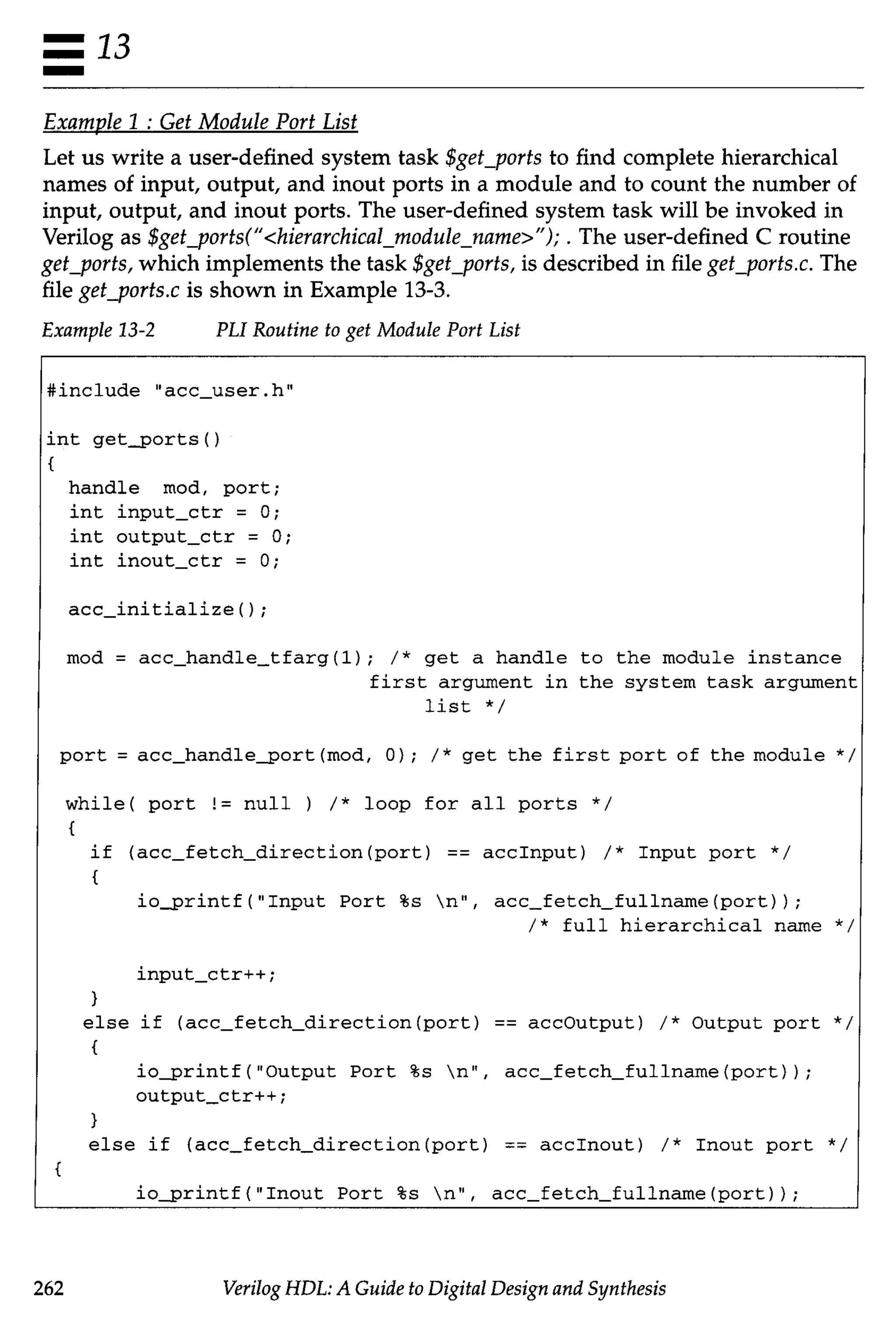

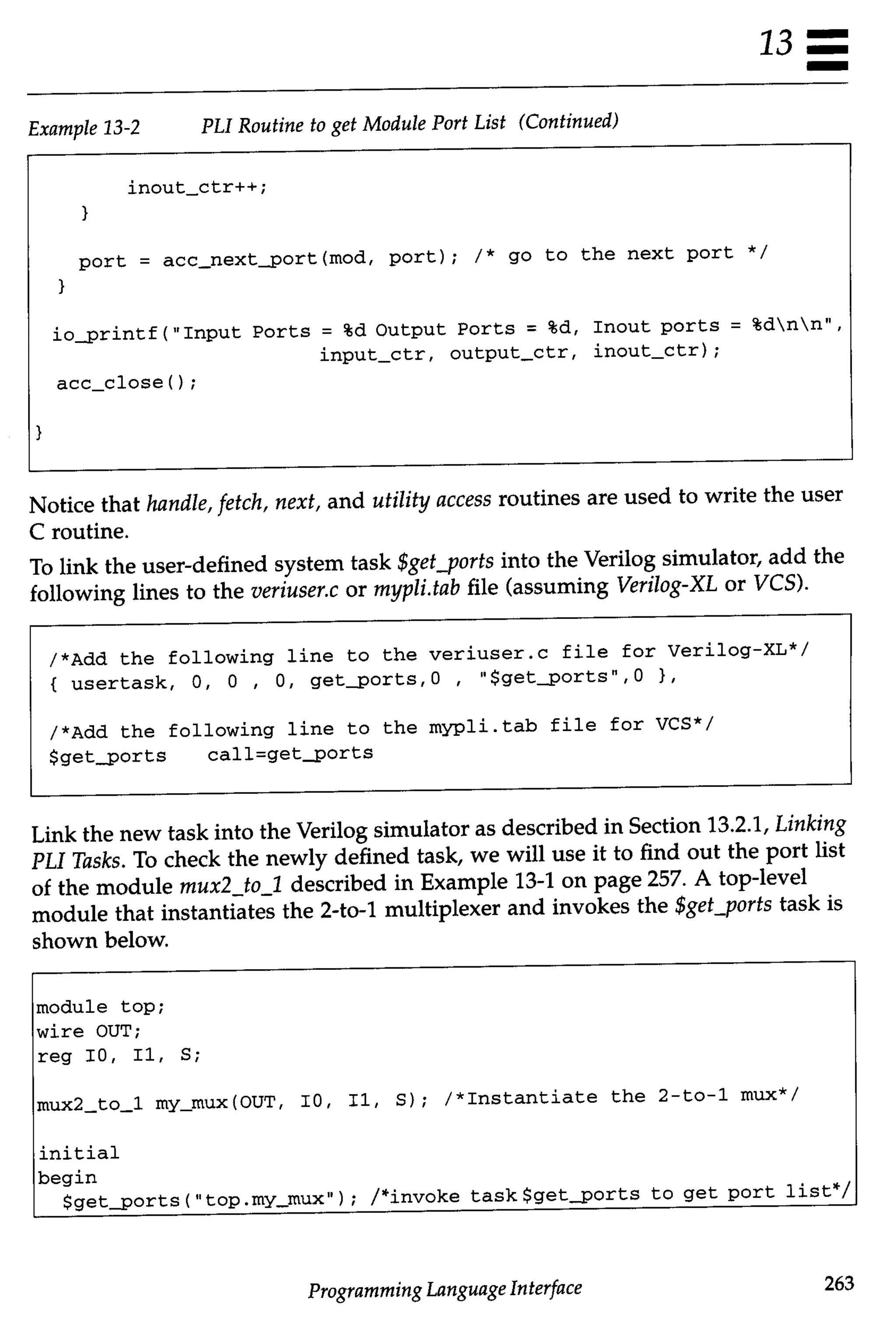

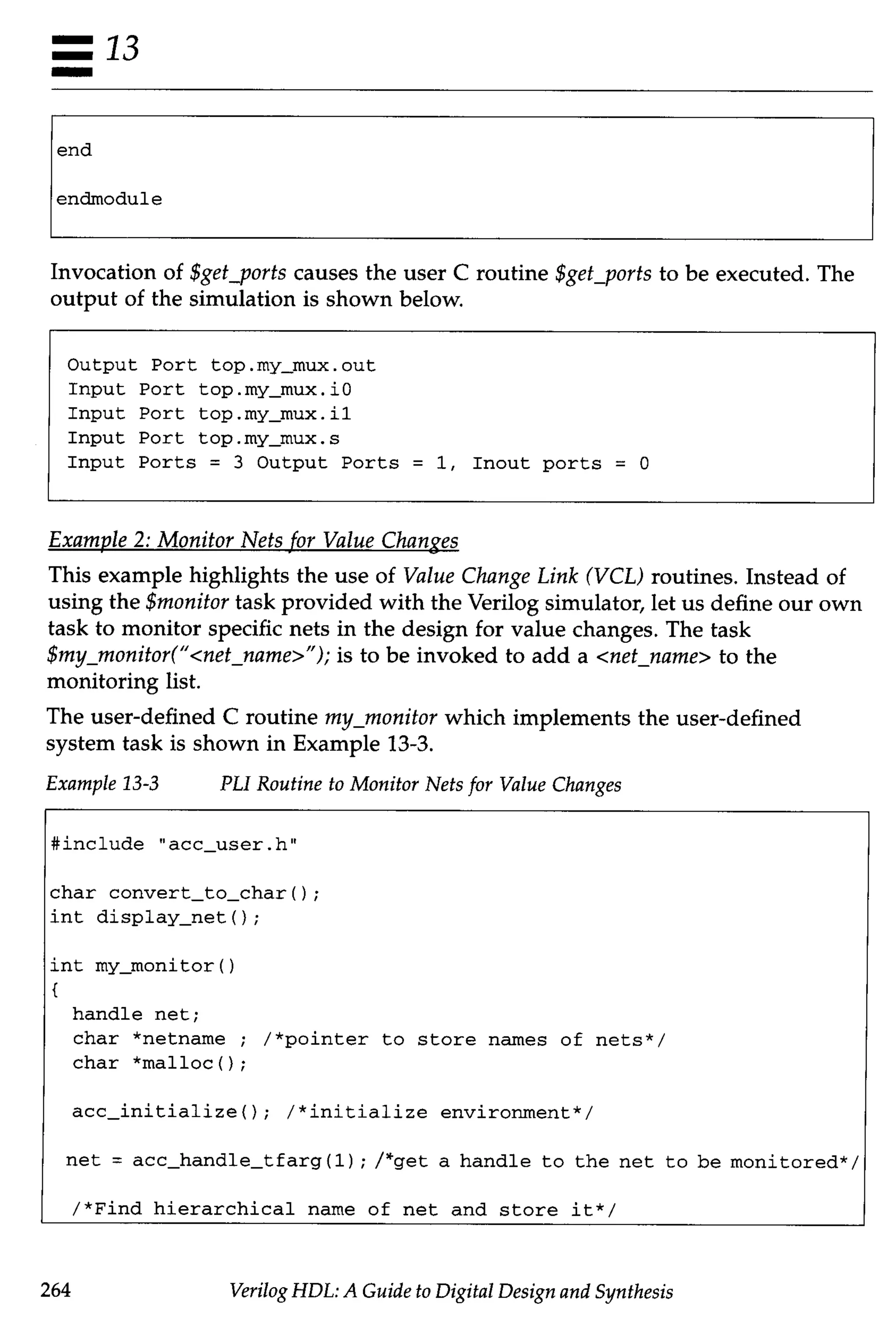

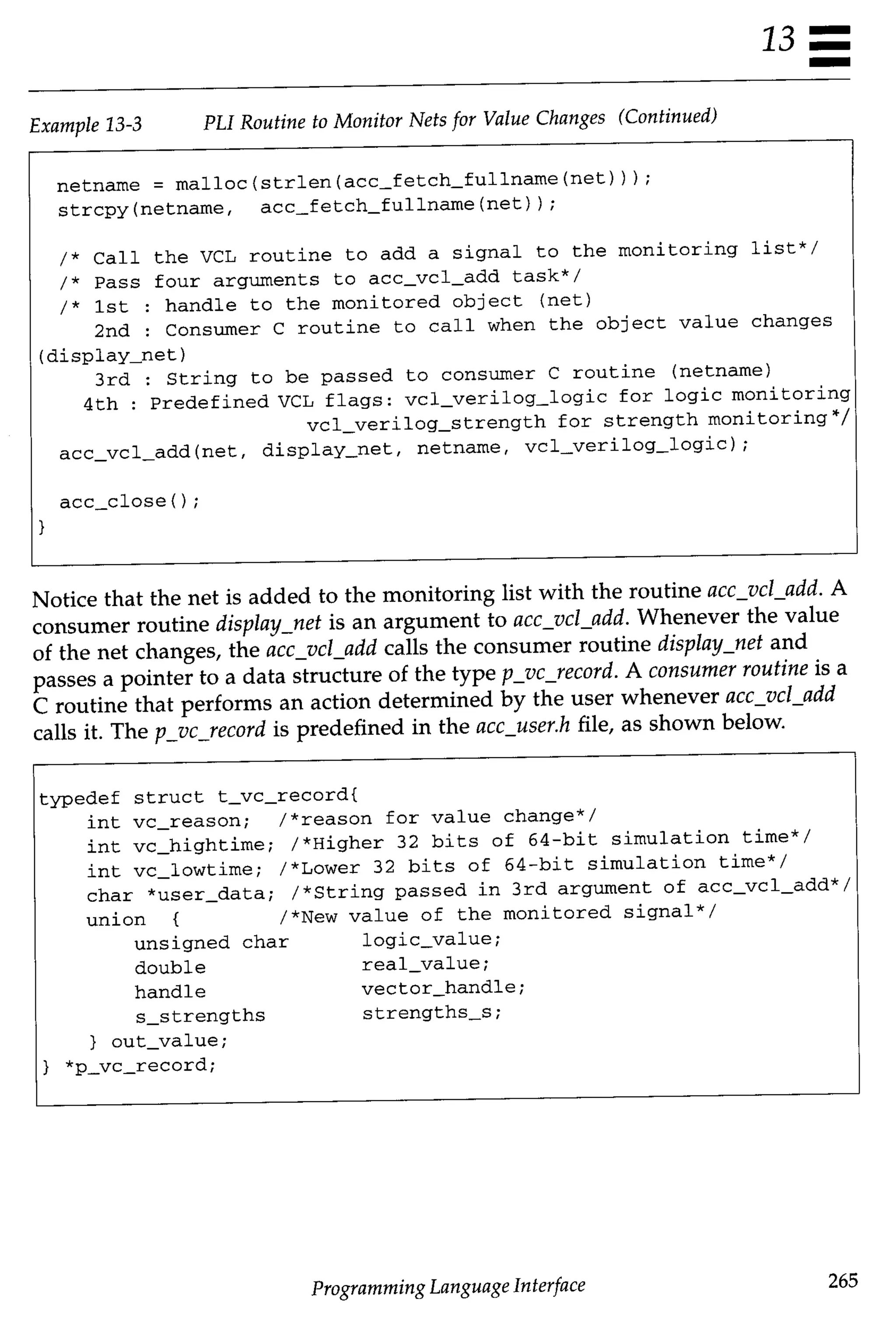

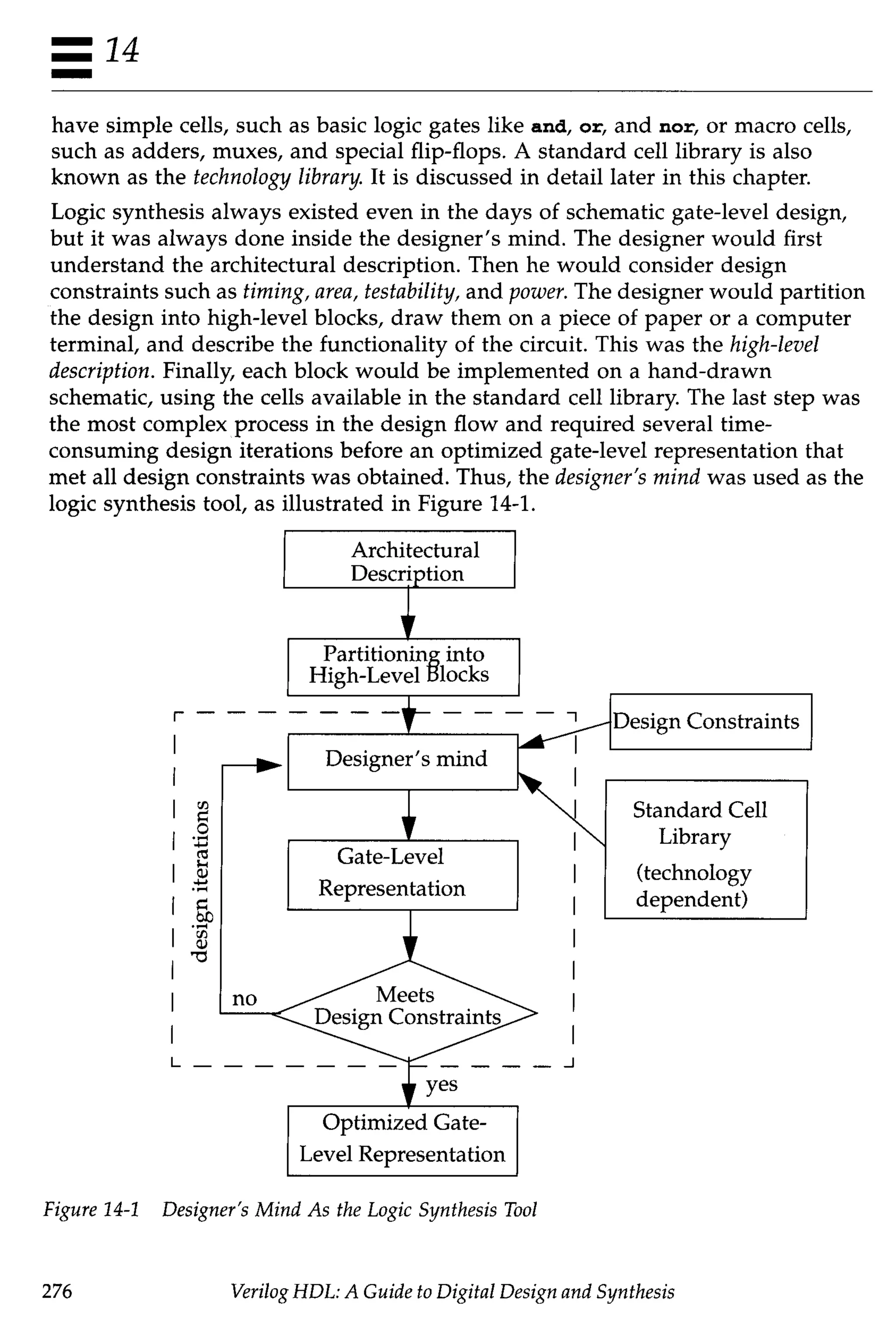

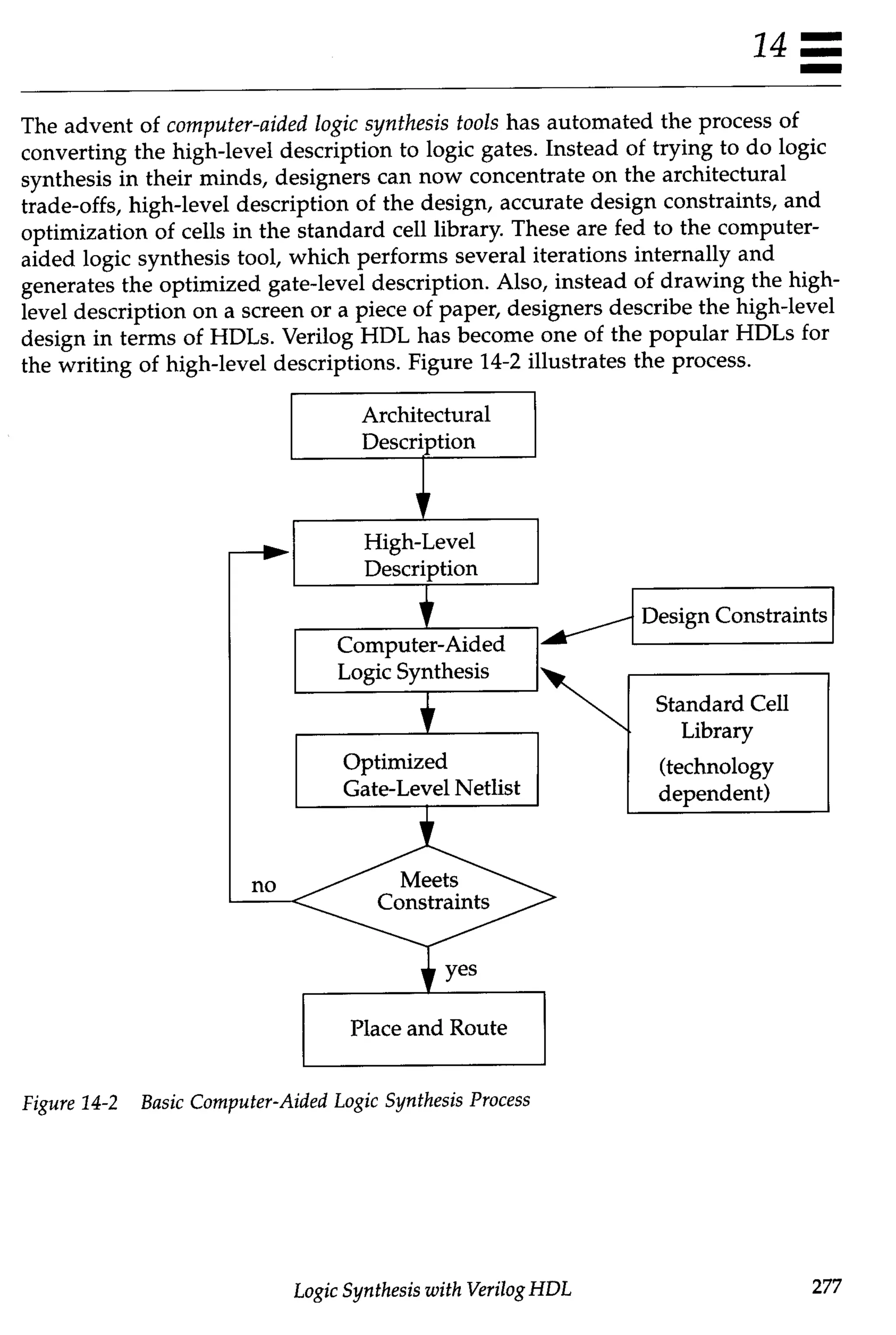

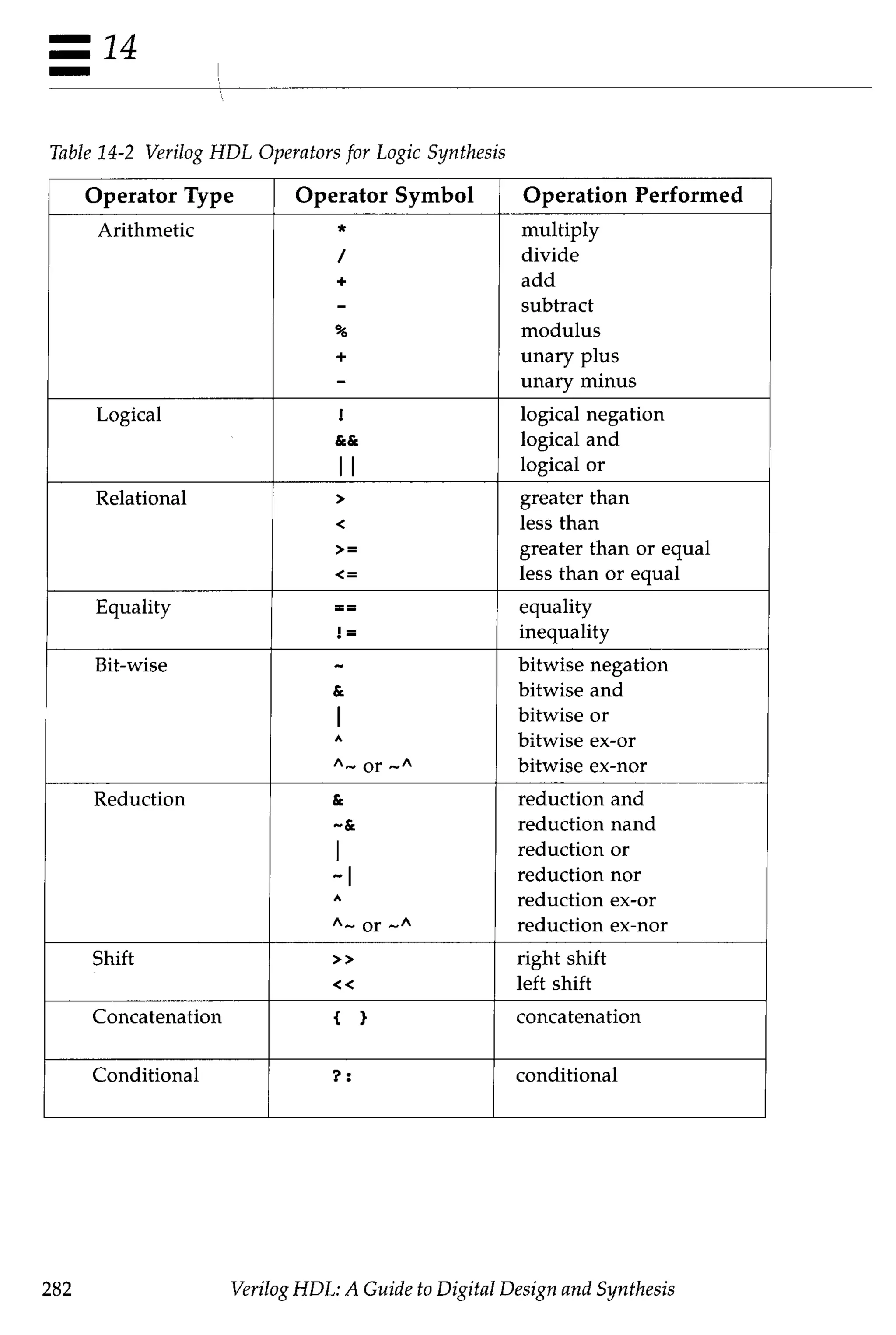

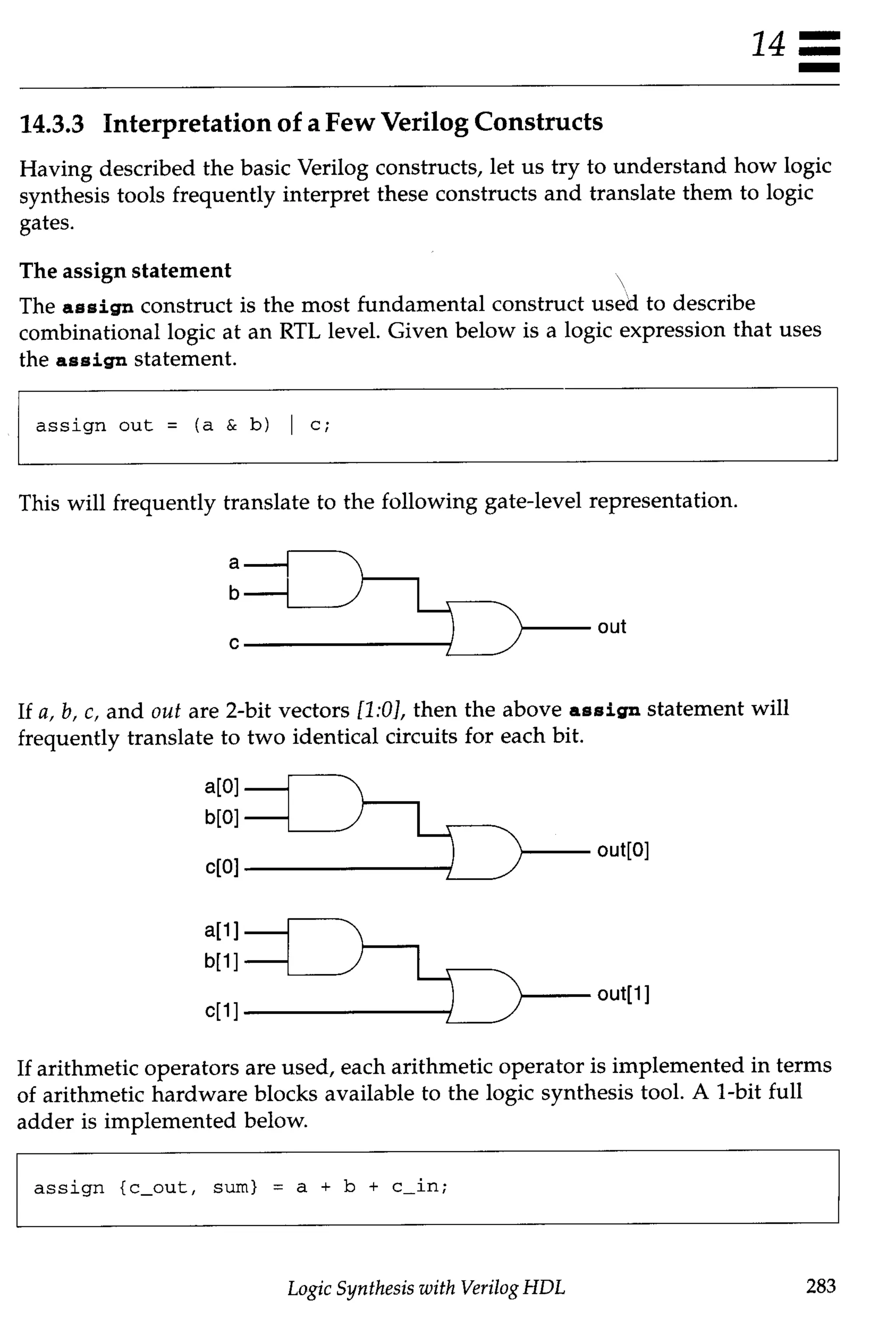

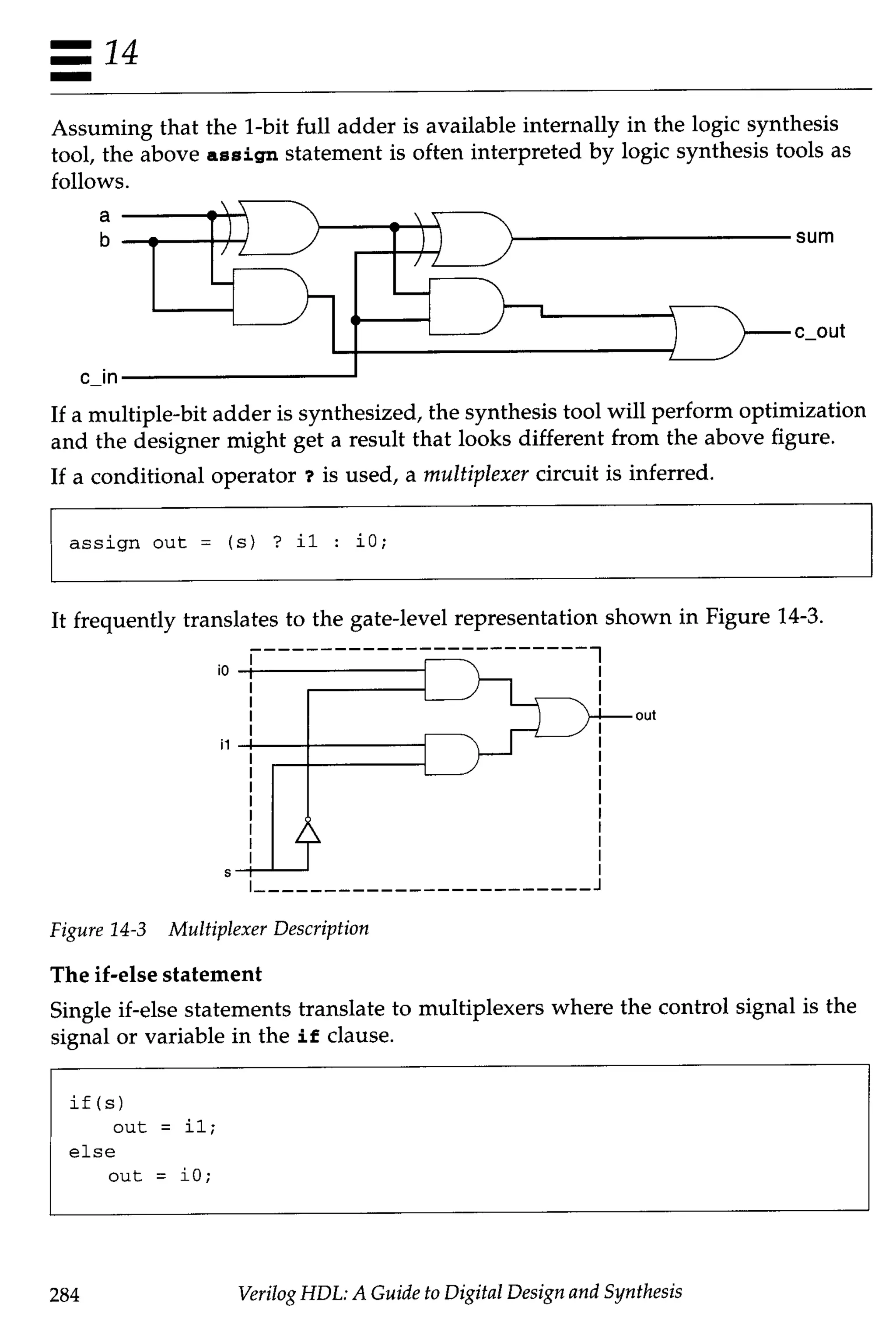

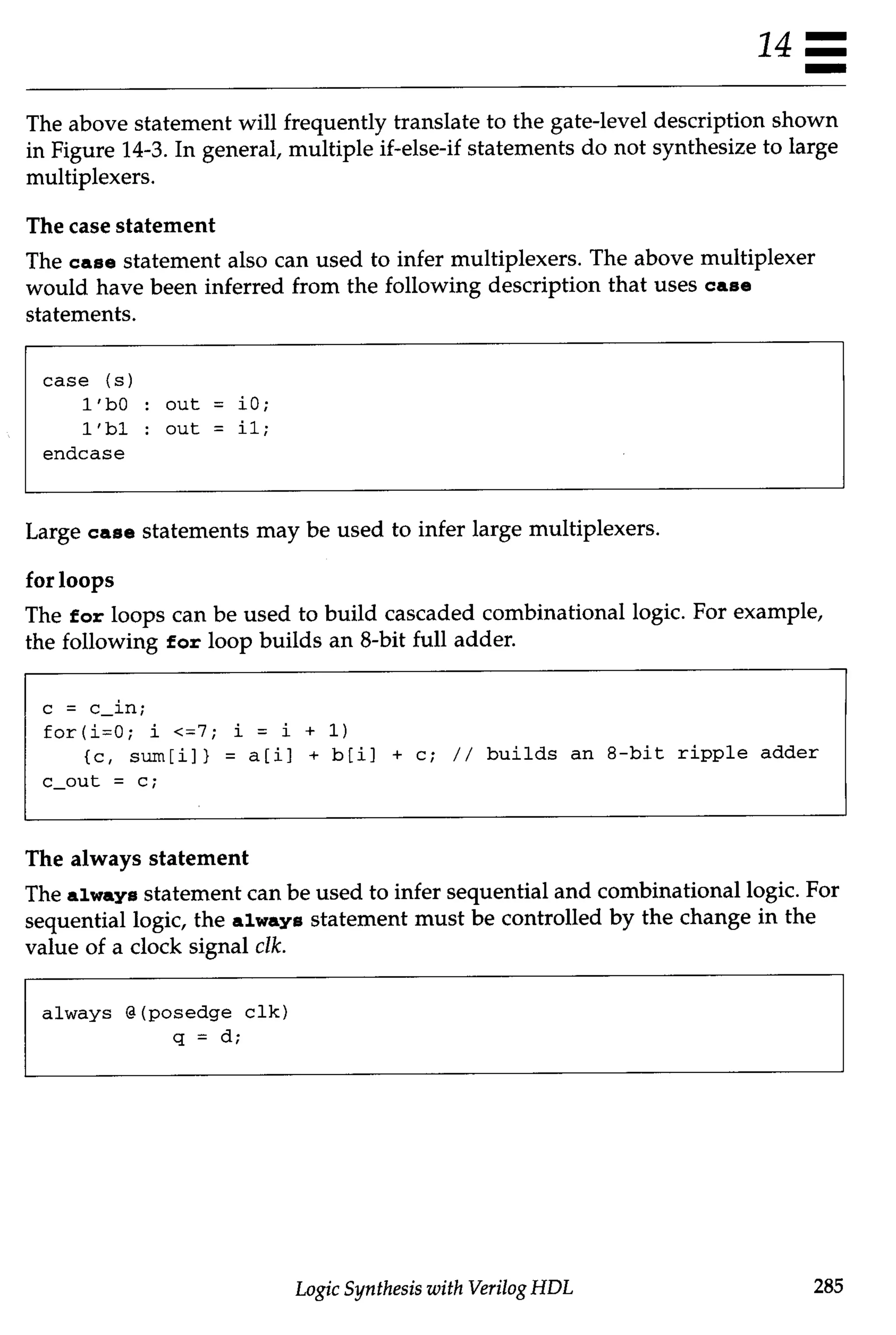

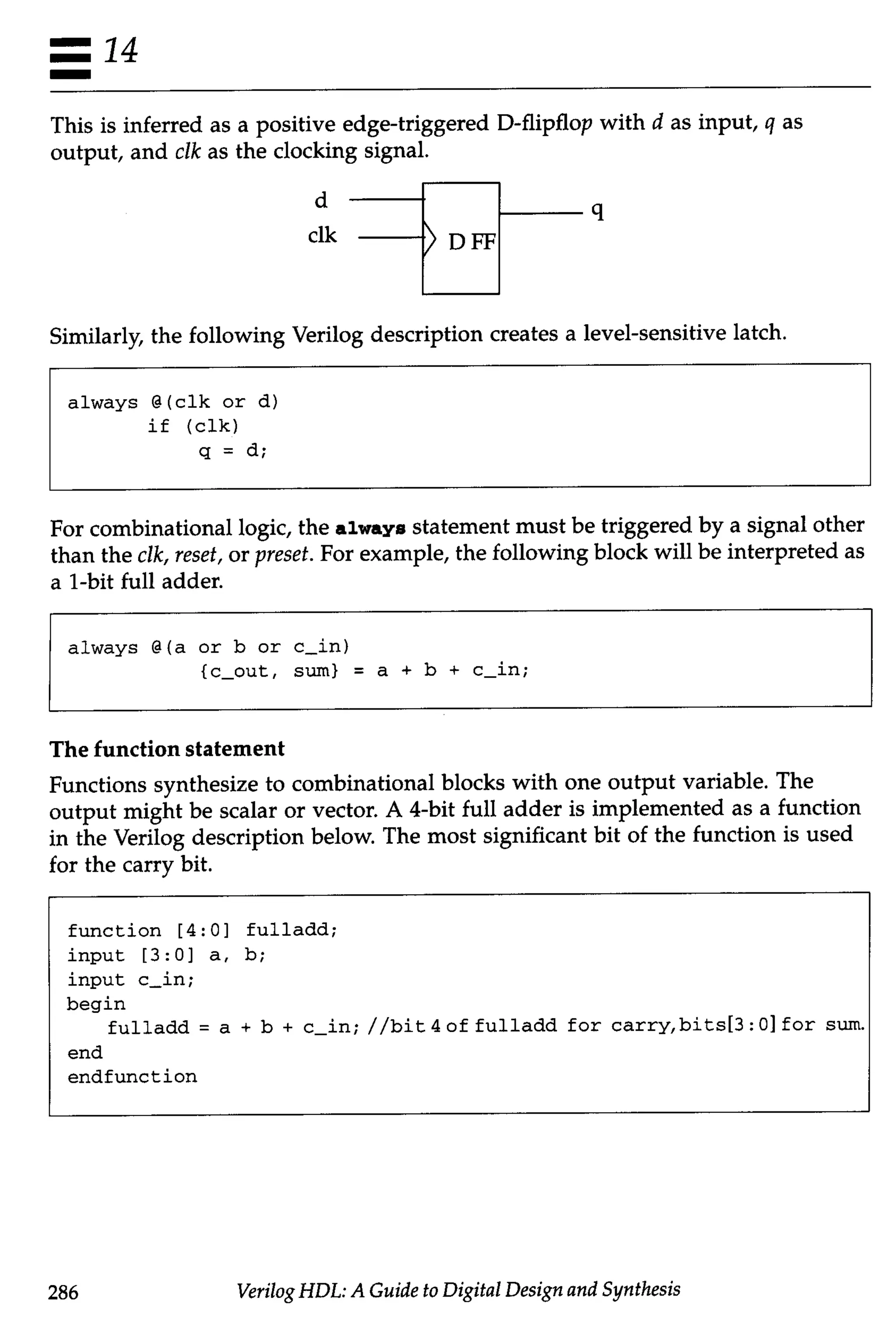

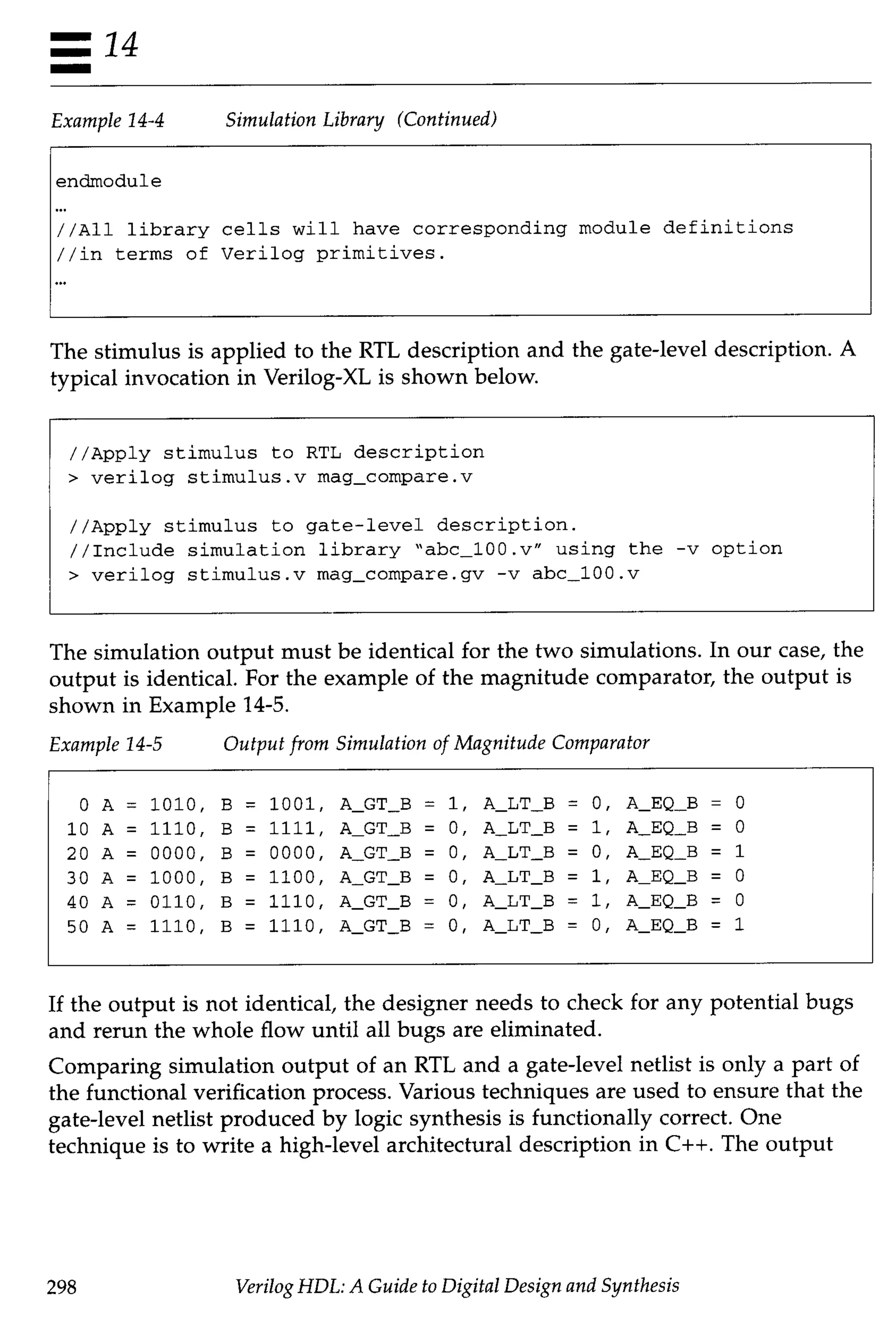

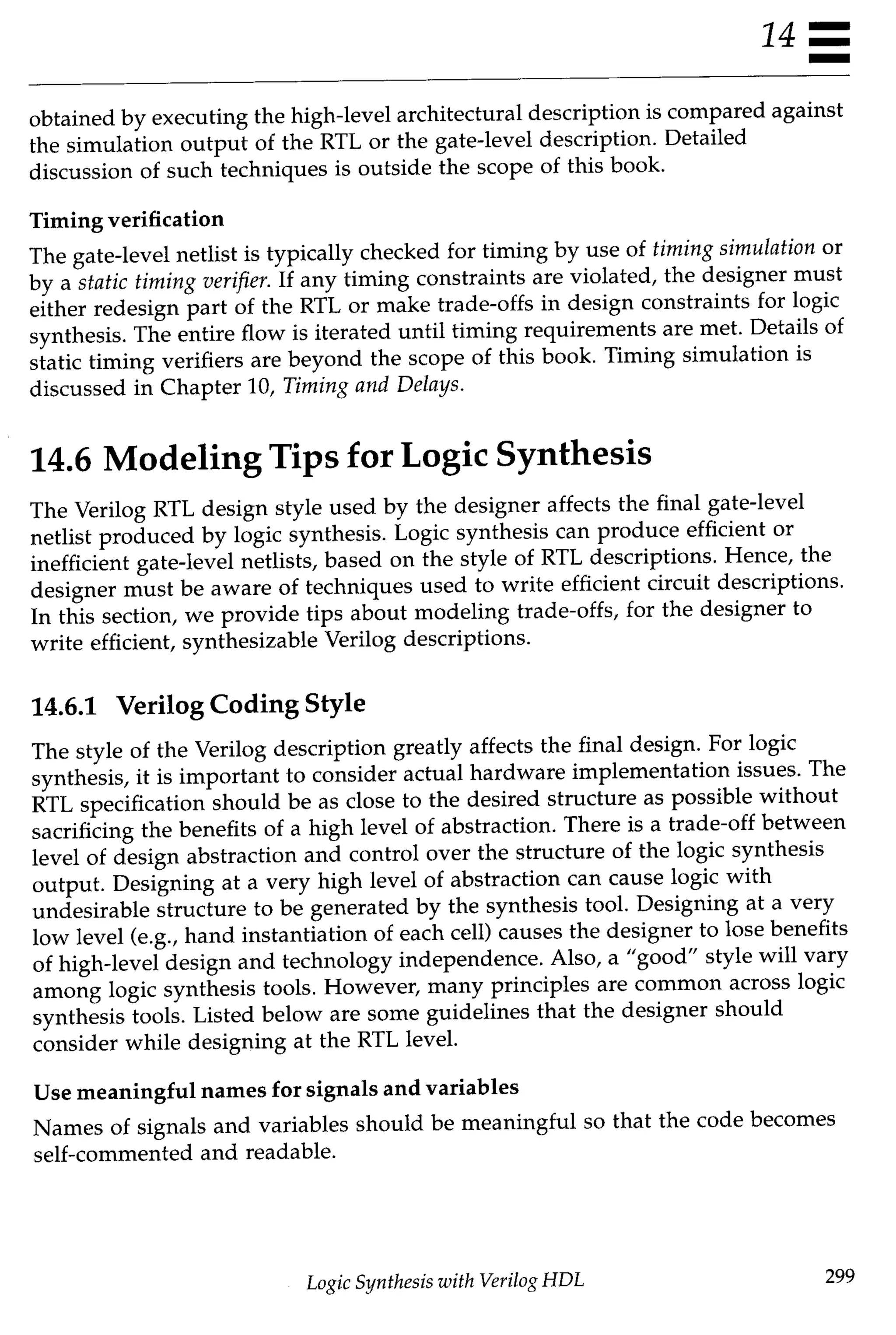

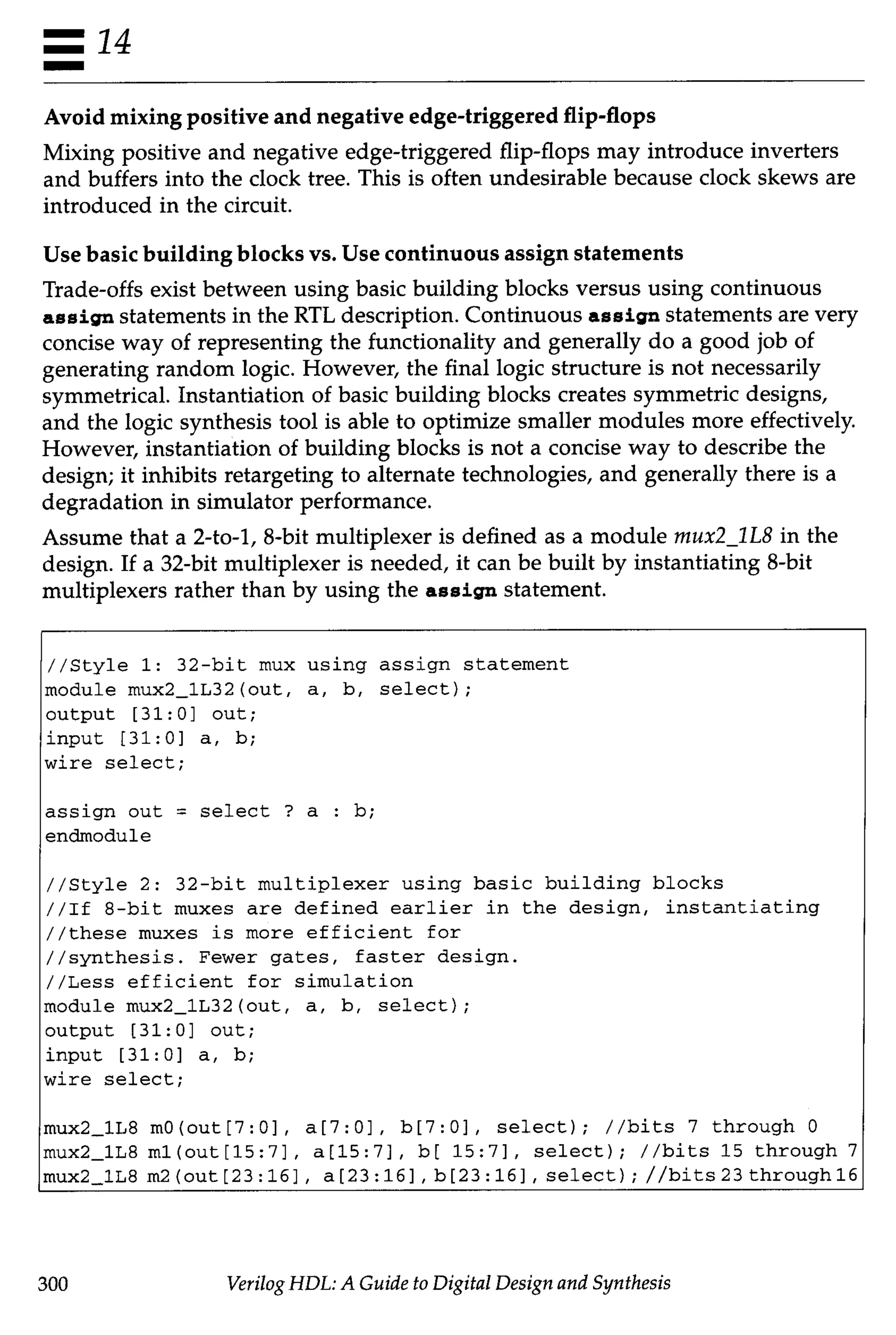

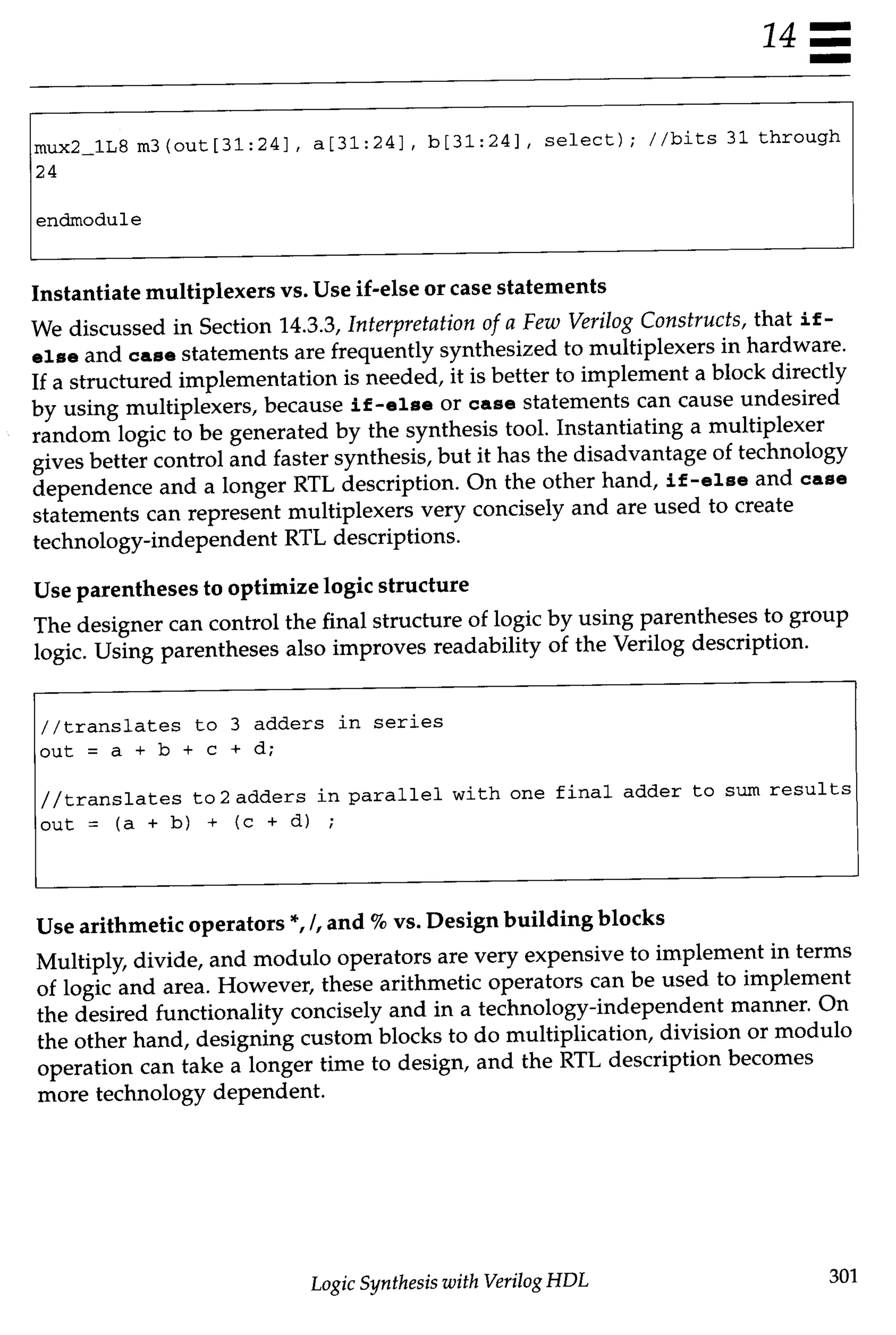

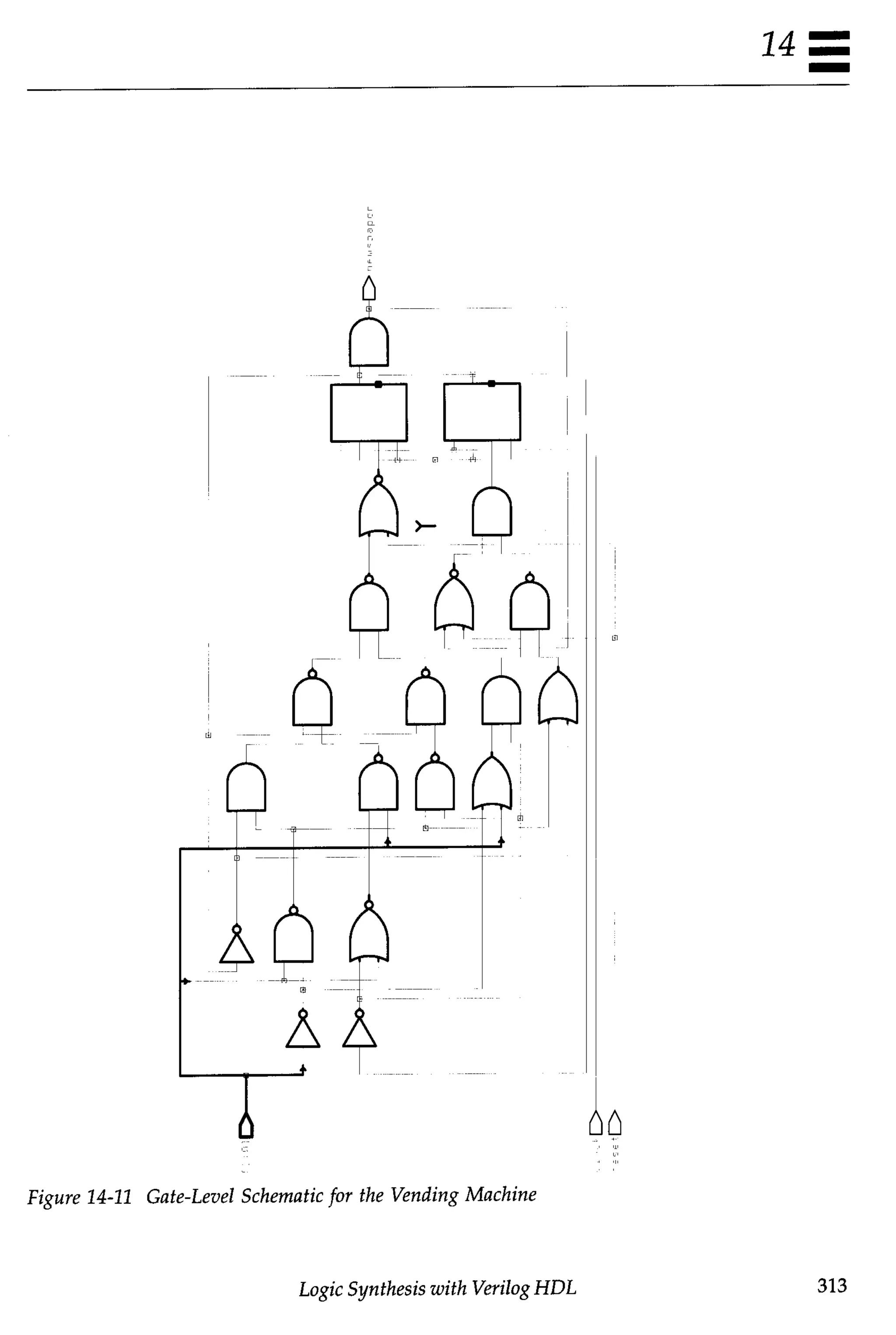

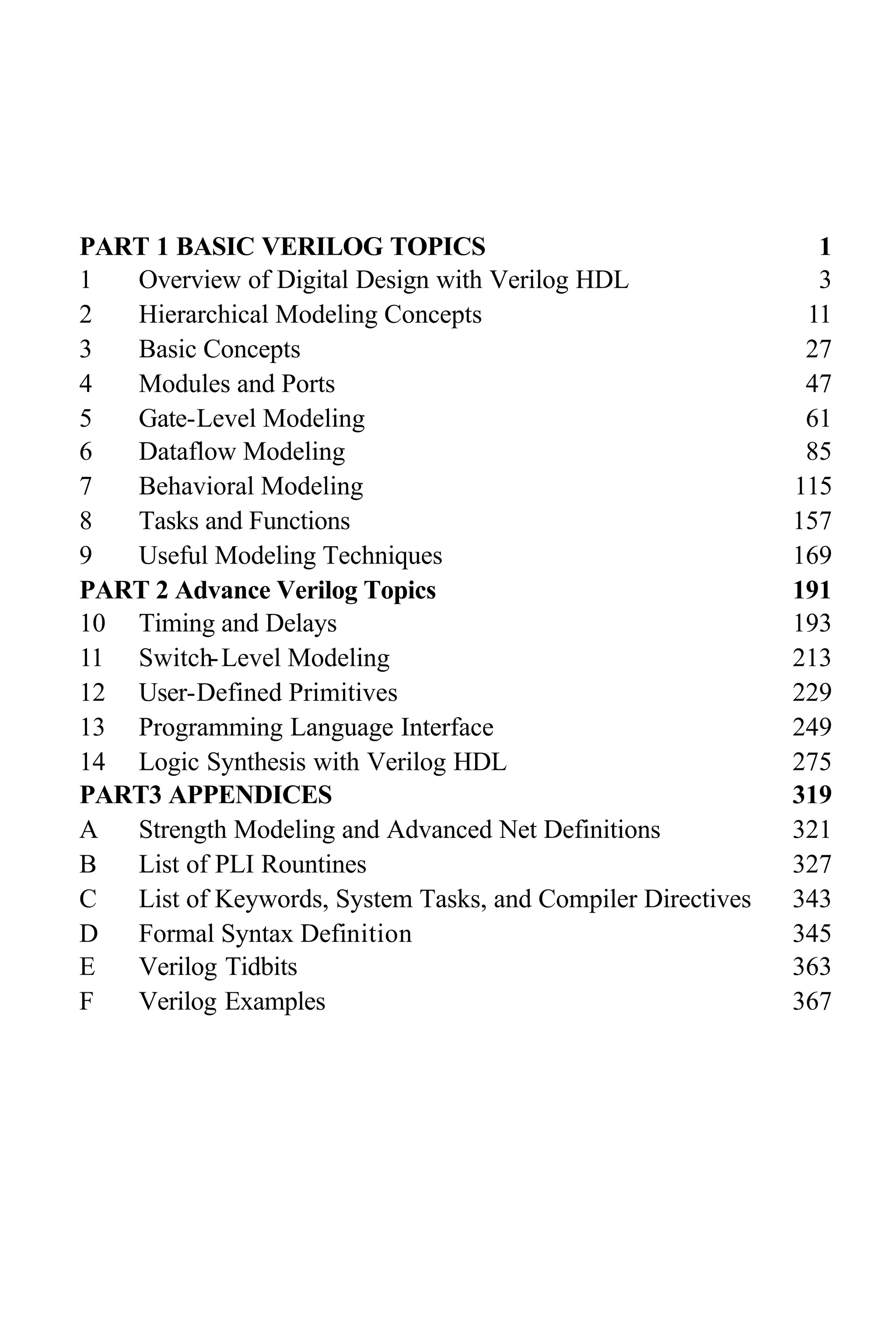

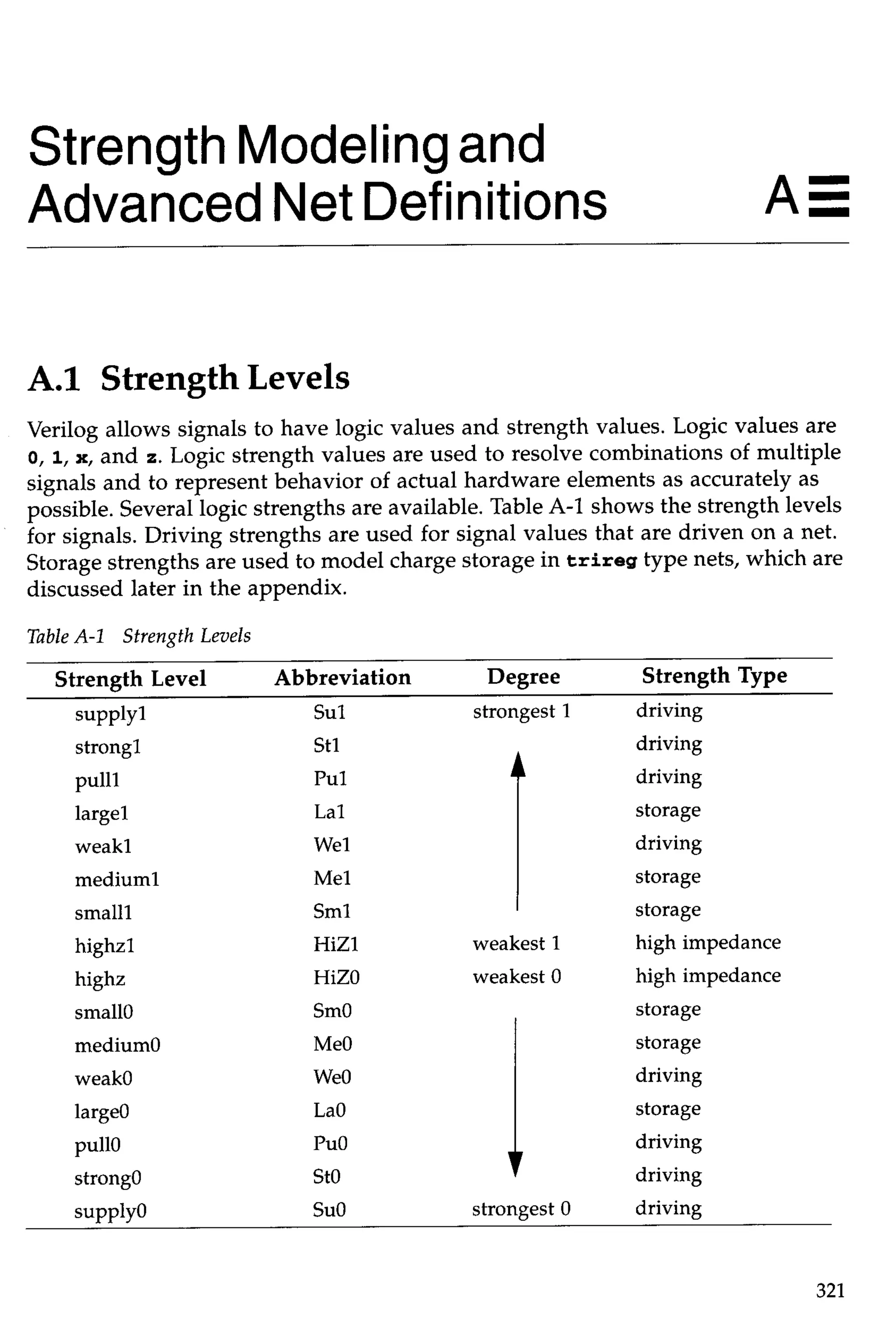

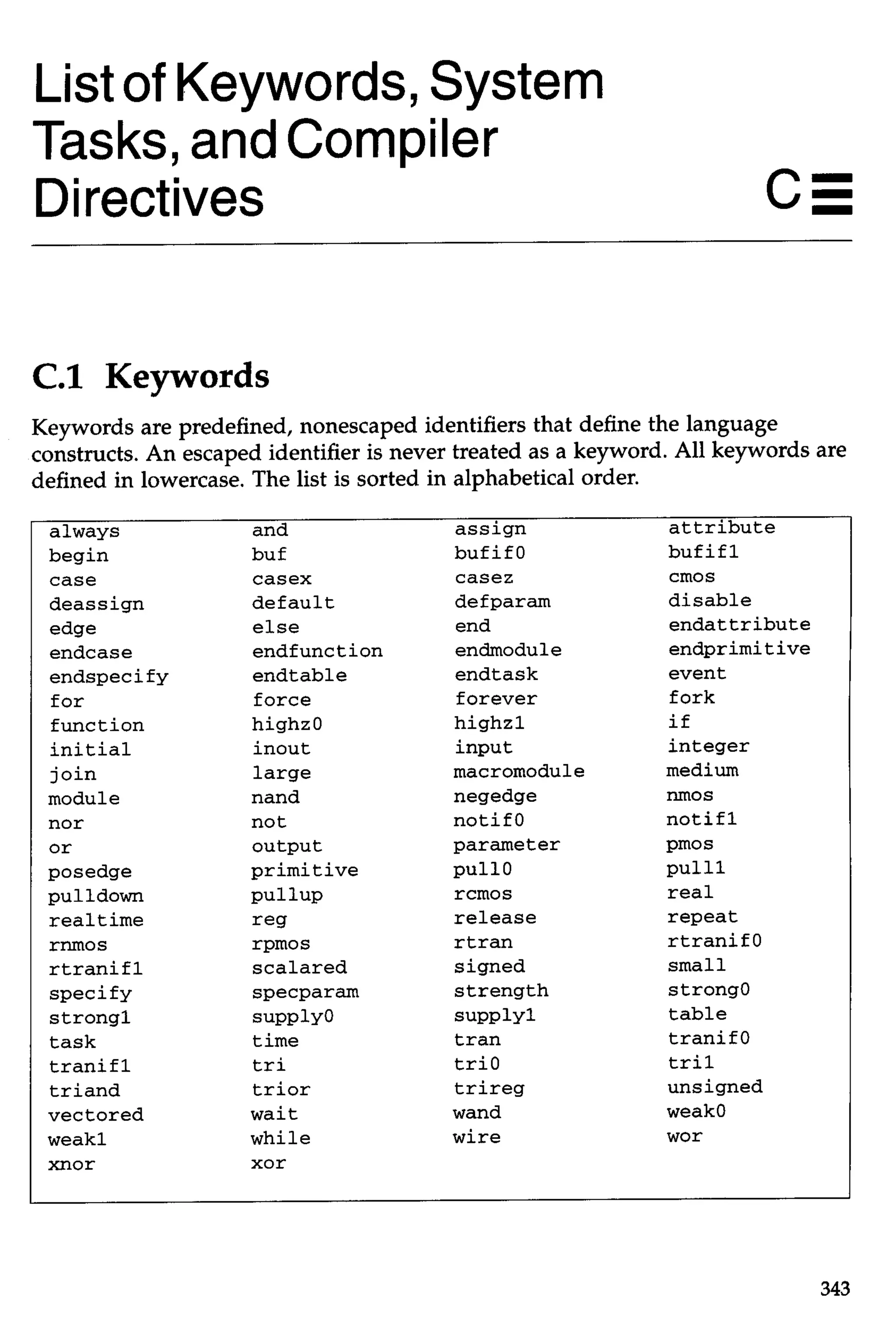

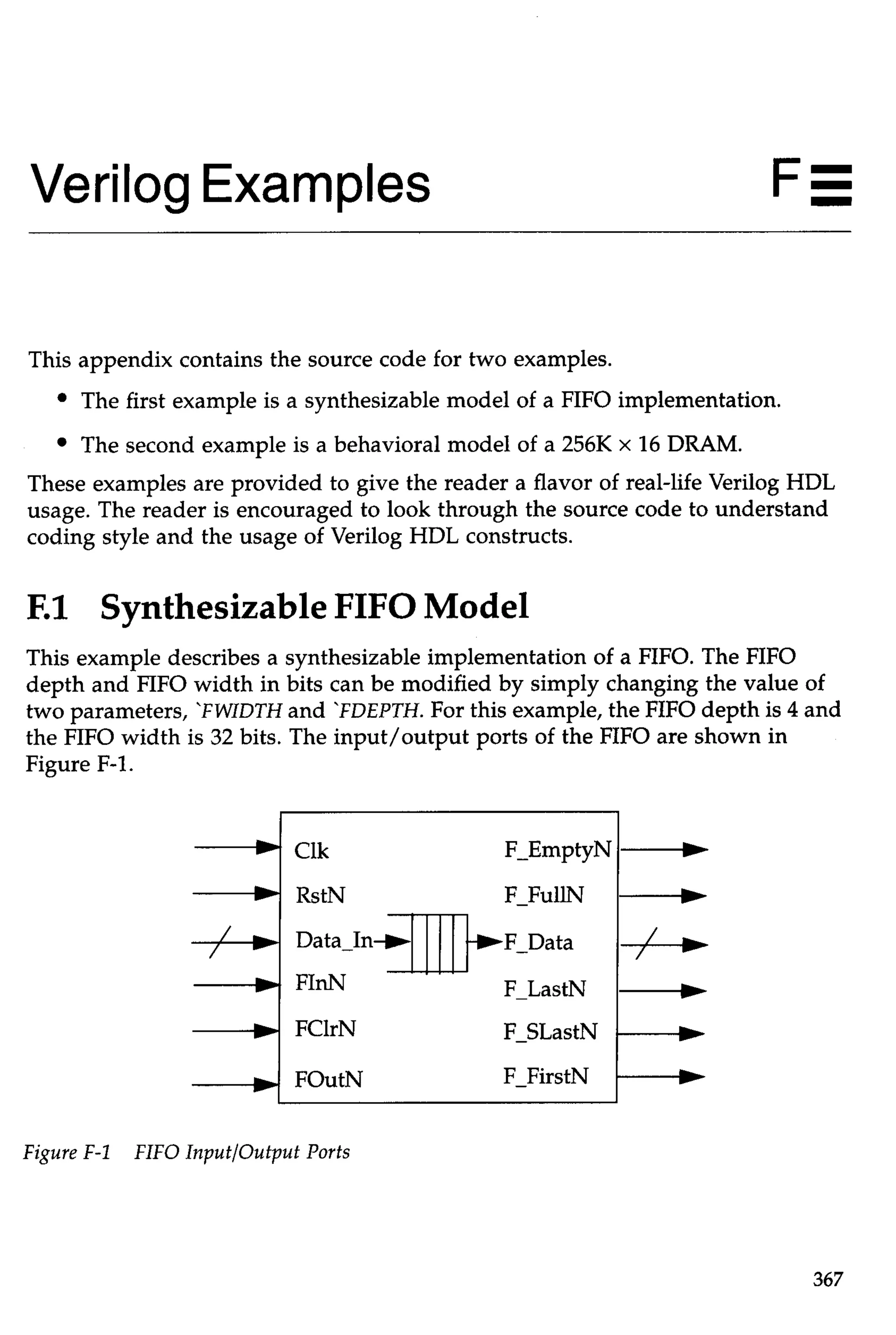

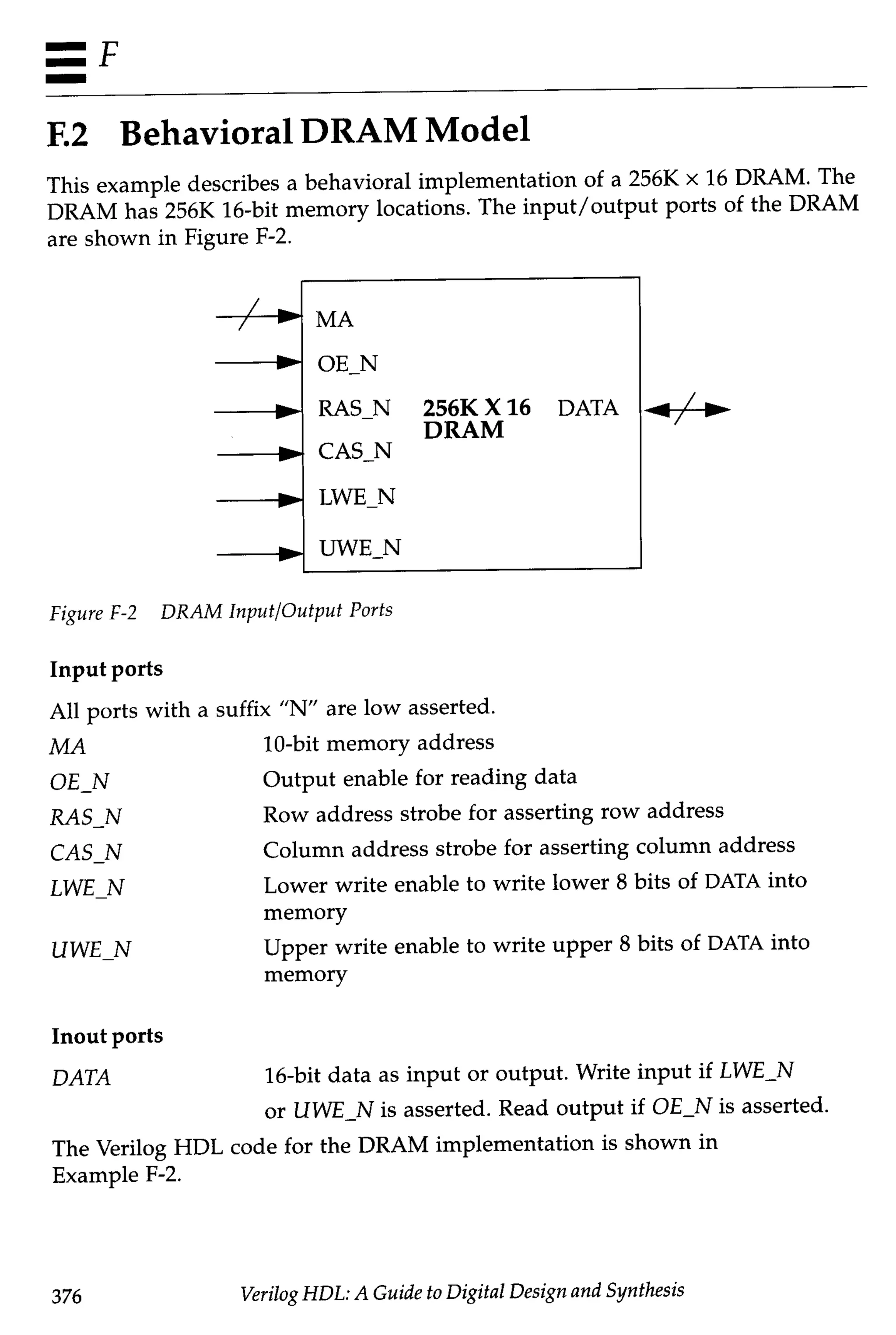

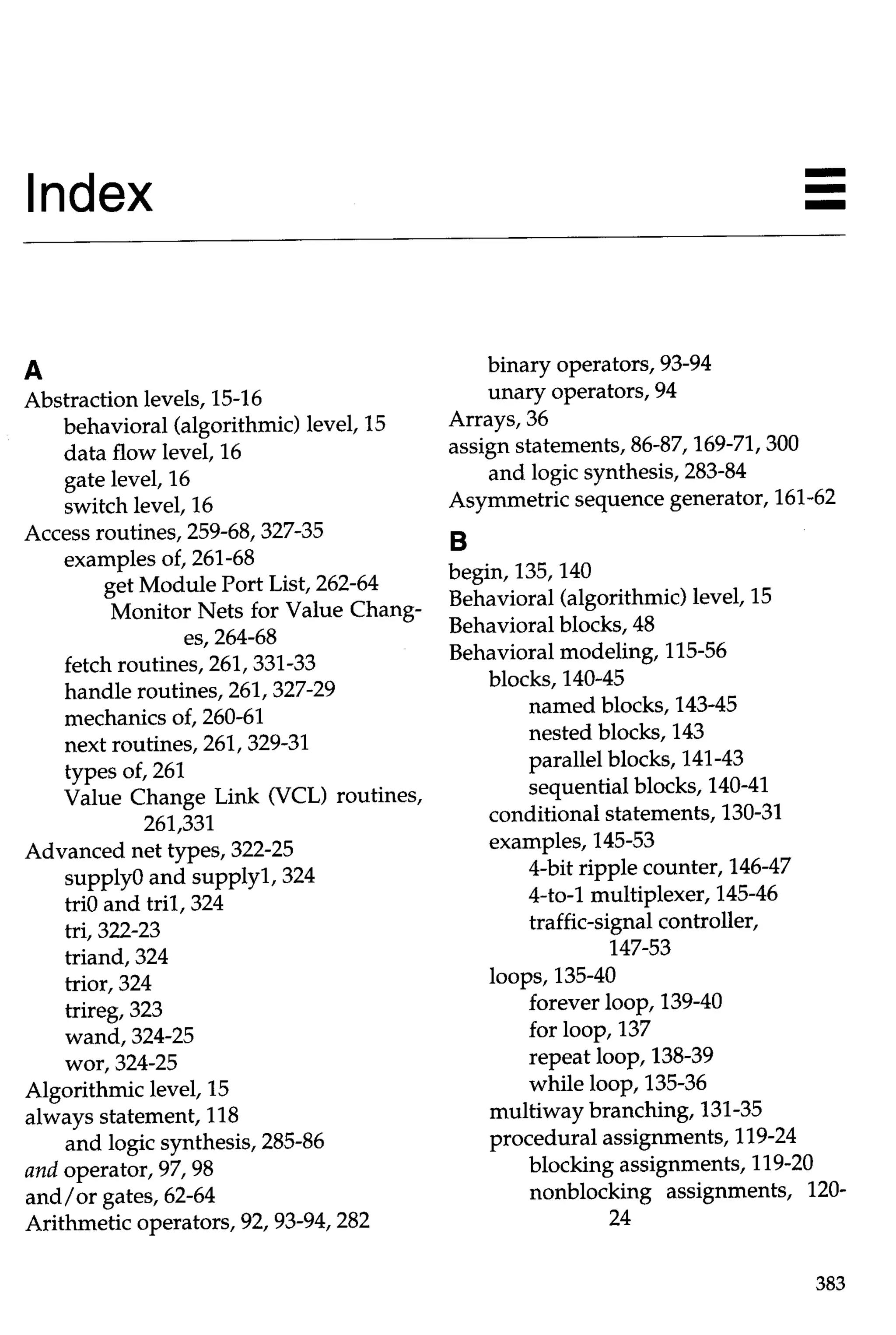

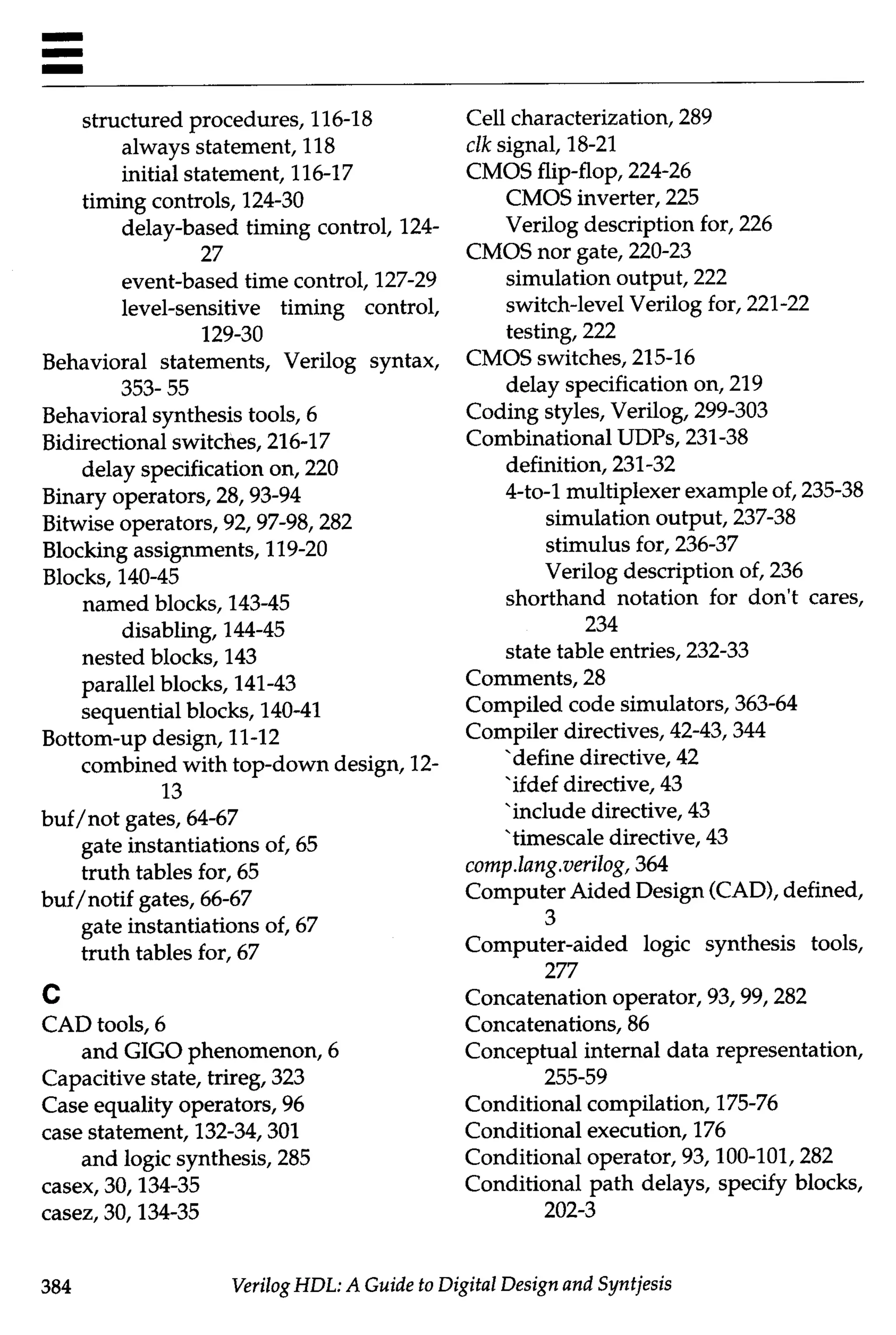

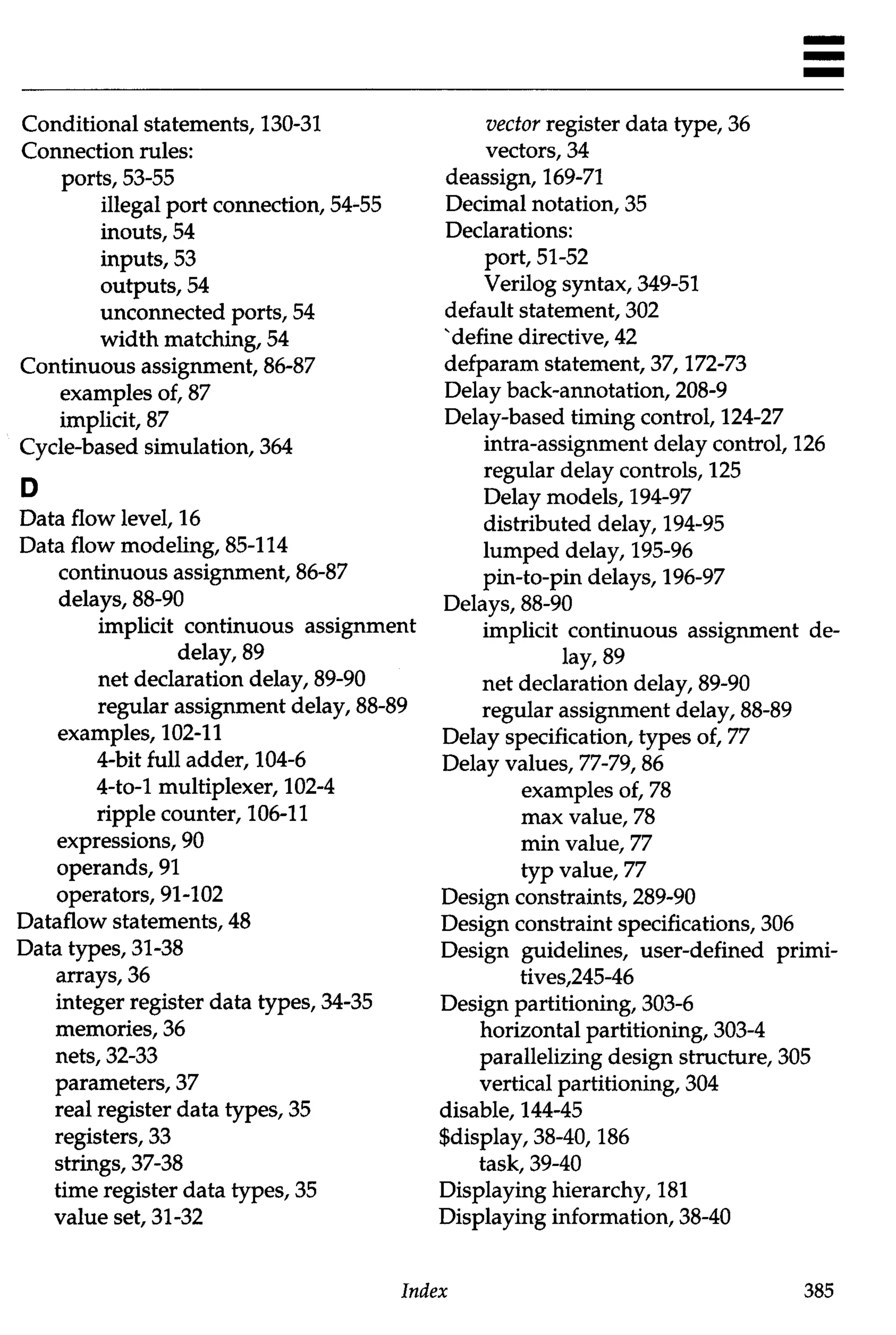

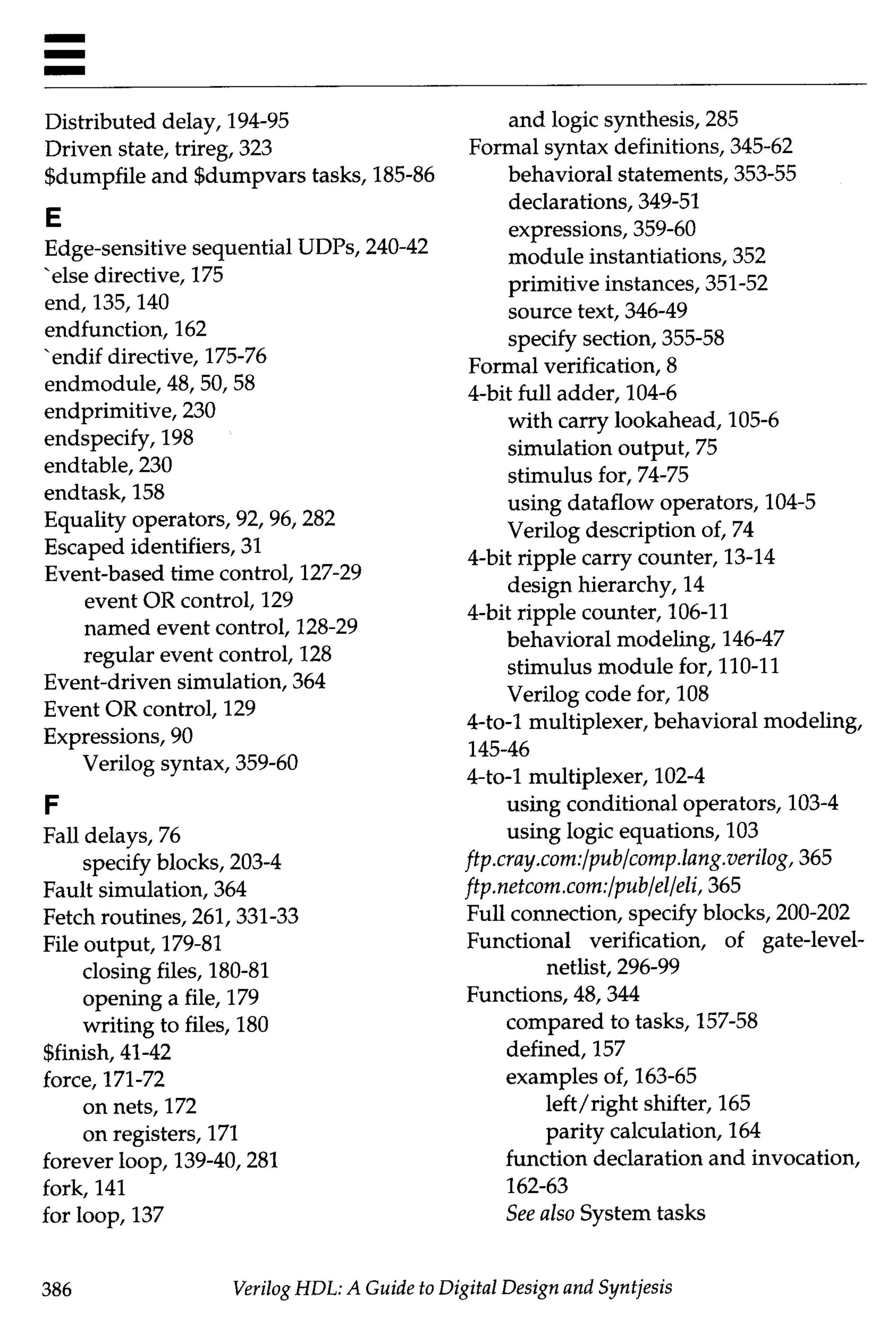

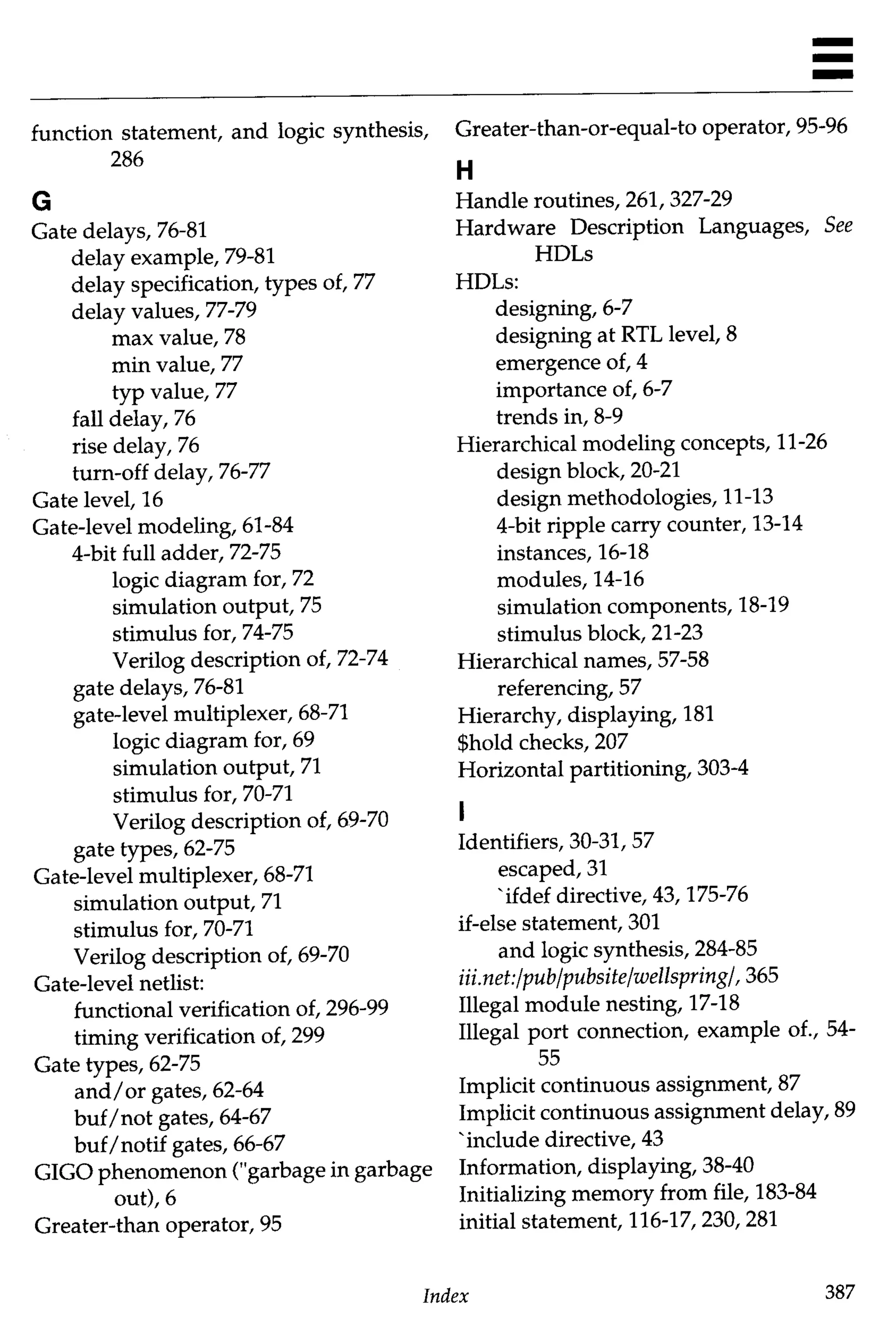

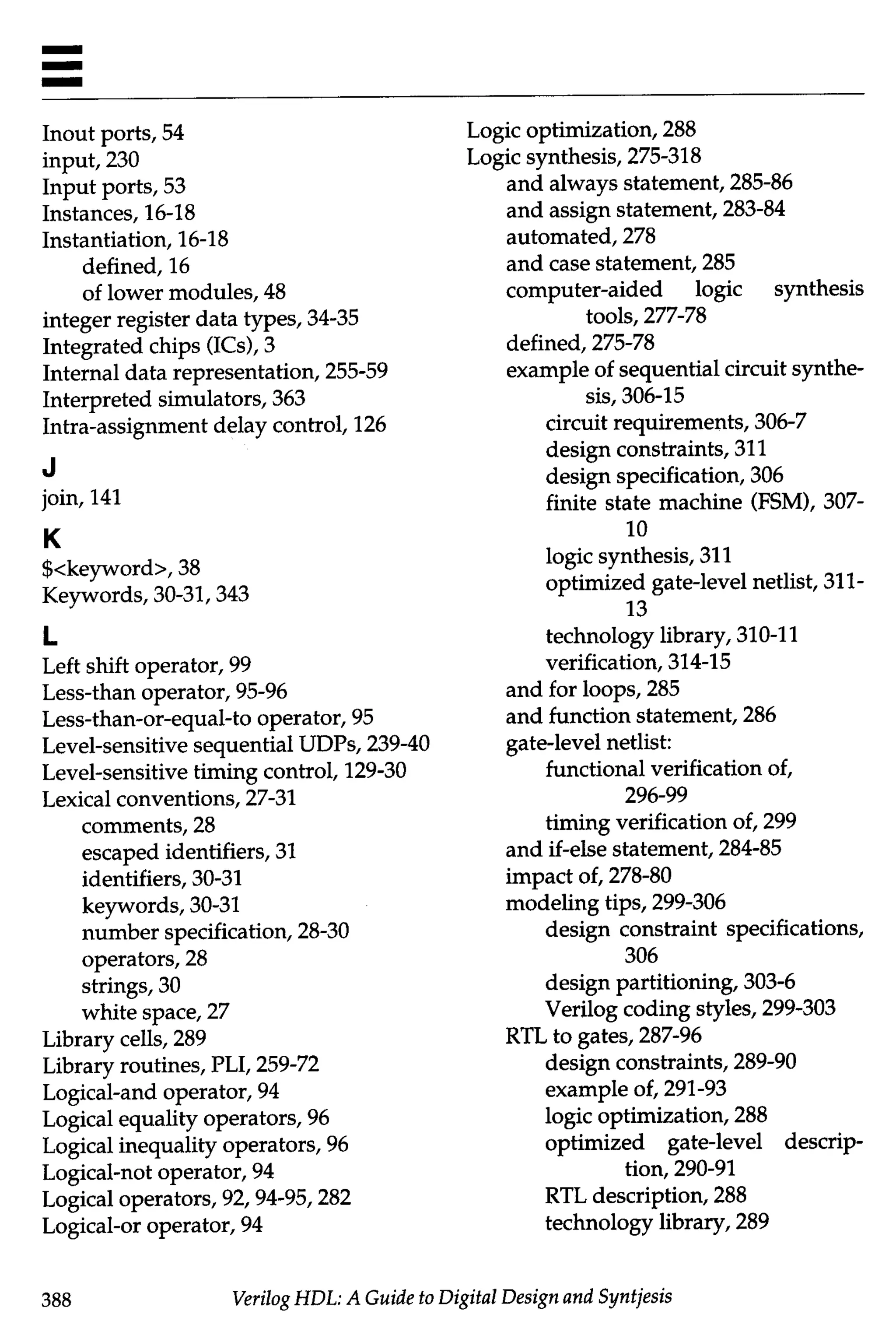

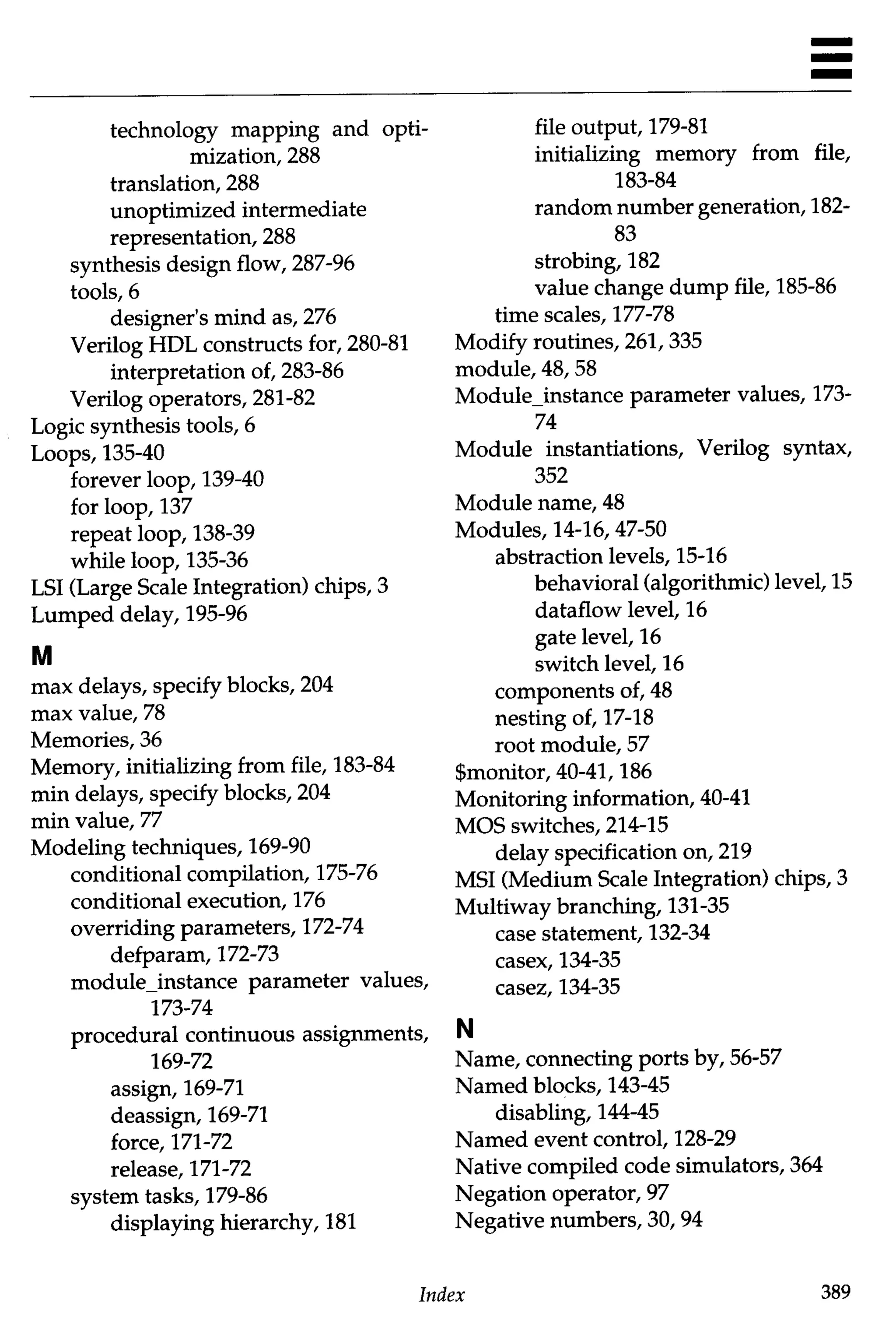

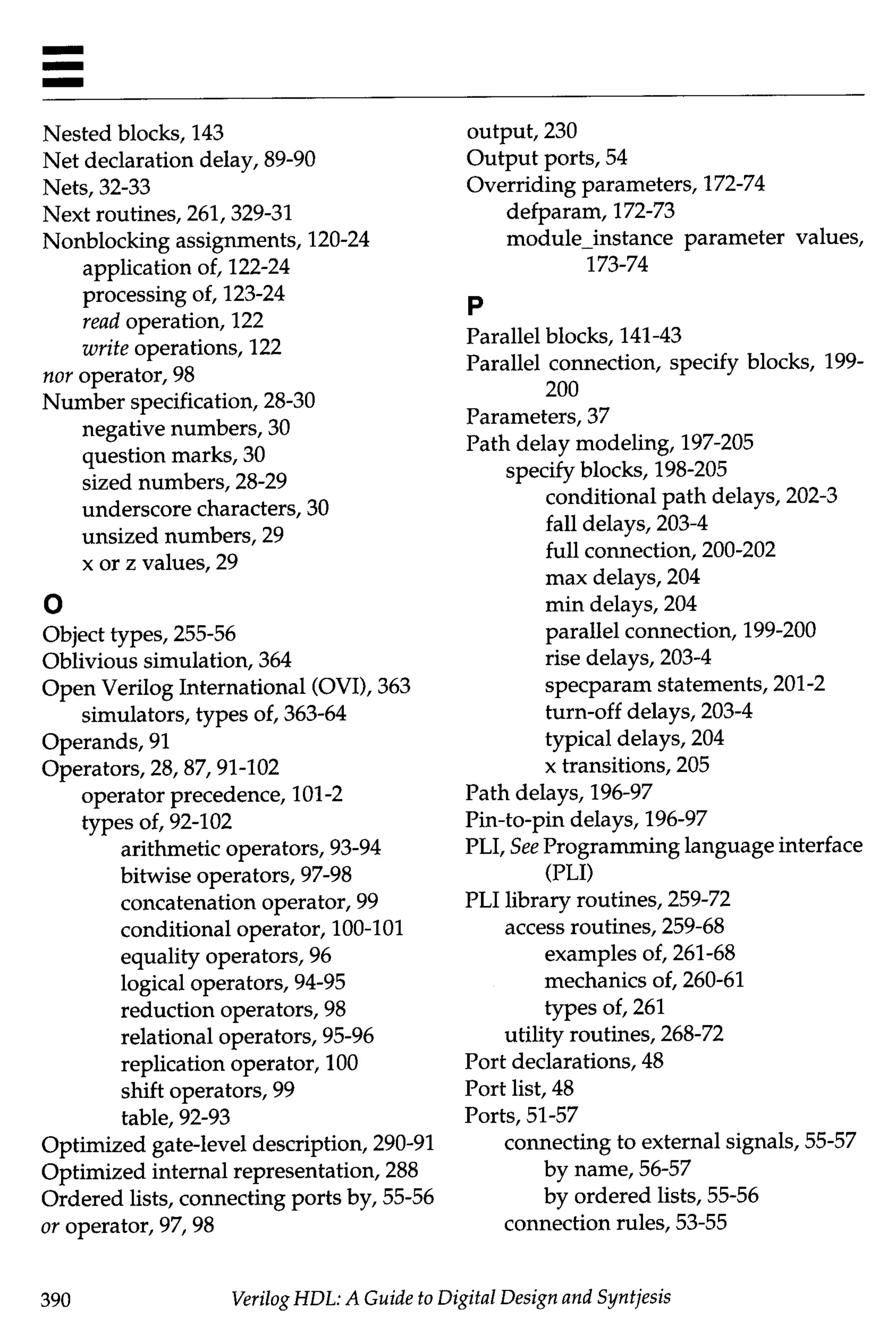

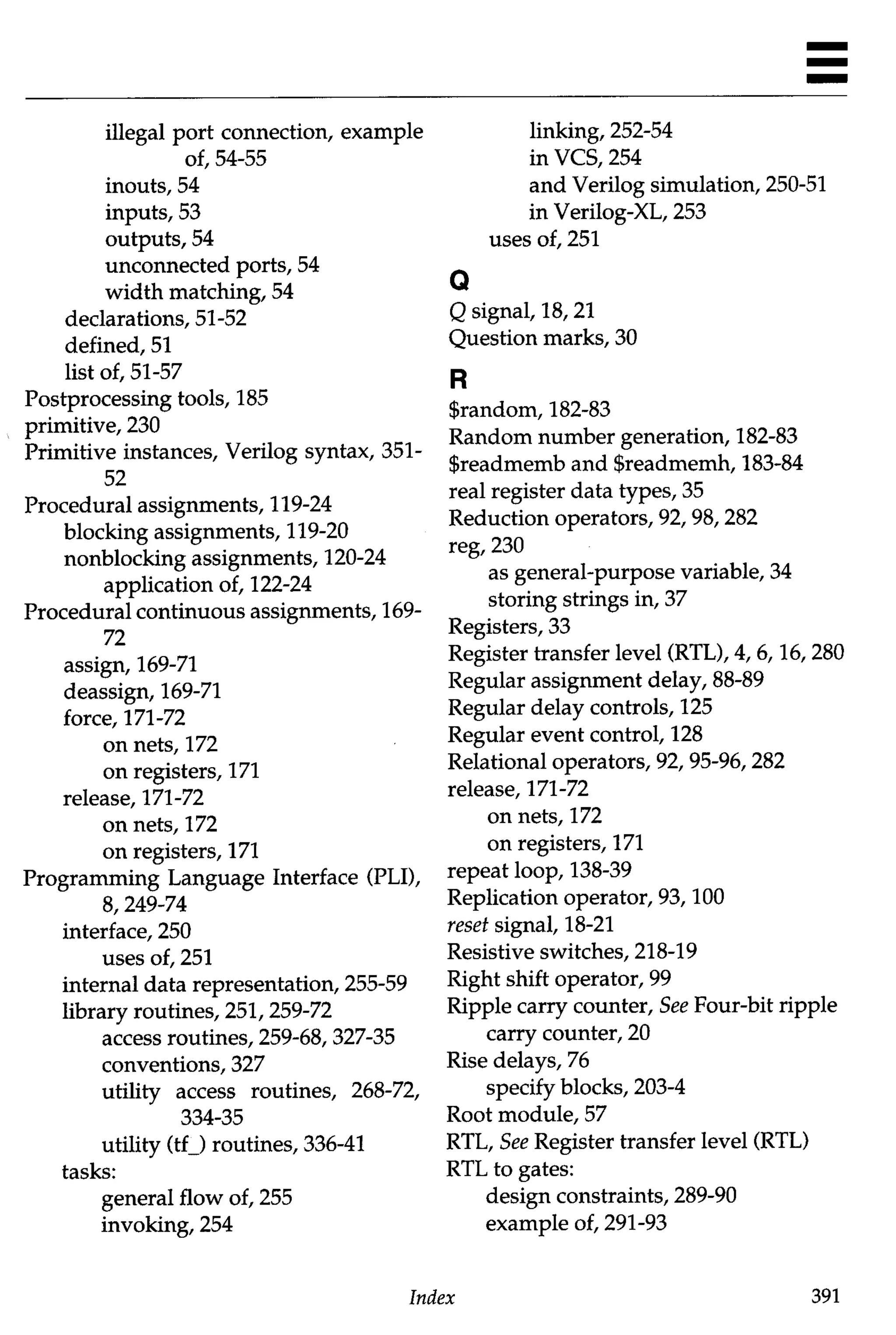

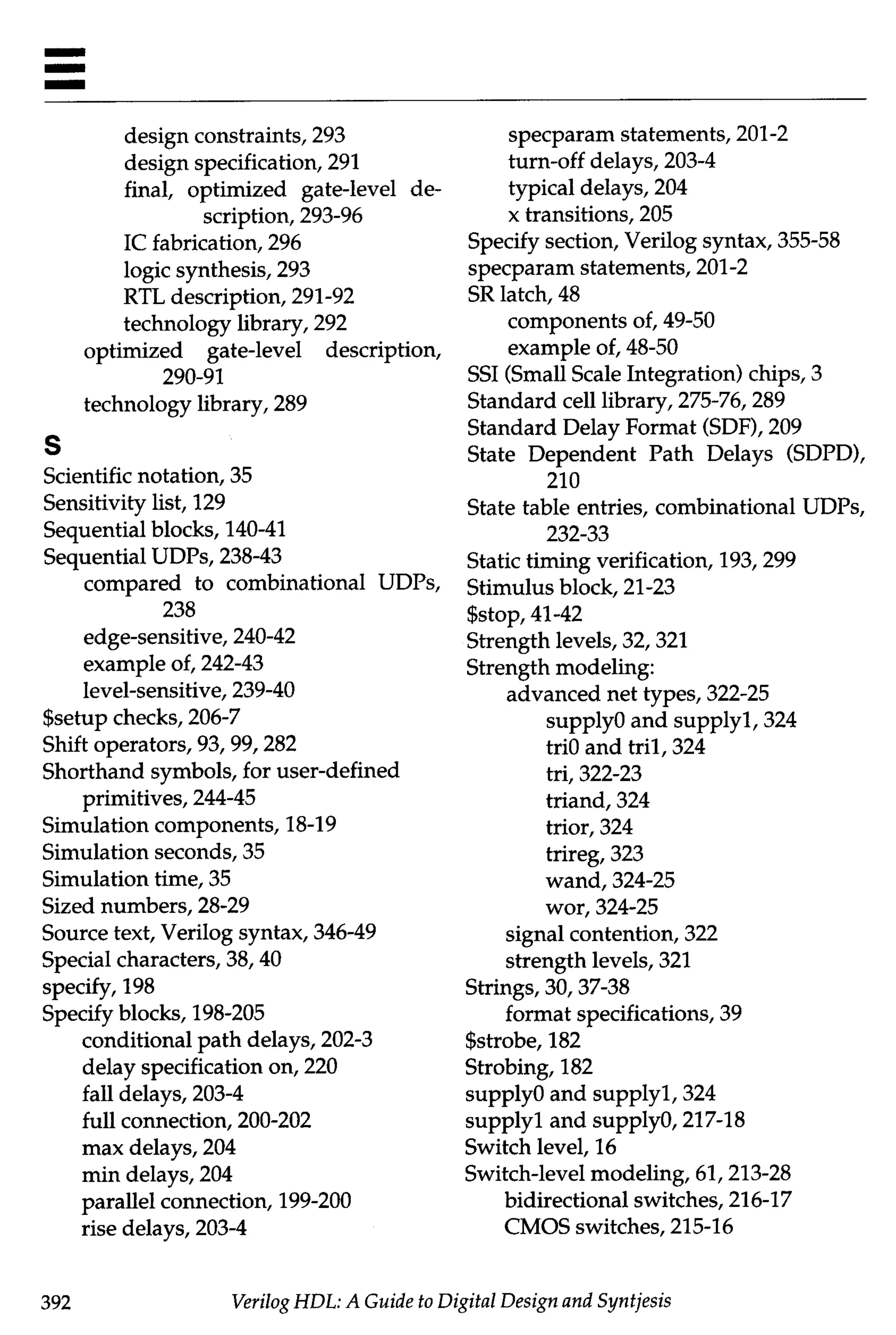

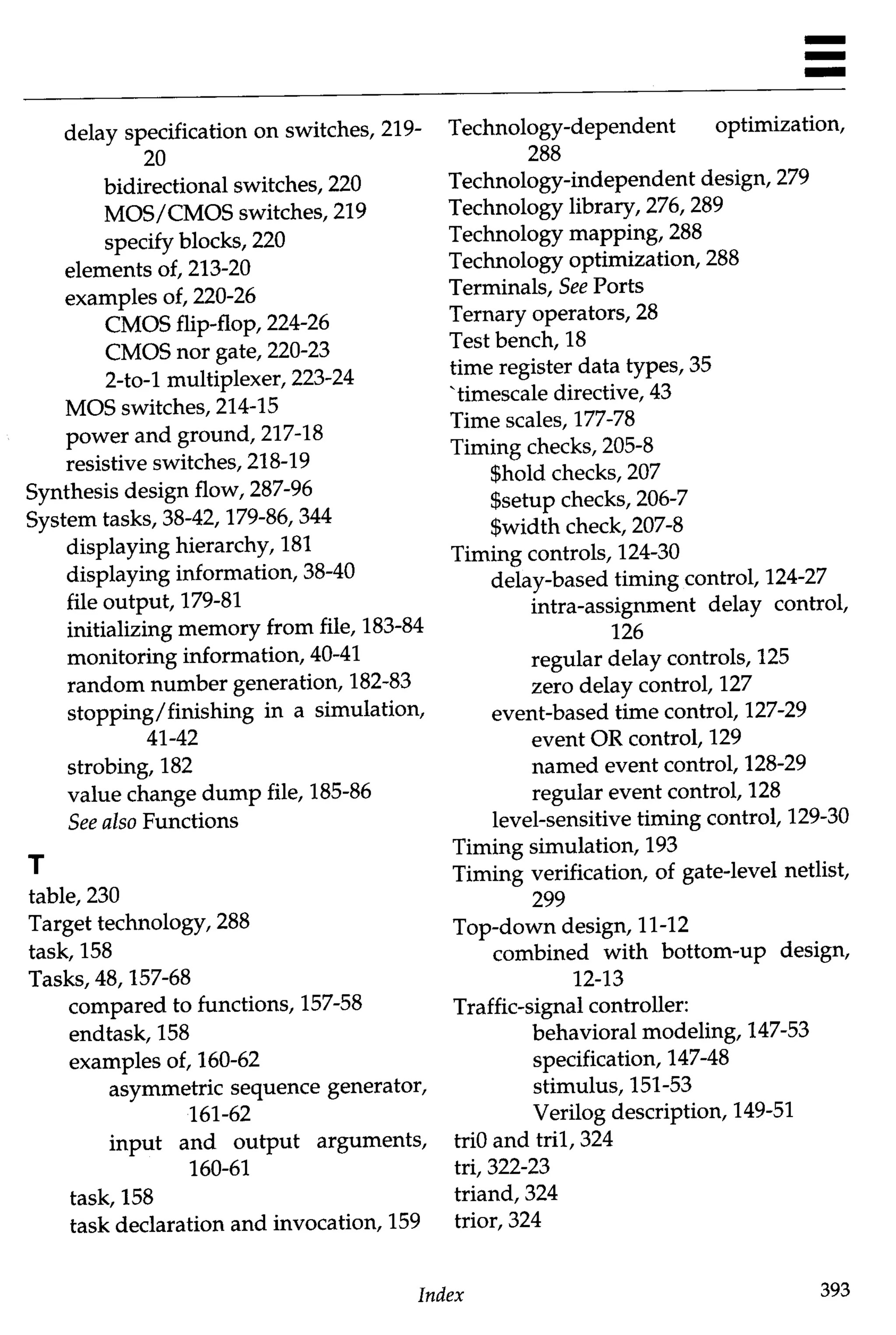

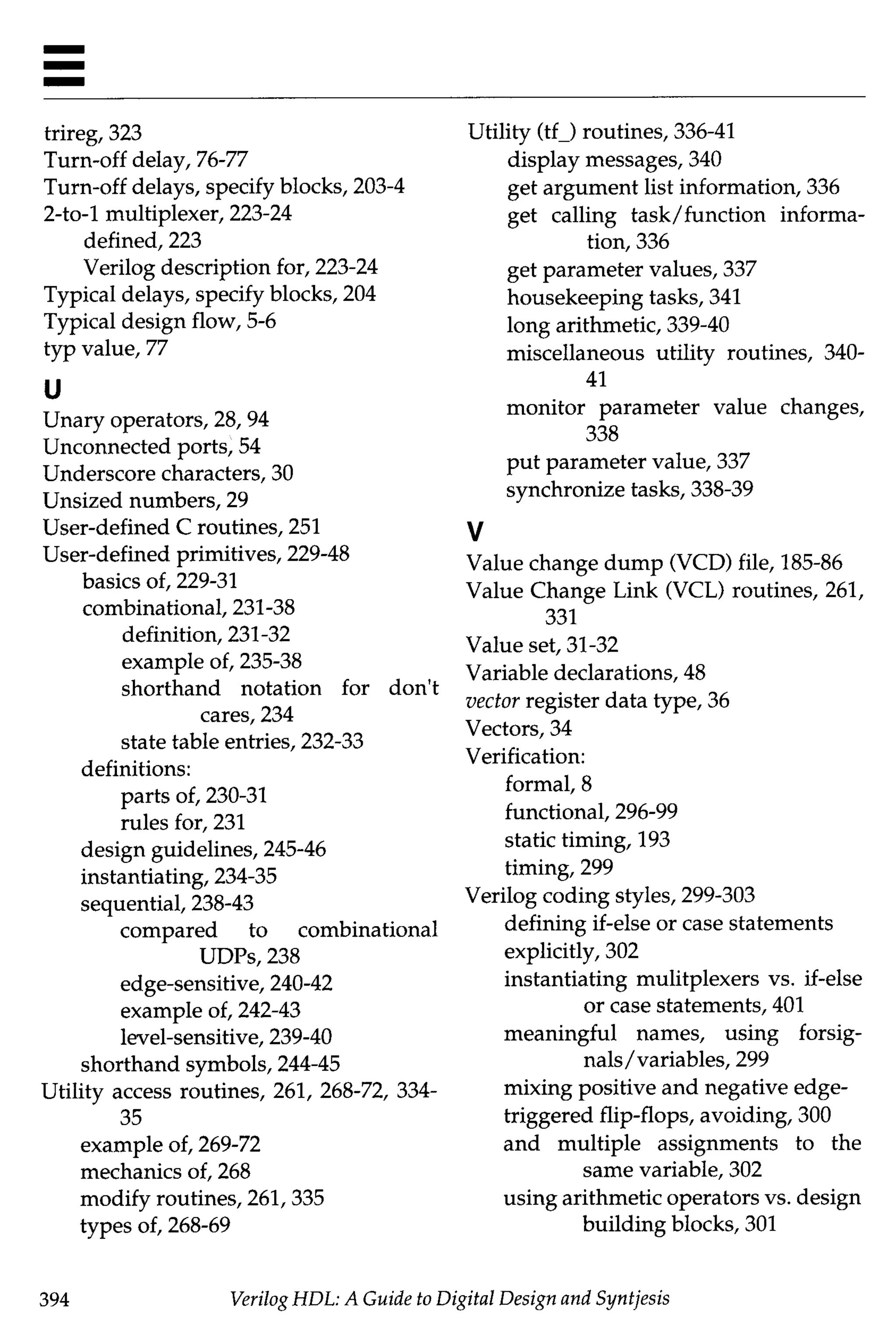

This document is a guide to digital design and synthesis using Verilog HDL. It is authored by Samir Palnitkar and published by SunSoft Press in 1996. The document covers basic and advanced topics of Verilog HDL over three parts, including modeling concepts, modules, behavioral modeling, timing, and logic synthesis. It also includes appendices with additional reference material.