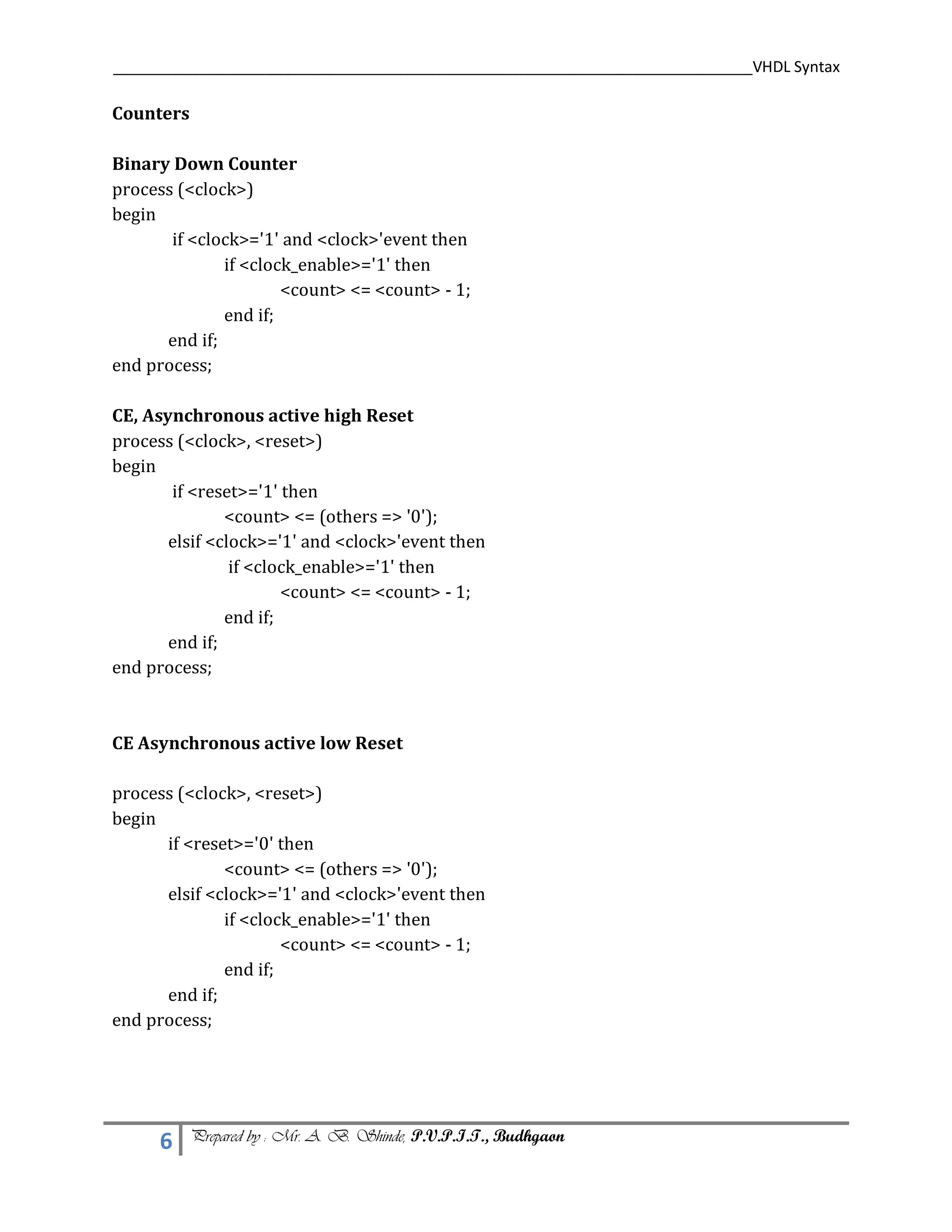

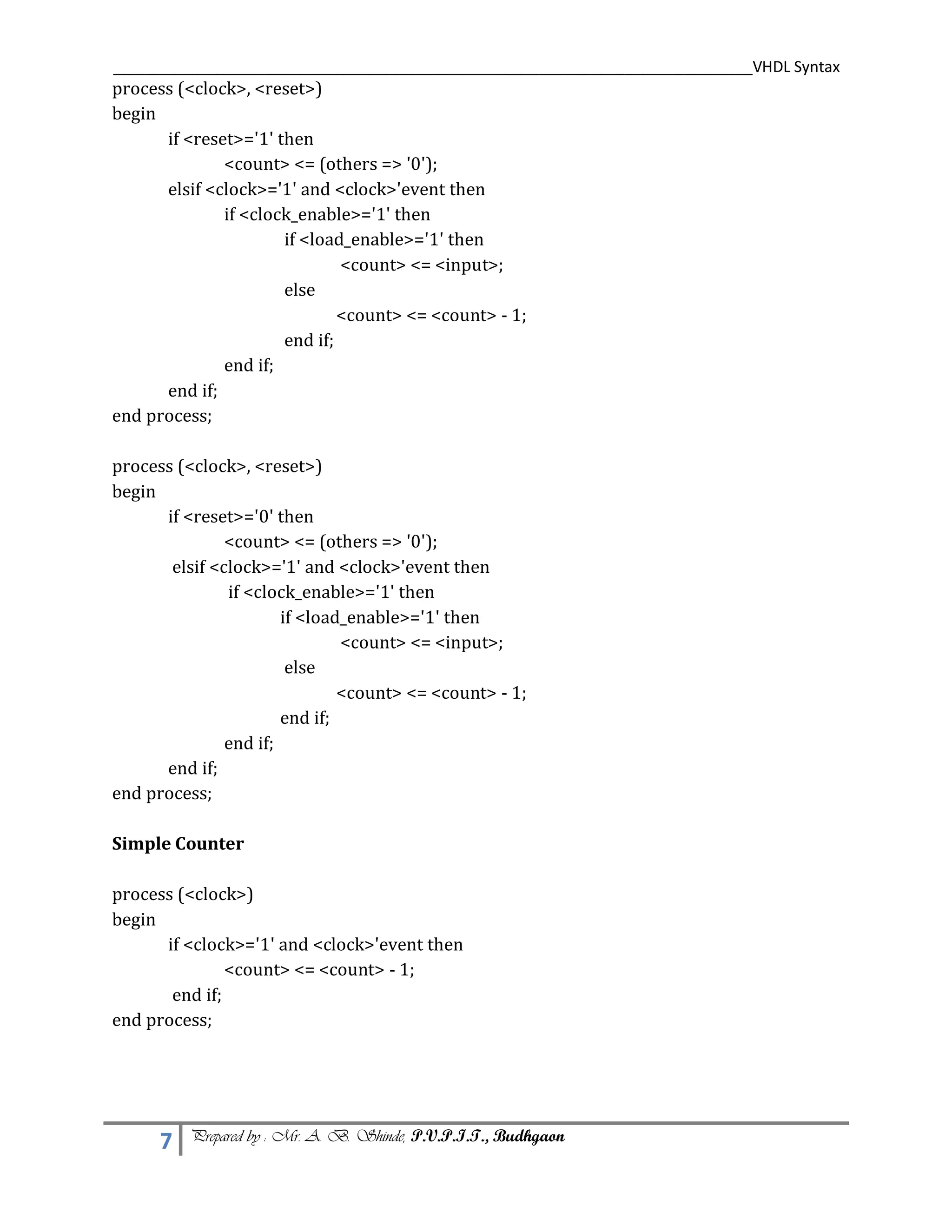

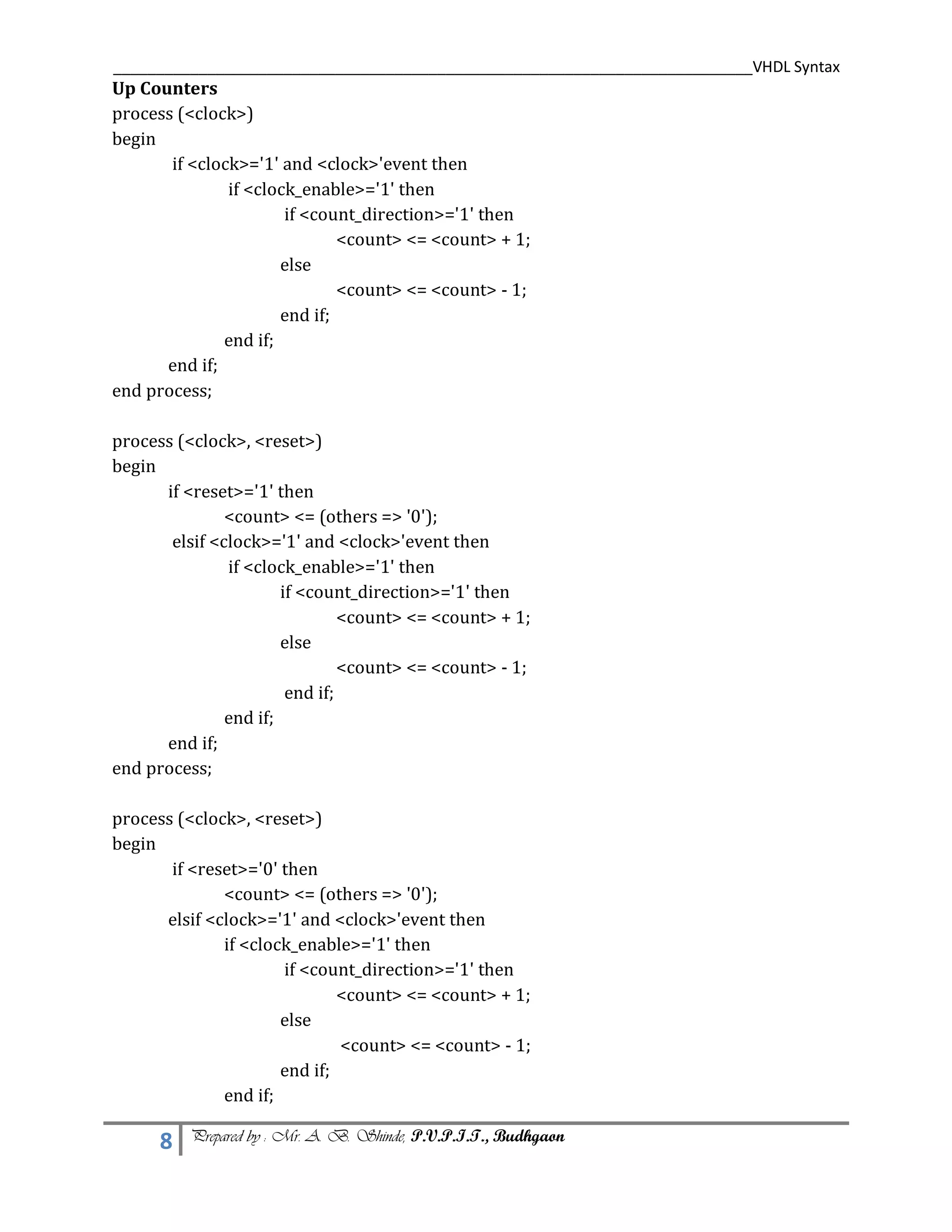

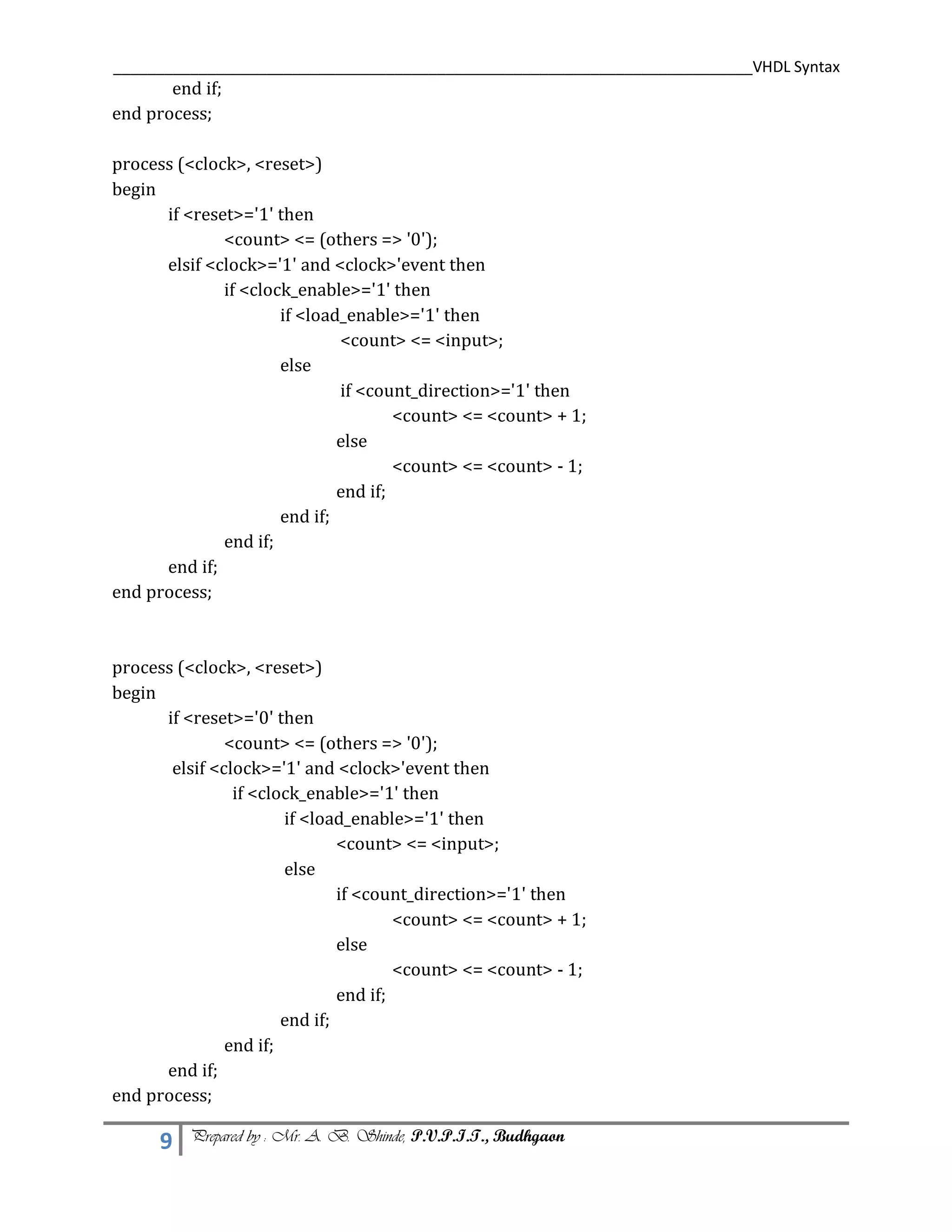

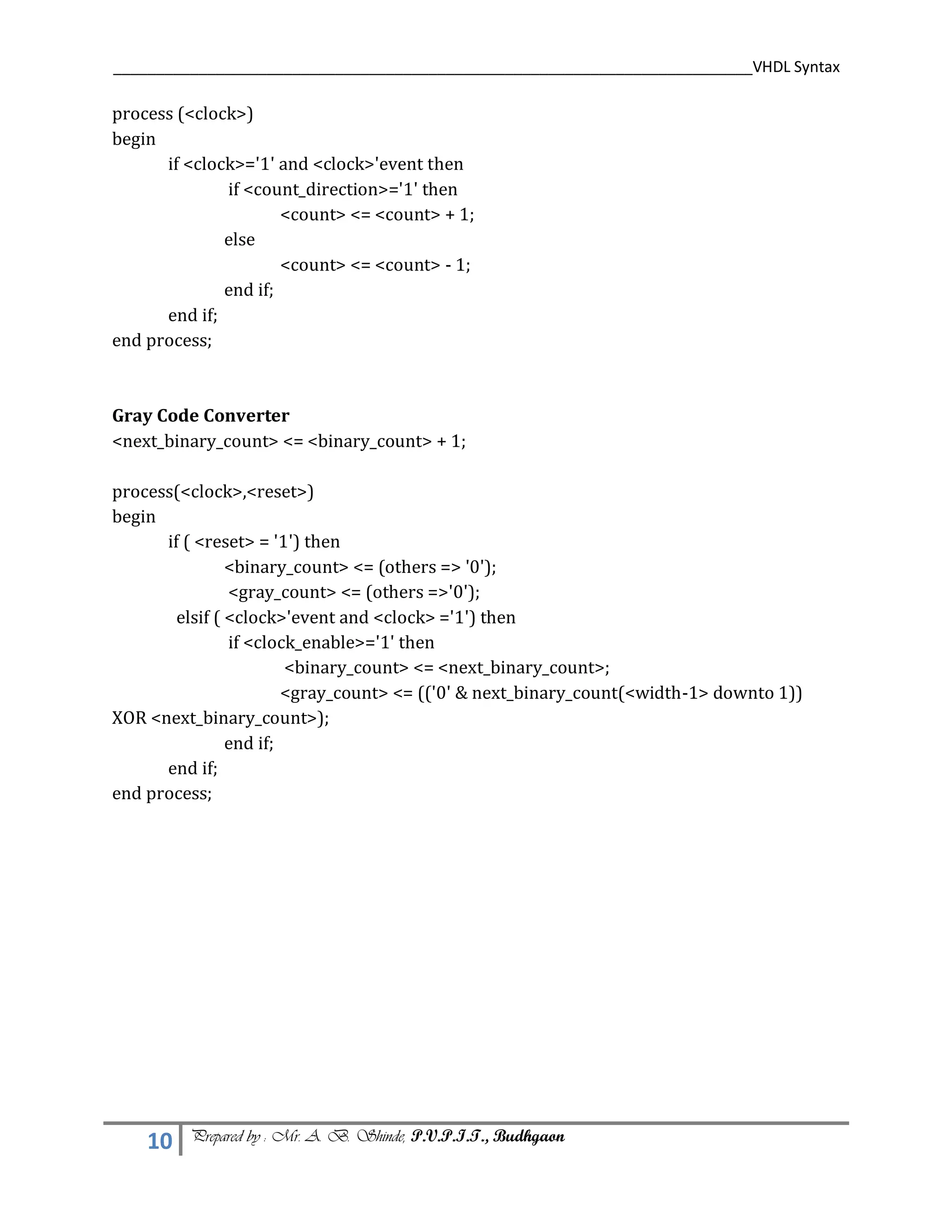

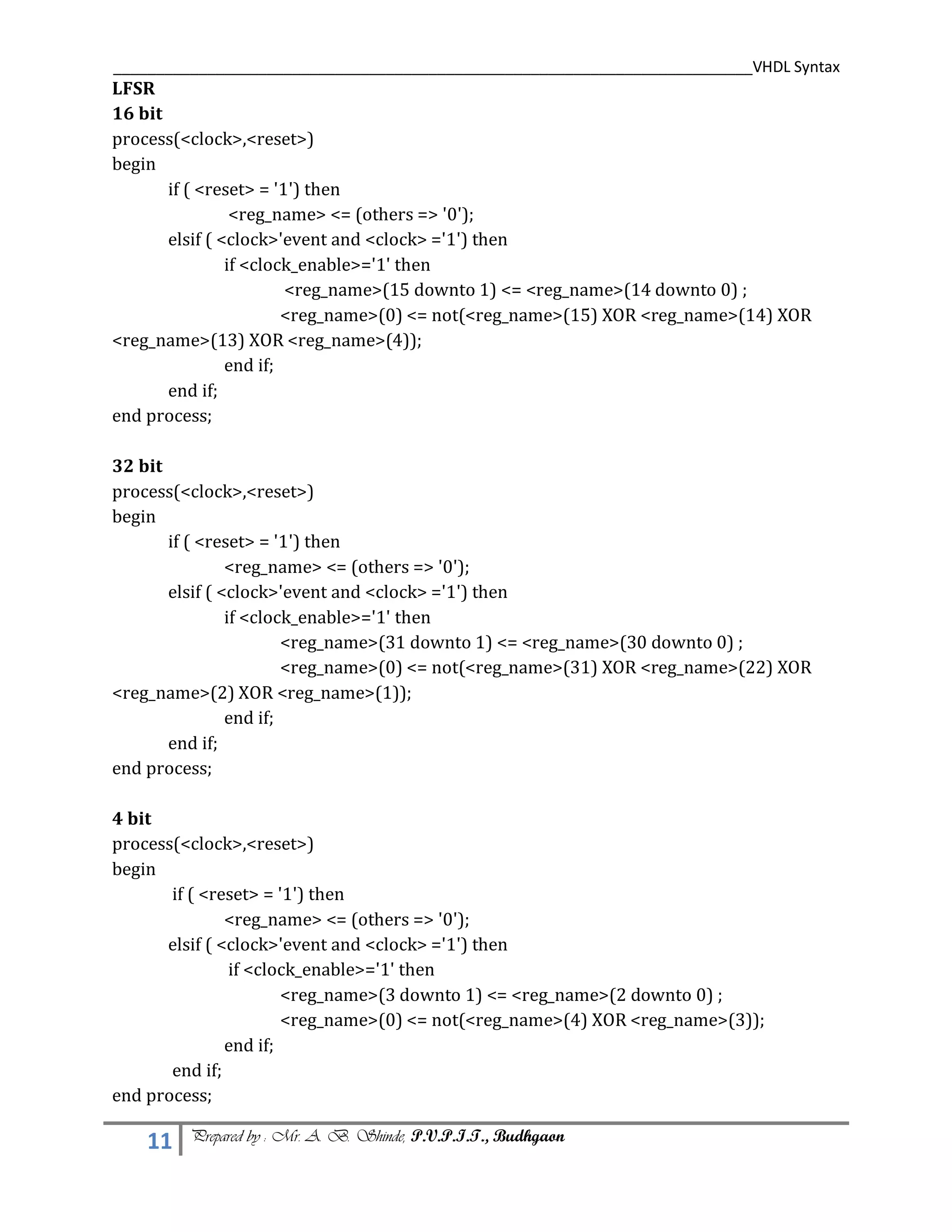

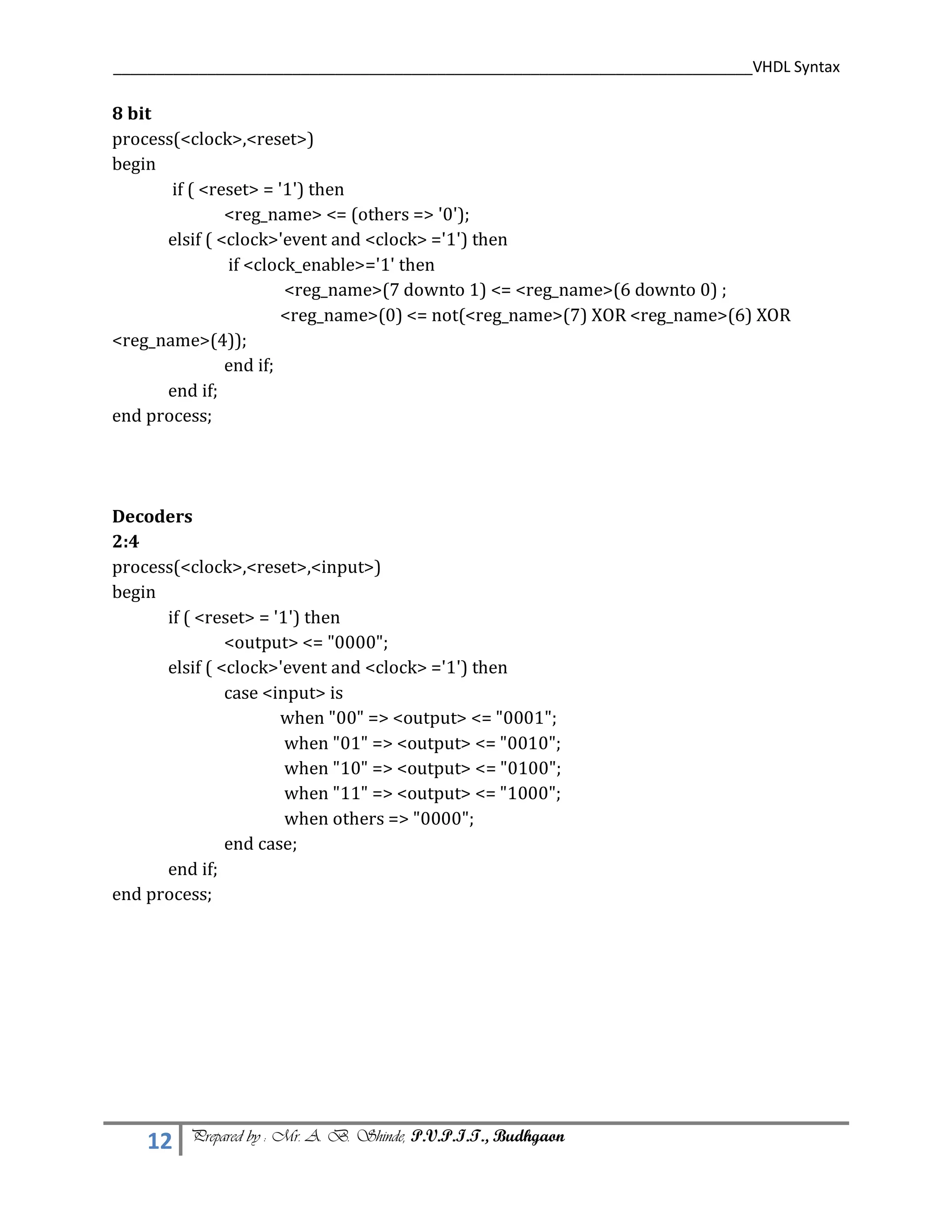

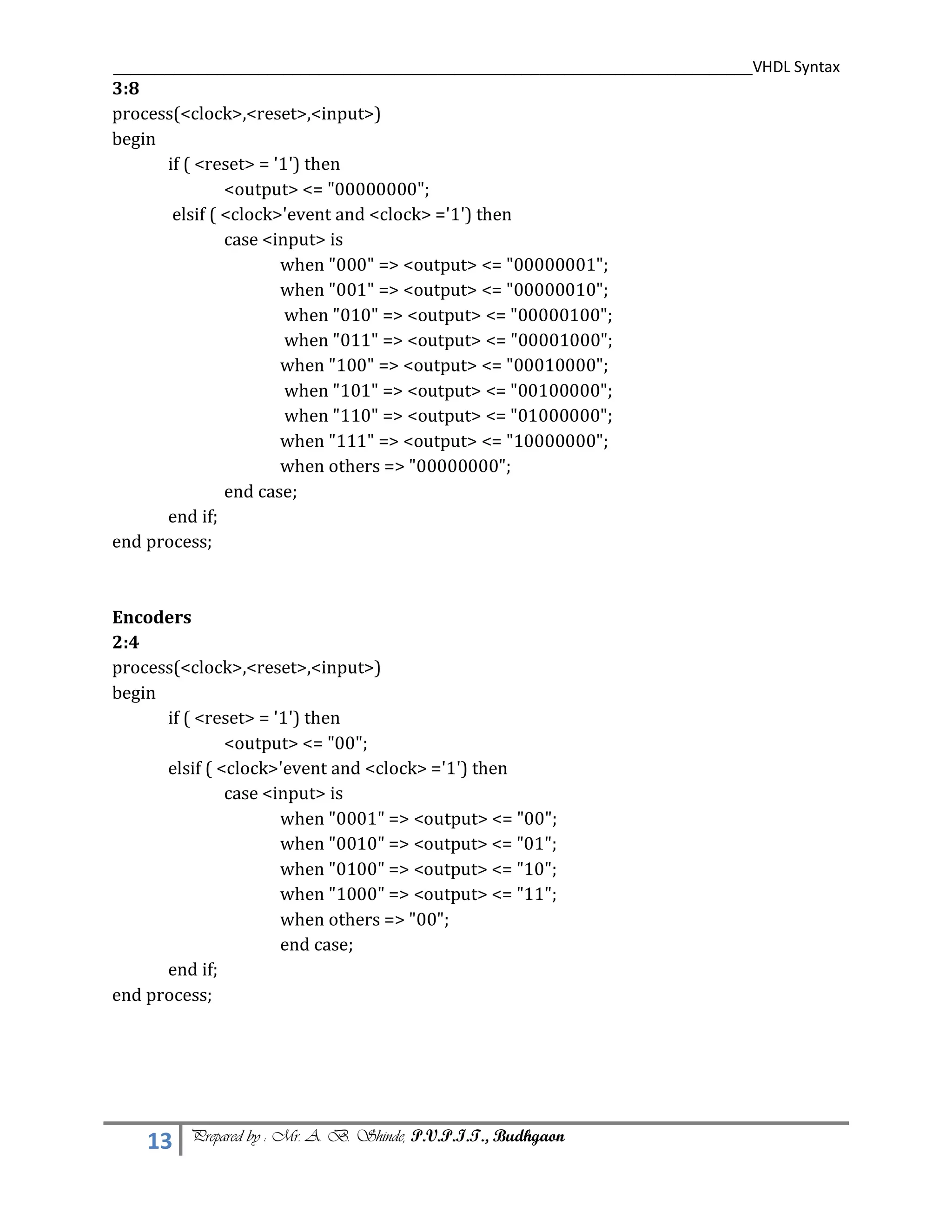

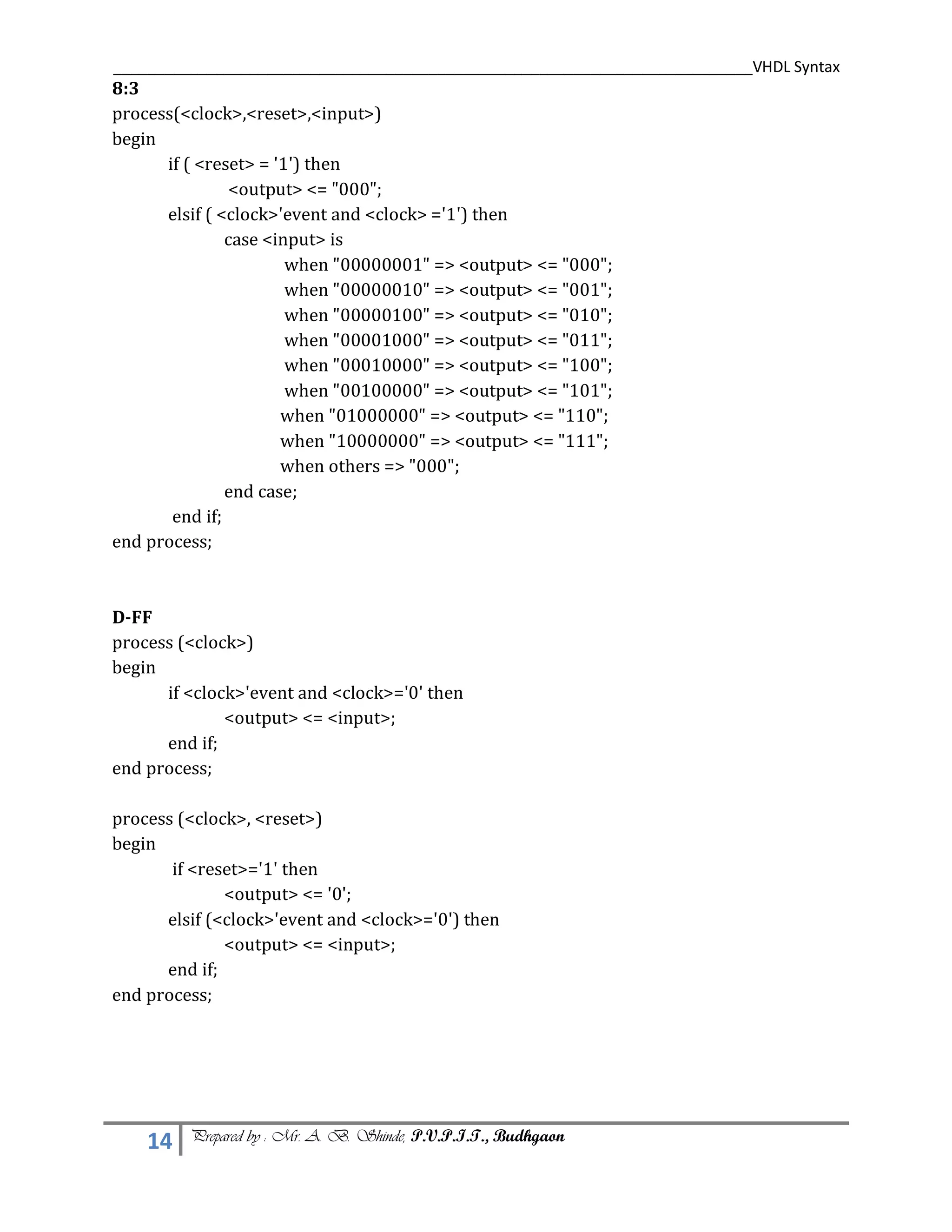

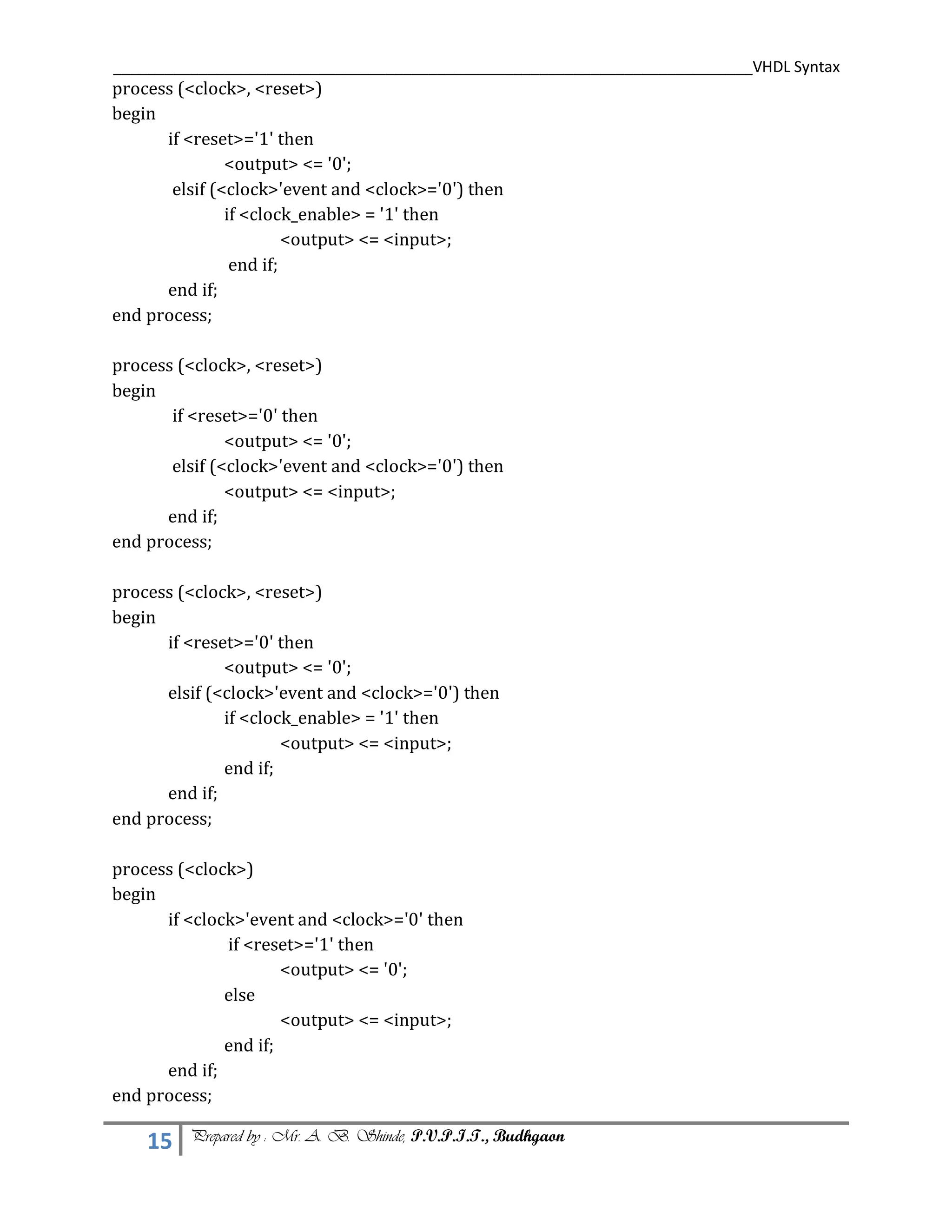

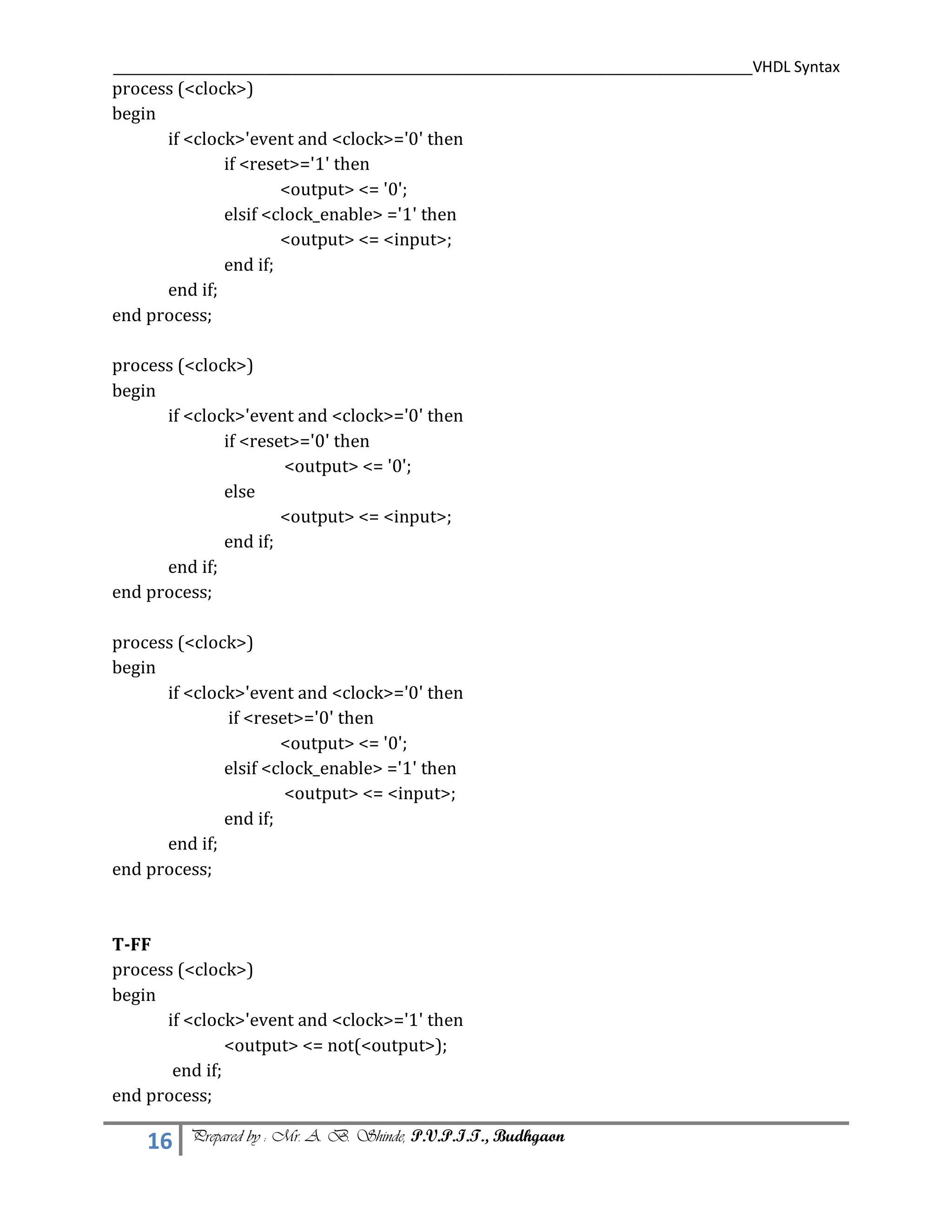

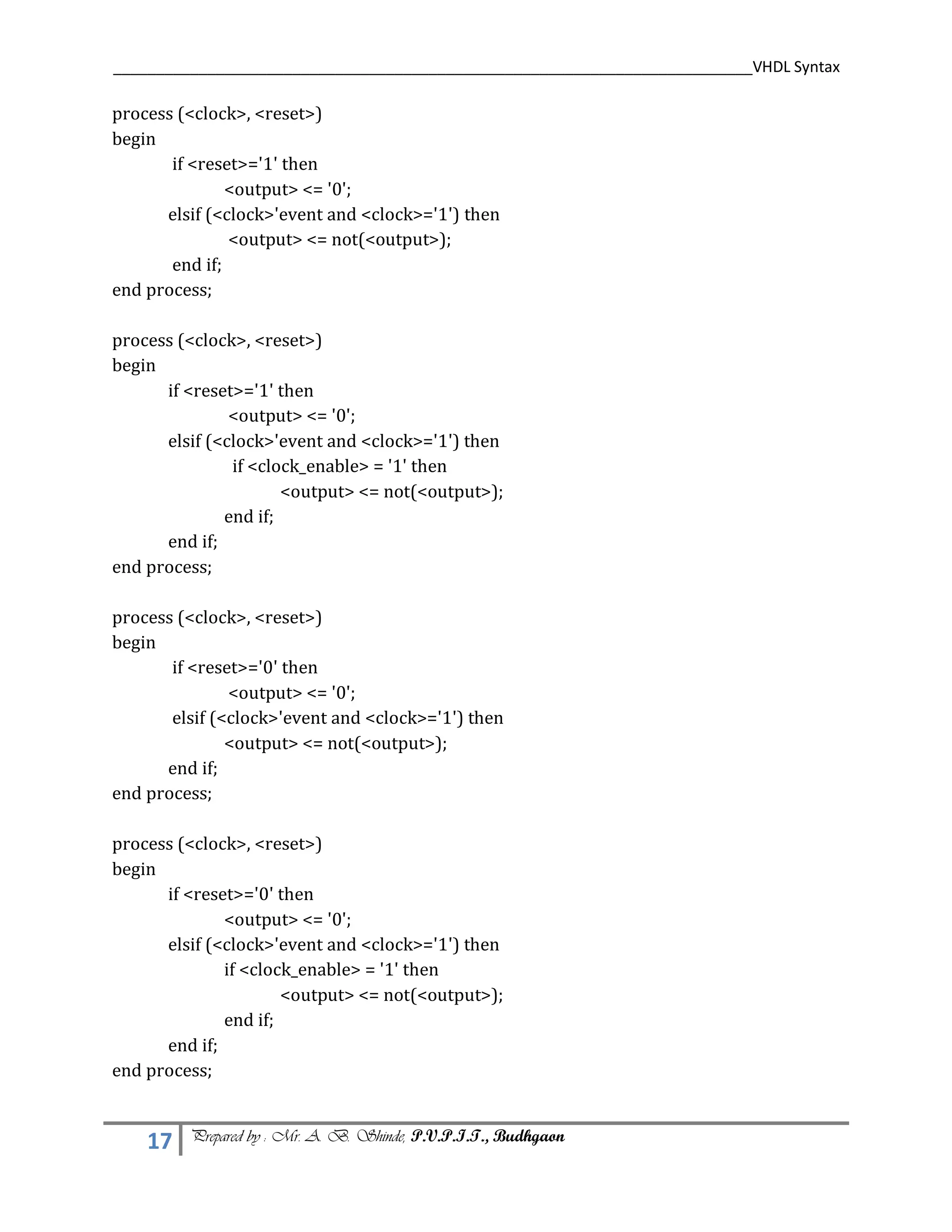

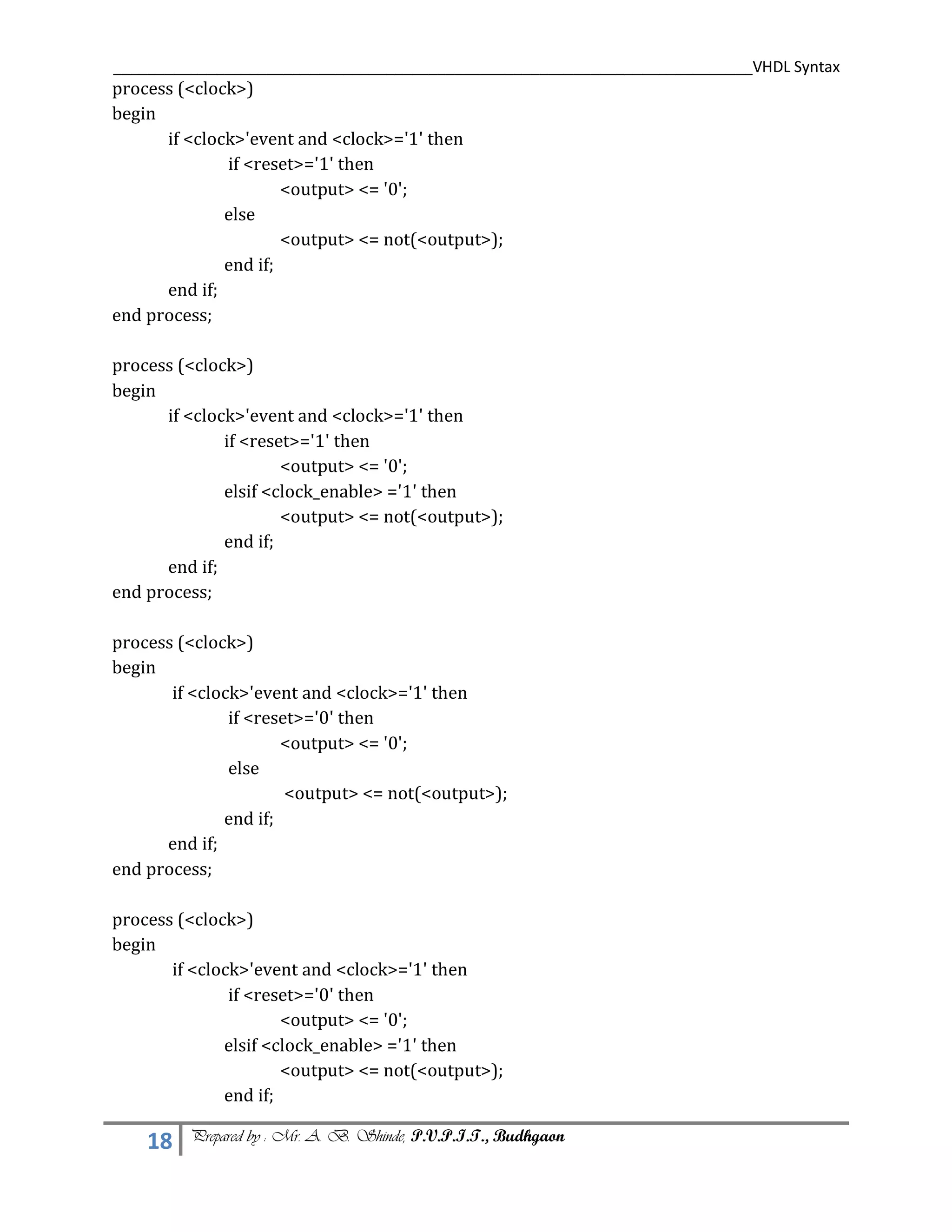

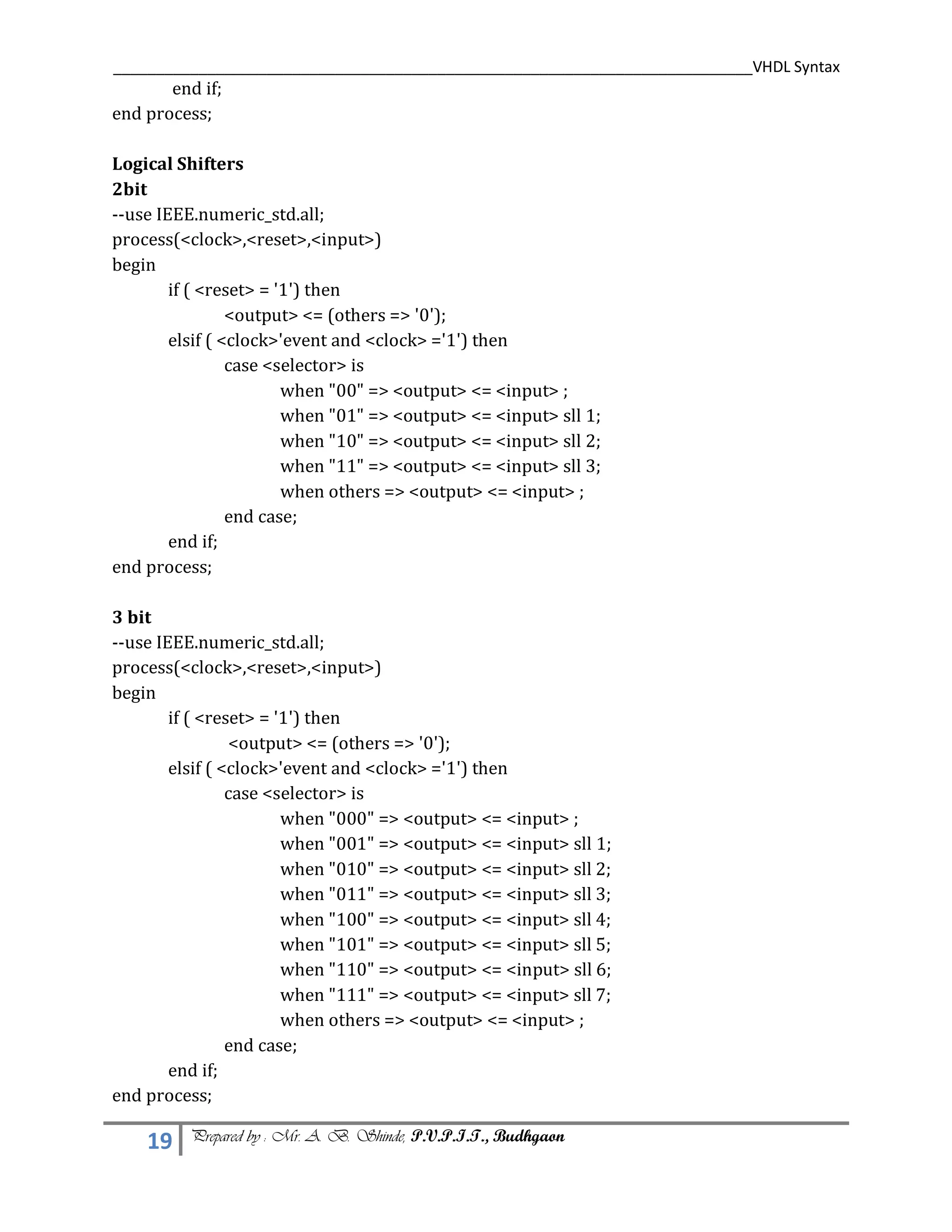

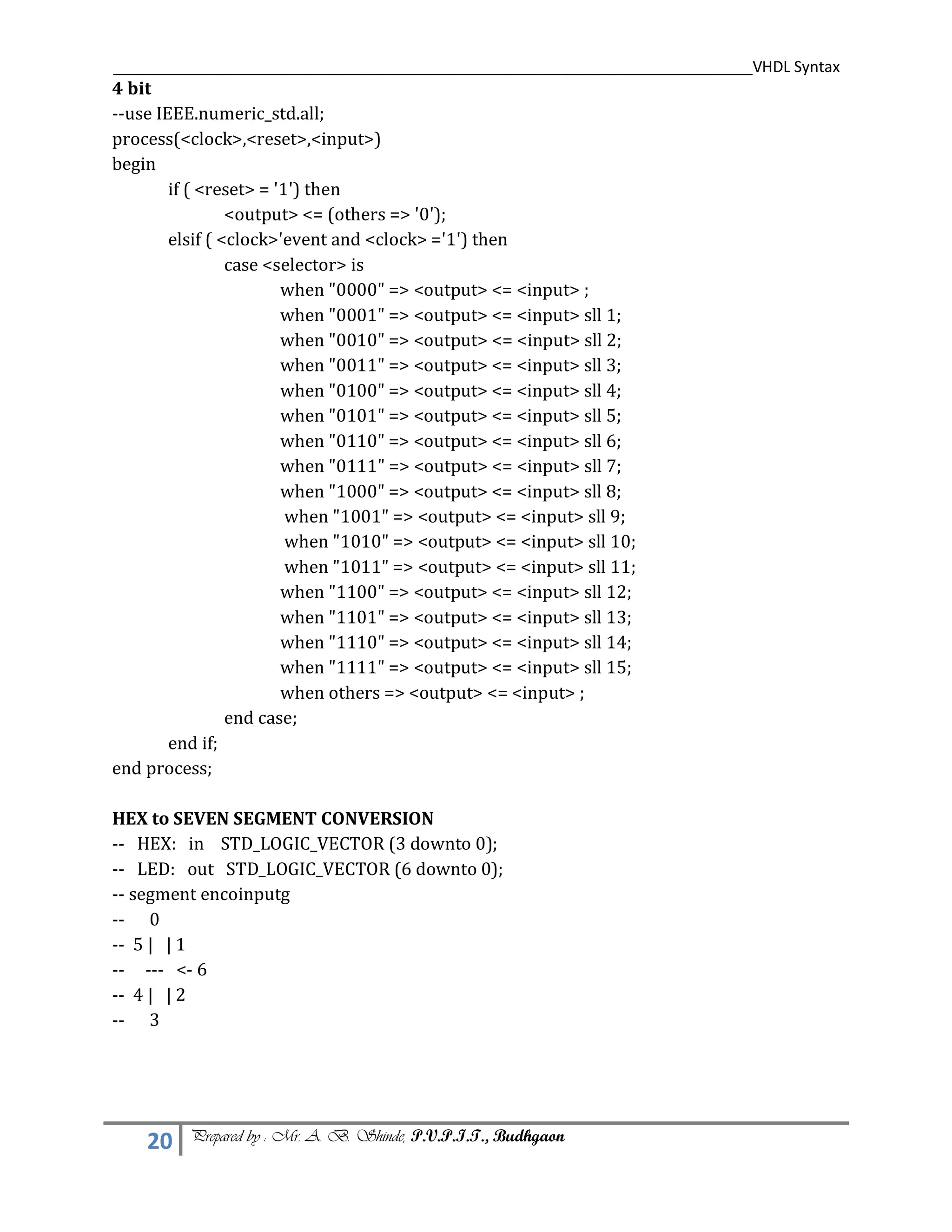

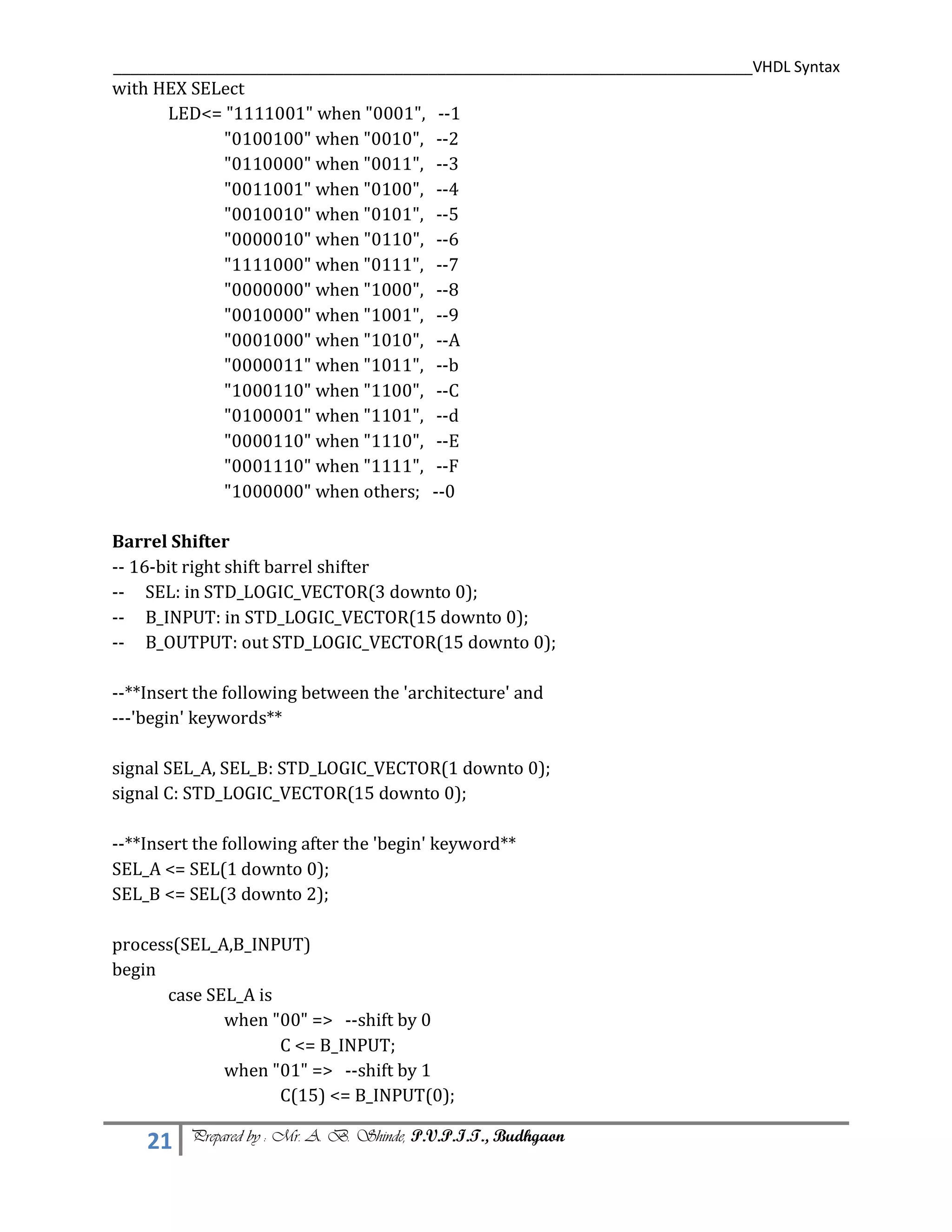

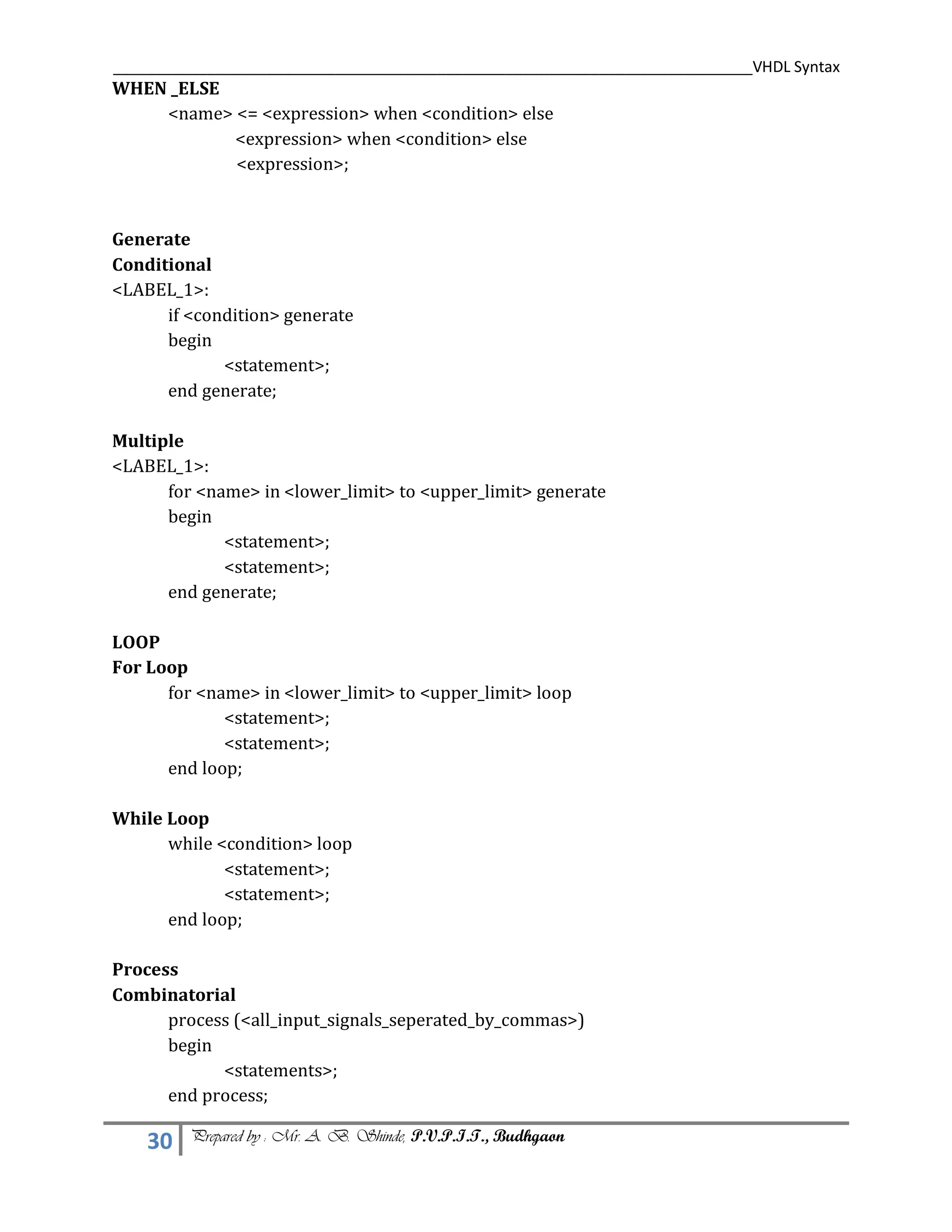

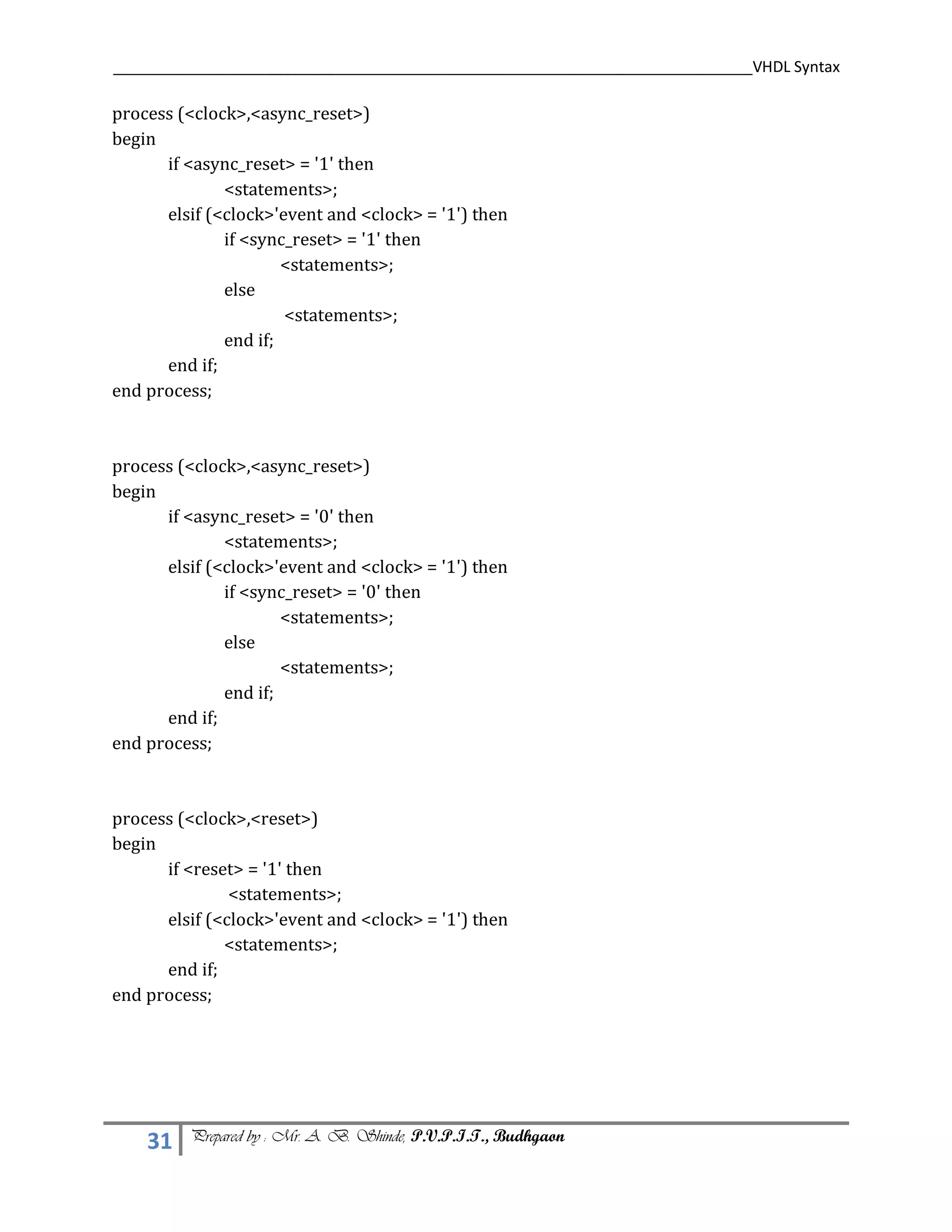

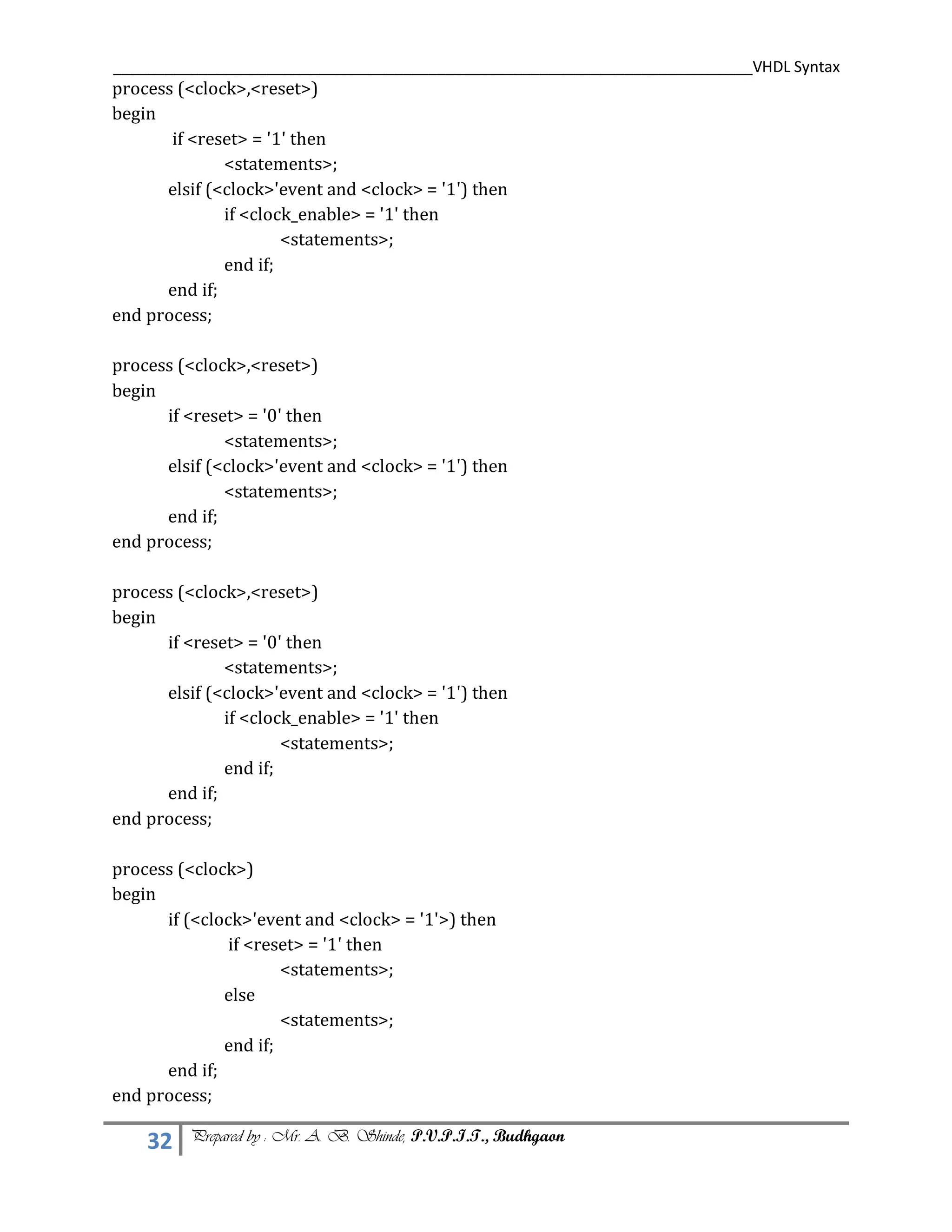

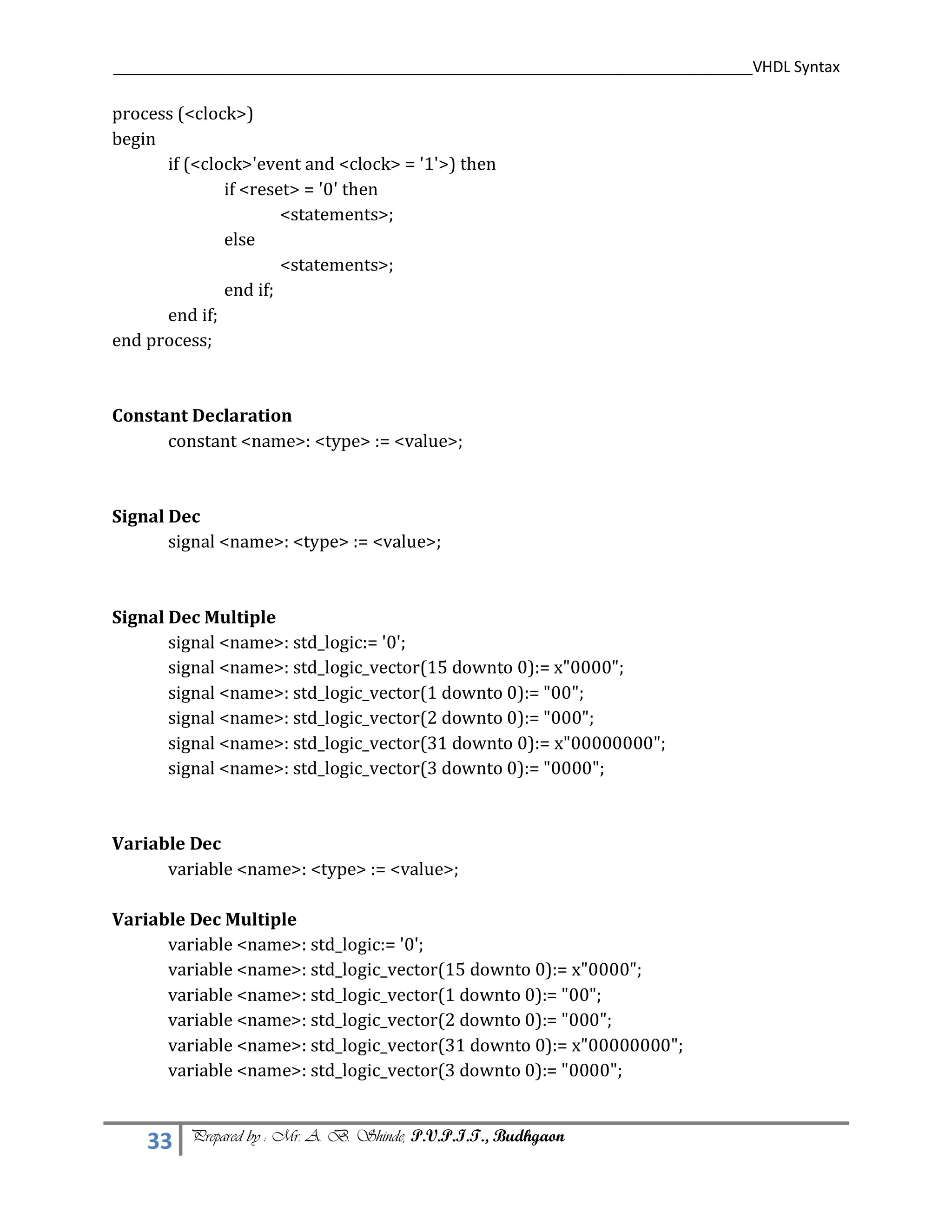

This document contains VHDL code examples for common digital logic components such as adders, comparators, counters, decoders, and linear feedback shift registers (LFSRs). It provides the VHDL syntax for implementing these components using processes, if/else statements, and case statements. The document is intended as a reference for a digital systems design lab manual. It was prepared by an instructor at Padmabhooshan Vasantraodada Patil Institute of Technology.