CS/ECE/EEE/INSTR F241 MICROPROCESSOR

PROGRAMMING & INTERFACING

MODULE 7: MEMORY INTERFACING

QUESTIONS

ANUPAMA KR

BITS, PILANI KK BIRLA GOA CAMPUS

�Q1.

An 8086 based system has the following memory requirements:

256K of ROM from 00000H

256K of ROM from C0000H

256K of RAM from 60000H.

Chips available:

64K ROM -8, 64K RAM -4, LS138-2. Design the memory Interfacing circuit.

Q2.

For an 80286 processor that has 16 MB of memory of which 4M is ROM and the rest is RAM. Half

of the ROM - mapped to address space starting at 00 00 00H Half to address space starting from

E0 00 00H. The RAM is mapped continuously from address 20 00 00H. Design the memory

Interfacing circuit.

Q3.

For an 8086 based system with the following memory requirements:

SRAM: 16KB from

ROM: 16 KB from

02000H

09000H

The following chips are available

SRAM- 2K x 8bit

74138 decoders (4 numbers)

ROM- 2K x 8bit

Using these decoders and minimum number of logic gates draw the memory interfacing diagram

Q4.

An 8086 system has the following memory requirements:

384K of ROM from 00000H

384K of ROM from A0000H

256K of RAM from 60000H

The following chips are available

32K ROM -24

32K RAM - 8

LS138 -4

Design the memory Interfacing circuit.

�Q5. Design an 80286 based system that has the following memory requirements:

1 M of ROM from 000000H

1 M of ROM from 800000H

1 M of ROM from F00000H

7 M of RAM from 100000H

3 M of RAM from 900000H

Chips available:

512K ROM chip

6 nos.

512K RAM chip

20 nos.

LS138

4 nos.

Show the complete memory mapping and design the memory decoding circuit using only the

chips given. All system bus signals (MEMR, MEMW, IOR, IOW BHE, A0- A23, D0 D16) are

available. Show the memory interfacing circuit. Use absolute addressing.

Q6.

A System is built around the 8086 processor which is working at a frequency of 5 MHz. It has 640

KB of memory of which 256 K is ROM and the rest is RAM Half of the ROM is mapped to address

space starting at 0 00 00H and half it to address space starting from E 00 00H The RAM 128 K is

mapped from 4 00 00H and the rest from address 8 00 00H.

Show the complete memory mapping and design the memory interfacing circuit using only the

chips given in table below. All system bus signals (MEMR, MEMW, IOR, IOW, BHE, A0- A19, D0

D15) are available. Use Absolute Addressing.

Chips Available

64 K ROM

64 K RAM

LS138

Q7.

Nos.

4

6

2

80286-based system has the following memory requirements

576KB of memory

128KB

ROM

rest

RAM

The mapping is as follows

64 K ROM

000000H

64 K ROM

0F0000H

RAM

040000H

System is expandable in nature.

Chips available:

27256

4 nos.

61256

14 nos.

Inverter

1

LS138

4 nos

4-input OR gates

1

Design the memory interfacing circuit.

�Q8.

For an 80386 system with the following memory requirements - 1 M SRAM 04 00 00 00H

The SRAM chip available is MS621000 128 K x 8. The memory interfacing has to be done using

GAL22V10C. (Refer to corresponding video for details of GAL22V10C)

1.

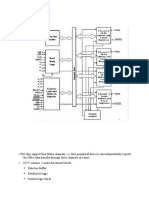

Q9. The decoding logic (using absolute addressing) for an 8086 processor is shown below. This is

the only decoding circuit in the computing system and the rest of the address lines are used with the

memory chips. (Pin out of this decoder is same as the one given in Lecture 1 of Module 7)

A17

O0

ROM1E

CS

A17

O0

ROM1O

CS

A16

O1

ROM2E

CS

A16

O1

ROM2O

CS

A15

O2

ROM3E

CS

A15

O2

ROM3O

CS

LS 138

O3

RAM1E

CS

LS 138

O3

RAM1O

CS

A19

G1

O4

RAM2E

CS

A19

G1

O4

RAM2O

CS

A18

G2A

O5

RAM3E

CS

A18

G2A

O5

RAM3O

CS

A0

G2B

O6

RAM4E

CS

BHE

G2B

O6

RAM4O

CS

O7

RAM5E

CS

O7

RAM5O

CS

Answer the following questions

How much memory does the system have? How much of this memory is RAM? What is the

size of the RAM and ROM Chips used? What is the memory map?

Memory

Chips

Address [Starting AddressEnding Address]

Memory

Chips

ROM1

RAM2

ROM2

RAM3

ROM3

RAM4

RAM1

RAM5

Address [Starting AddressEnding Address]