0% found this document useful (0 votes)

278 views17 pages8051 Architecture

The 8051 architecture was developed by Intel in the 1980s using NMOS and later CMOS technology. It has 128 bytes of RAM, 4K bytes of ROM, two timers, serial port, and four 8-bit I/O ports. The CPU contains an ALU and CU to control operations. Program memory stores instructions, data memory stores variables, and I/O ports connect to external devices. A crystal oscillator provides the clock signal. Newer variants include larger memory, USB, encryption, ADCs, and wireless modules.

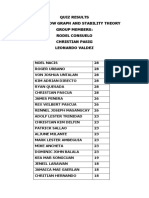

Uploaded by

Leonard ValdezCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

278 views17 pages8051 Architecture

The 8051 architecture was developed by Intel in the 1980s using NMOS and later CMOS technology. It has 128 bytes of RAM, 4K bytes of ROM, two timers, serial port, and four 8-bit I/O ports. The CPU contains an ALU and CU to control operations. Program memory stores instructions, data memory stores variables, and I/O ports connect to external devices. A crystal oscillator provides the clock signal. Newer variants include larger memory, USB, encryption, ADCs, and wireless modules.

Uploaded by

Leonard ValdezCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 17